用来进行芯片内部的除错控制的设备以及方法与流程

- 国知局

- 2024-07-31 20:12:02

本发明是关于系统除错,尤指一种用来进行一芯片内部的除错控制的设备以及方法。

背景技术:

1、为了进行系统除错,芯片除了功能模式(function mode)外还可利用具备扫描模式(scan mode)的扫描链(scan chain),在芯片运作到某个状态时能将芯片中的信息倒出以进行进一步的分析及除错。然而,相关技术需要在功能模式执行一定的频率周期后就切换到扫描模式,因为扫描链长度很长,所以需要多个频率周期才能完整地取得芯片内的瞬时数据。尤其当系统回报错误时,相关技术典型地需要反复地在功能模式与扫描模式之间切换,才得以将与芯片的运作错误对应的瞬时数据取出以供后续分析之用,因此会耗费大量的时间成本。另外,芯片上的硬件错误并不一定是固定型故障(stuck-at fault),因此利用相关技术的方法所撷取出的瞬时数据的值与实际执行程序的情况下所得到的值可能不同,导致除错方向错误。

2、为了解决上述问题,可增加追踪缓冲器(trace buffer)或是在小功能单元中增加校验码(check code)解决上述问题。然而,增加追踪缓冲器会大幅地增加额外硬件成本,因此难以被普及,而增加校验码的方式则无法让除错程序进行细部的定位。

3、因此,需要一种新颖的除错设备以及相关方法,以在没有副作用或较不会带来副作用的情况下提升除错程序的效率。

技术实现思路

1、本发明的目的在于提供一种用来进行一芯片内部的除错控制的设备以及方法,使得该芯片的执行精确地被暂停在指定的或想要的位置,以提升除错程序的效率。

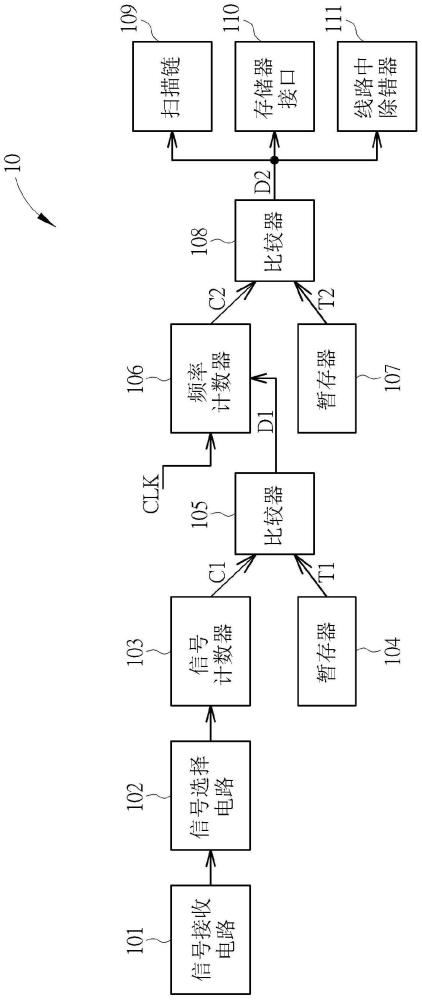

2、本发明至少一实施例提供一种用来进行一芯片内部的除错控制的设备。该设备包括一第一计数器、一第一判断电路、一第二计数器以及一第二判断电路,其中该第一判断电路耦接至该第一计数器,该第二计数器耦接至该第一判断电路,以及该第二判断电路耦接至该第二计数器。该第一计数器是用来对该芯片中的一特定系统请求被执行的次数进行计数,以产生一第一计数结果。该第一判断电路是用来判断该第一计数结果是否达到一第一阈值,以产生一第一判断结果。该第二计数器是用来对一执行频率的一周期数进行计数,以产生一第二计数结果。该第二判断电路是用来判断该第二计数结果是否达到一第二阈值,以产生一第二判断结果。另外,当该第一判断结果指出该第一计数结果达到该第一阈值且该第二判断结果指出该第二计数结果达到该第二阈值时,该芯片的执行被暂停在一断点状态。

3、本发明至少一实施例提供一种用来进行一芯片内部的除错控制的方法。该方法包括:利用一第一计数器对该芯片内部中的一特定系统请求被执行的次数进行计数,以产生一第一计数结果;利用一第一判断电路判断该第一计数结果是否达到一第一阈值,以产生一第一判断结果;利用一第二计数器对一执行频率的一周期数进行计数,以产生一第二计数结果;利用一第二判断电路判断该第二计数结果是否达到一第二阈值,以产生一第二判断结果;以及因应该第一判断结果指出该第一计数结果达到该第一阈值且该第二判断结果指出该第二计数结果达到该第二阈值,将该芯片的执行暂停在一断点状态。

4、本发明的实施例提供的设备以及方法能通过第一阈值以及第二阈值的设定,使得芯片内部的执行能被暂停在指定的位置。例如,芯片的目标暂停位置能通过特定系统请求的执行次数以及该特定系统请求执行的频率周期数来定义。相较于相关技术,本发明能更快速地让芯片内部的执行被暂停在指定的断点(例如与芯片所回报的错误对应的执行断点),以利于取得与芯片回报的错误相关的瞬时数据。

技术特征:1.一种用来进行芯片内部的除错控制的设备,其特征在于,包括:

2.如权利要求1所述的设备,其特征在于,该设备还包括:

3.如权利要求2所述的设备,其特征在于,当该设备接收到错误信息时,该第一计数器依据该错误信息被配置为对接收到该特定信号的次数进行计数,以对该特定系统请求被执行的次数进行计数。

4.如权利要求1所述的设备,其特征在于,当该第一判断结果指出该第一计数结果达到该第一阈值时,该第二计数器开始对该执行频率的该周期数进行计数,以产生该第二计数结果。

5.如权利要求1所述的设备,其特征在于,该第一阈值是依据该第一计数器在该设备在先前该芯片执行的期间接收到错误信息时产生的先前的第一计数结果来决定,以及该第二阈值是依据该第二计数器在该设备在先前该芯片执行的期间接收到该错误信息时产生的先前的第二计数结果来决定,以将该芯片的执行在该设备接收到该错误信息时的状态设为该断点状态。

6.如权利要求1所述的设备,其特征在于,该第一阈值是依据该第一计数器在该设备在先前该芯片执行的期间接收到错误信息时产生的先前的第一计数结果来决定,以及该第二阈值被依序设为多个候选阈值以使得该芯片的执行依序被暂停在多个候选断点状态,其中该多个候选阈值的其中一者依据该多个候选断点状态被选择作为该第二阈值,以使得该断点状态对应于该设备在先前该芯片执行的期间接收到的该错误信息。

7.如权利要求1所述的设备,其特征在于,当该第一判断结果指出该第一计数结果达到该第一阈值且该第二判断结果指出该第二计数结果达到该第二阈值时,串接多个触发器的扫描链被触发以将该多个触发器在该断点状态下的值输出。

8.如权利要求1所述的设备,其特征在于,当该第一判断结果指出该第一计数结果达到该第一阈值且该第二判断结果指出该第二计数结果达到该第二阈值时,耦接至存储装置的存储器接口被触发以撷取该存储装置在该断点状态下存储的数据。

9.如权利要求1所述的设备,其特征在于,当该第一判断结果指出该第一计数结果达到该第一阈值且该第二判断结果指出该第二计数结果达到该第二阈值时,线路中除错器被触发以撷取该设备在该断点状态下的信息。

10.一种用来进行芯片内部的除错控制的方法,其特征在于,包括:

技术总结本发明提供一种用来进行一芯片内部的除错控制的设备以及方法,其中该设备包括一第一计数器、一第一判断电路、一第二计数器以及一第二判断电路。该第一计数器对该芯片内部中的特定系统请求被执行的次数进行计数,以产生第一计数结果,并且该第一判断电路依据该第一计数结果产生第一判断结果。该第二计数器对执行频率的周期数进行计数,以产生第二计数结果,并且该第二判断电路依据该第二计数结果产生第二判断结果。当该第一判断结果指出该第一计数结果达到第一阈值且该第二判断结果指出该第二计数结果达到第二阈值时,该芯片的执行被暂停在一断点状态。技术研发人员:陈泳成,许廷硕受保护的技术使用者:瑞昱半导体股份有限公司技术研发日:技术公布日:2024/7/9本文地址:https://www.jishuxx.com/zhuanli/20240731/185412.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表