存储装置、电子设备和存储装置的控制方法

- 国知局

- 2024-07-31 20:14:24

本公开的实施例涉及一种存储装置、电子设备和存储装置的控制方法。

背景技术:

1、随着科学技术和经济的快速发展,存储器的应用范围越来越广。基本的存储器可以按照存储介质的特性分为易失性存储器和非易失性存储器。易失性存储器指断电之后存储的数据将丢失的存储器,相应地非易失性存储器则是指断电之后存储的数据不会丢失的存储器。通常,易失性存储器操作速度快,而非易失性存储器保存时间长。

2、sram(static random access memory,静态随机存储器)是易失性存储器,当电源断开的时候其内存储的数据会丢失,因此需要一直提供电源以维持sram存储器的编程状态,这种方法消耗较多能量,不利于存储装置的低功耗设计。

技术实现思路

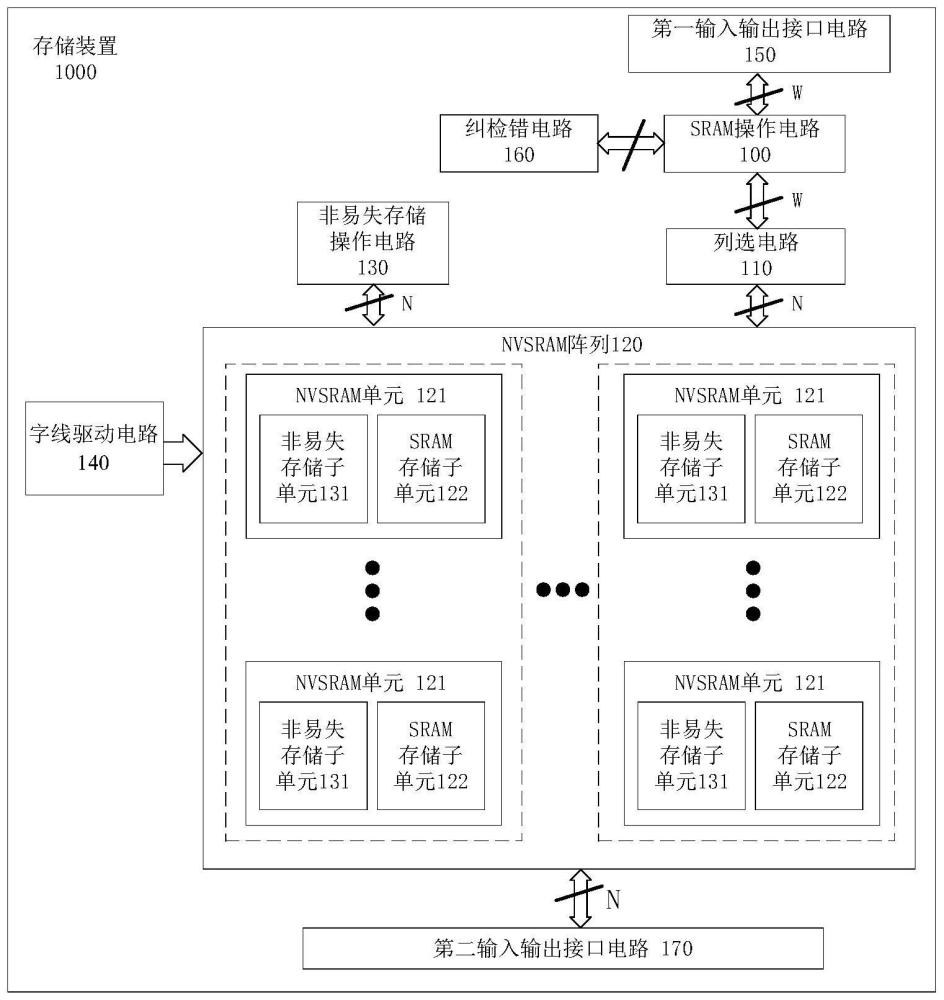

1、本公开至少一个实施例提供一种存储装置,包括:nvsram阵列、sram操作电路、非易失存储操作电路、纠检错电路、第一输入输出接口电路、列选电路、第二输入输出接口电路,其中,所述纠检错电路与所述sram操作电路耦接,所述sram操作电路与所述列选电路耦接,所述列选电路与所述nvsram阵列耦接,所述非易失存储操作电路与所述nvsram阵列耦接;所述nvsram阵列包括阵列排列的多个nvsram单元,且每个nvsram单元包括sram存储子单元和非易失存储子单元,所述非易失存储子单元被配置为对所述sram存储子单元存储的数据进行数据备份;所述非易失存储操作电路被配置为对所述nvsram阵列中被选择的nvsram单元中的sram存储子单元数据进行数据备份操作;所述sram操作电路被配置为对所述sram存储子单元数据进行第一数据读写操作;所述列选电路被配置为,对所述非易失存储子单元数据进行数据恢复操作;所述列选电路还被配置为,在进行所述数据恢复操作或在所述sram操作电路进行所述第一数据读写操作的情况下,选择所述nvsram阵列中需要被操作的对象单元列;所述第一输入输出接口电路与所述sram操作电路耦接,且被配置为将接收的第一输入数据提供给所述sram操作电路以及从所述sram操作电路接收要输出的第一输出数据;所述纠检错电路被配置为对目标数据进行编码和解码并判断所述目标数据是否发生错误并纠错;所述列选电路还被配置为隔离所述sram操作电路的操作和所述非易失存储操作电路的操作,以及隔离所述第一数据读写操作、所述第二数据读写操作和所述数据恢复操作;所述第二输入输出接口电路与所述nvsram阵列耦接,且被配置为对所述nvsram阵列进行第二数据读写操作。

2、例如,在本公开一实施例提供的存储装置中,所述纠检错电路还被配置为:在所述非易失存储操作电路进行所述数据备份操作的情况下,对从所述sram操作电路输入所述纠检错电路的目标数据进行编码;以及所述纠检错电路还被配置为,在所述列选电路完成所述数据恢复操作的情况下,确定所述sram操作电路从所述nvsram阵列读取并输入所述纠检错电路的目标数据是否发生错误并纠错。

3、例如,在本公开一实施例提供的存储装置中,所述纠检错电路还被配置为,在进行编码时,对读取的所述目标数据的k位信息码进行编码得到r位校验码,通过所述sram操作电路将所述r位校验码写入所述nvsram阵列中;以及,所述纠检错电路还被配置为,在进行解码时,对读取的所述目标数据的k位信息码和r位校验码进行解码检错,响应于发生错误则进行纠错,将k位纠错后的信息码通过所述sram操作电路写入所述nvsram阵列中,其中,k和r为正整数。

4、例如,在本公开一实施例提供的存储装置中,所述第二输入输出接口电路包括移位寄存操作电路、输入接口电路和输出接口电路,所述移位寄存操作电路与所述nvsram阵列耦接,且被配置为对所述nvsram阵列进行所述第二数据读写操作;所述输入接口电路与所述移位寄存操作电路耦接,且被配置为接收第二输入数据且将接收的所述第二输入数据提供给所述移位寄存操作电路;所述输出接口电路与所述移位寄存操作电路耦接,且被配置为从所述移位寄存操作电路接收要输出的第二输出数据。

5、例如,在本公开一实施例提供的存储装置,还包括:字线驱动电路,

6、所述字线驱动电路被配置为,在所述sram操作电路进行所述第一数据读写操作的情况下,或者在所述列选电路进行所述数据恢复操作的情况下,或者在所述第二输入输出接口电路进行所述第二数据读写操作的情况下,或者在所述非易失存储操作电路进行所述数据备份操作的情况下,选择所述nvsram阵列中需要被操作的对象单元行。

7、例如,在本公开一实施例提供的存储装置中,所述第二输出接口电路还包括隔离子电路,其中,所述隔离子电路耦接在所述nvsram阵列和所述移位寄存操作电路之间;所述隔离子电路被配置为,在所述移位寄存操作电路进行所述第二数据读写操作的情况下,导通所述移位寄存操作电路与所述nvsram阵列的耦接。

8、例如,在本公开一实施例提供的存储装置中,所述隔离子电路还被配置为,在所述非易失存储操作电路进行所述数据备份操作的情况下,或者在所述列选电路进行所述数据恢复操作的情况下,或者在所述sram操作电路进行所述第一数据读写操作的情况下,断开所述移位寄存操作电路与所述nvsram阵列的耦接。

9、例如,在本公开一实施例提供的存储装置中,所述移位寄存操作电路通过n组传输线与所述nvsram阵列耦接;所述输入接口电路通过w2组传输线与所述移位寄存操作电路耦接;所述输出接口电路通过w2组传输线与所述移位寄存操作电路耦接,其中,w2和n为整数且n≥w2>1。

10、例如,在本公开一实施例提供的存储装置中,所述非易失存储操作电路还被配置为,在所述sram操作电路进行所述第一数据读写操作的情况下,或者在所述列选电路进行所述数据恢复操作的情况下,或者在所述第二输入输出接口电路进行所述第二数据读写操作的情况下,断开与所述nvsram阵列的耦接;所述列选电路还被配置为,在所述sram操作电路进行所述第一数据读写操作的情况下,连通所述sram操作电路和所述nvsram阵列的耦接;所述列选电路还被配置为,在进行所述数据恢复操作的情况下,断开所述sram操作电路和所述nvsram阵列的耦接;所述列选电路还被配置为,在所述第二输入输出接口电路进行所述第二数据读写操作的情况下,断开所述sram操作电路和所述nvsram阵列的耦接。

11、例如,在本公开一实施例提供的存储装置中,所述非易失存储操作电路还被配置为,在所述非易失存储操作电路进行所述数据备份操作的情况下,连通与所述nvsram阵列的耦接;所述列选电路还被配置为,在所述非易失存储操作电路进行所述数据备份操作的情况下,断开所述sram操作电路和所述nvsram阵列的耦接;所述第二输入输出接口电路还被配置为,断开与所述nvsram阵列的耦接。

12、例如,在本公开一实施例提供的存储装置中,所述列选电路还包括数据恢复操作子电路;所述数据恢复操作子电路被配置为,对所述对象单元列中的非易失存储子单元数据进行所述数据恢复操作。

13、例如,在本公开一实施例提供的存储装置中,所述nvsram阵列的阵列宽度为n;所述nvsram阵列包括m行所述nvsram单元;所述纠检错电路通过传输线与所述sram操作电路耦接;所述sram操作电路通过w1组传输线与所述输入输出接口电路耦接;所述sram操作电路通过w1组传输线与所述列选电路耦接;所述列选电路通过n组传输线与所述nvsram阵列耦接;所述非易失存储操作电路通过n组传输线与所述nvsram阵列耦接,其中,w1、n和m为整数且1<n,1<m,1<w1≤n。

14、例如,在本公开一实施例提供的存储装置中,所述字线驱动电路还被配置为,在所述非易失存储操作电路进行所述数据备份操作的情况下,选择所述nvsram阵列的i行nvsram单元中的sram存储子单元数据以进行所述数据备份操作;或,在所述列选电路进行所述数据恢复操作的情况下,选择所述nvsram阵列的j行nvsram单元中的非易失存储子单元数据以进行所述数据恢复操作,其中,i和j为整数,且m≥i≥1,m≥j≥1。

15、例如,在本公开一实施例提供的存储装置中,所述sram操作电路还被配置为,在进行所述第一数据读写操作的情况下,对被选择的所述nvsram阵列的第i行的w1个nvsram单元中的sram存储子单元的数据进行所述第一数据读写操作;所述第二输入输出接口电路还被配置为,在进行所述第二数据读写操作的情况下,对被选择的所述nvsram阵列的第i行的w2个nvsram单元中的sram存储子单元的数据进行所述第二数据读写操作;所述非易失存储操作电路还被配置为,在进行所述数据备份操作的情况下,对被选择的所述nvsram阵列的e行和/或f列的nvsram单元中的sram存储子单元的数据进行所述数据备份操作;所述列选电路还被配置为,在进行数据恢复操作的情况下,对被选择的所述nvsram阵列的g行和/或h列的nvsram单元中的非易失存储子单元的数据进行所述数据恢复操作,其中,i、e、f、g、h、w为整数,且n≥w1≥1,n≥w2≥1,m≥e≥1,m≥g≥1,n≥f≥1,n≥h≥1,m≥i≥1。

16、例如,在本公开一实施例提供的存储装置中,所述非易失存储子单元包括rram存储子单元、mram存储子单元或pram存储子单元。

17、例如,在本公开一实施例提供的存储装置,还包括控制电路,其中,所述控制电路与所述sram操作电路、所述非易失存储操作电路、所述纠检错电路、所述第一输入输出接口电路、所述列选电路和所述第二输入输出接口电路耦接且被配置为,根据选择的工作模式向所述sram操作电路、所述非易失存储操作电路、所述纠检错电路、所述第一输入输出接口电路、所述列选电路和所述第二输入输出接口电路提供对应的控制信号。

18、本公开至少一个实施例提供一种电子设备,包括本公开任一实施例提供的存储装置。

19、本公开至少一个实施例提供一种存储装置的控制方法,用于本公开任一实施例提供的存储装置。该控制方法包括:控制所述纠检错电路对所述目标数据进行编码和解码并判断所述目标数据是否发生错误并纠错。

20、例如,在本公开一实施例提供的控制方法中,控制所述纠检错电路对所述目标数据进行编码和解码并判断所述目标数据是否发生错误并纠错,包括:在所述非易失存储操作电路进行所述数据备份操作的情况下,对从所述sram操作电路输入所述纠检错电路的目标数据进行编码;以及在所述列选电路完成所述数据恢复操作的情况下,确定所述sram操作电路从所述nvsram阵列读取并输入所述纠检错电路的目标数据是否发生错误并纠错。

21、例如,在本公开一实施例提供的控制方法中,在进行编码时,对读取的所述目标数据的k位信息码进行编码得到r位校验码,通过所述sram操作电路将所述r位校验码写入所述nvsram阵列中;在进行解码时,对读取的所述目标数据的k位信息码和r位校验码进行解码检错,响应于发生错误则进行纠错,将k位纠错后的信息码通过所述sram操作电路写入所述nvsram阵列中,其中,k和r为正整数。

22、例如,在本公开一实施例提供的控制方法,还包括:在确定所述sram操作电路进行所述第一数据读写操作的情况下,断开所述非易失存储操作电路与所述nvsram阵列的耦接,控制所述列选电路连通所述sram操作电路与所述nvsram阵列的耦接,控制所述第二输入输出电路断开与所述nvsram阵列的耦接;或,在确定所述第二输入输出接口电路进行所述第二数据读写操作的情况下,断开所述非易失存储操作电路与所述nvsram阵列的耦接,连通所述第二输入输出接口电路与所述nvsram阵列的耦接,控制所述列选电路断开所述sram操作电路与所述nvsram阵列的耦接;或,在确定所述非易失存储操作电路进行所述数据备份操作的情况下,连通所述非易失存储操作电路与所述nvsram阵列的耦接,控制所述列选电路断开所述sram与所述nvsram阵列的耦接,控制所述移位寄存操作电路断开与所述nvsram阵列的耦接;或,在确定所述列选电路进行所述数据恢复操作的情况下,断开所述非易失存储操作电路与所述nvsram阵列的耦接,控制所述列选电路断开所述sram操作电路与所述nvsram阵列的耦接,控制所述第二输入输出接口电路断开与nvsram阵列的耦接。

23、例如,在本公开一实施例提供的控制方法,还包括:接收工作模式信号;根据所述工作模式信号产生用于所述第一数据读写操作、所述数据备份操作、所述数据恢复操作、所述第二数据读写操作或数据纠检错操作的控制信号;将所述控制信号对应地提供给所述sram操作电路、所述非易失存储操作电路、所述列选电路、所述第二输入输出接口电路、所述纠检错电路或所述第一输入输出接口电路。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185510.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。