一种TCAM存储器的内建自测试方法与流程

- 国知局

- 2024-07-31 20:15:22

本发明公开了一种tcam存储器的内建自测试方法,涉及芯片可测性设计、芯片生产测试。

背景技术:

1、tcam是ternary content addressable memory的缩写,即三态内容寻址存储器,它是从cam的基础上发展而来。tcam中每个bit除了“0”和“1”两个状态外,还有一个“don’tcare”状态,所以称为“三态”。现有技术中,tcam一个bit能表示三个值,共有0/1/x三种状态,如图1所示。可以支持各种lookup key的任何组合查找,支持任意地mask任何不关心的字段,使其既能进行精确匹配查找,又能进行模糊匹配查询。

2、存储器件在制造过程中极易引入缺陷,所以完备的测试是必不可少的环节。常见的故障类型包括固定故障、跳变故障和相邻单元耦合故障等。由于接口和读写协议的差异,使得tcam的测试依赖半定制甚至全定制的解决方式,一般由ip使用者自行设计测试控制器和数据产生器/比较器,从而完成tcam的内建自测试。当内建自测试被激活的时候,数据产生器按照类似静态随机存储器(sram)读写方式对tcam的行/列存储单元完成读写操作,这种方法能够覆盖大部分固定故障和跳变故障,但是缺点在于相邻单元耦合故障和地址译码故障检测不全,产品缺陷水平偏高。

技术实现思路

1、本发明所要解决的技术问题是:针对现有技术的缺陷,提供一种tcam存储器的内建自测试方法,使用硬件描述语言定制化设计tcam存储器的内建自测试模块,充分检测出包括固定故障、跳变故障、相邻存储单元耦合故障和地址译码故障在内的各种生产制造缺陷,降低产品缺陷率,同时控制算法的复杂程度和芯片面积开销。

2、本发明为解决上述技术问题采用以下技术方案:

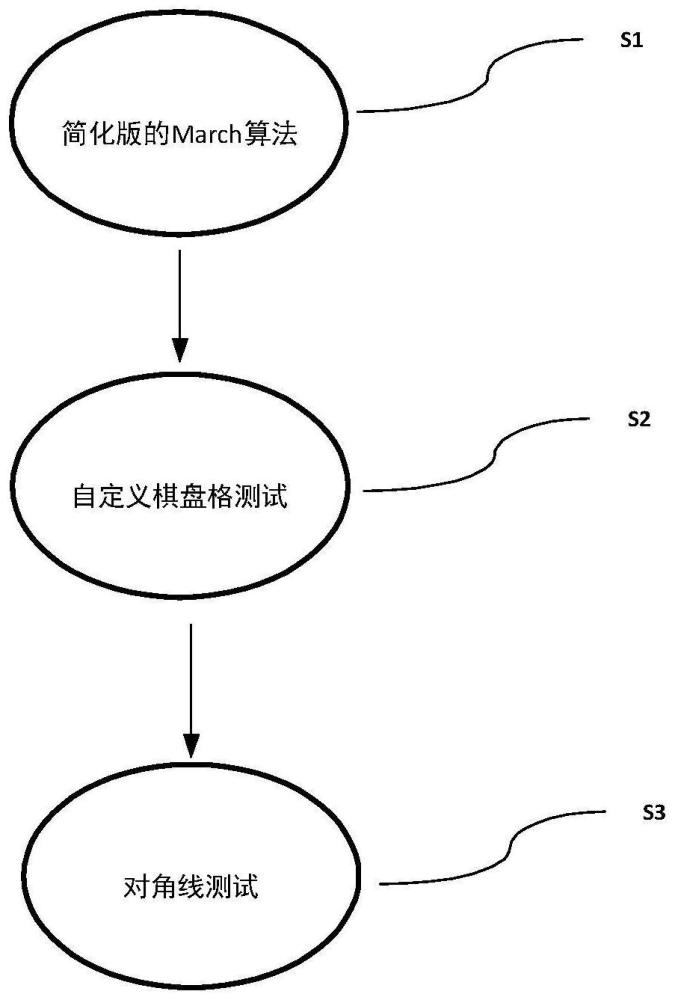

3、一种tcam存储器的内建自测试方法,所述方法包括如下步骤:

4、步骤一、通过简化的march算法完成固定故障检测。

5、作为本发明的进一步优选方案,所述步骤一具备包括:

6、101、所有存储地址写入00h,然后读出并判断其是否为00h;

7、102、将地址写入到存储单元中,然后读出数据并判断是否与写入的值一致;

8、103、将地址补码写入到存储单元中,然后读出数据并判断是否与写入的值一致。

9、步骤二、使用自定义棋盘格测试方法检测耦合故障。

10、作为本发明的进一步优选方案,所述步骤二具体包括:

11、201、偶数行存储单元数据由1变0,或者0变1,导致相邻存储单元被耦合为0的检测:

12、202、奇数行存储单元数据由1变0,或者0变1,导致相邻存储单元被耦合为0的检测;

13、203、偶数行存储单元数据由1变0,或者0变1,导致相邻存储单元被耦合为1的检测;

14、204、奇数行存储单元数据由1变0,或者0变1,导致相邻存储单元被耦合为1的检测。

15、步骤三、利用对角线测试方法补充耦合故障、跳变故障以及地址译码故障的检测。

16、作为本发明的进一步优选方案,所述步骤三具体包括:

17、301、按照地址升序的方式将所有存储单元全部写入0h;沿着对角线将存储单元写入1h,然后读出并判断是否与写入的一致;

18、302、按照地址降序的方式将所有存储单元全部写入1h;沿着对角线将存储单元写入0h,然后读出并判断是否与写入的一致;

19、303、按照地址降序的方式将所有存储单元全部写入0h;沿着反向对角线将存储单元写入1h,然后读出并判断是否与写入的一致;

20、304、按照地址升序的方式将所有存储单元全部写入1h;沿着反向对角线将存储单元写入0h,然后读出并判断是否与写入的一致。

21、作为本发明的进一步优选方案,所述方法通过verilog硬件描述语言实现,经过逻辑综合产生的门电路当作存储器件的外围接口电路集成在芯片内部。

22、作为本发明的进一步优选方案,所述对存储单元的写入和读出包括奇数行和偶数行的交替读写操作;所述对存储单元的写入和读出包括按照存储地址升序和降序的读写操作。

23、作为本发明的进一步优选方案,所述方法中,tcam mbist控制器完成与未完成、通过与失败的状态指示由两个专用信号bist_busy,bist_go送出,以供自动化测试设备观测。

24、作为本发明的进一步优选方案,所述方法用以检测固定故障和地址译码故障,以及相邻存储单元敏感耦合故障和跳变故障。

25、本发明采用以上技术方案与现有技术相比,具有以下技术效果:在简化march算法的基础上,增加了自定义的增强型棋盘格测试和对角线测试,将相邻单元耦合故障的覆盖率做到100%,有效地将产品缺陷水平降低到1dppm(百万分之一)以下,可测性设计额外引入的芯片面积开销被控制在存储器面积的5%以内。同时测试接口简单,仅需要5个信号即可完成内建自测试。

技术特征:1.一种tcam存储器的内建自测试方法,其特征在于,所述方法包括如下步骤:

2.如权利要求1所述的一种tcam存储器的内建自测试方法,其特征在于:所述方法通过verilog硬件描述语言实现,经过逻辑综合产生的门电路当作存储器件的外围接口电路集成在芯片内部。

3.如权利要求1所述的一种tcam存储器的内建自测试方法,其特征在于,所述步骤一具备包括:

4.如权利要求1所述的一种tcam存储器的内建自测试方法,其特征在于,所述步骤二具体包括:

5.如权利要求1所述的一种tcam存储器的内建自测试方法,其特征在于,所述步骤三具体包括:

6.如权利要求5所述的一种tcam存储器的内建自测试方法,其特征在于,所述对存储单元的写入和读出包括奇数行和偶数行的交替读写操作。

7.如权利要求6所述的一种tcam存储器的内建自测试方法,其特征在于,所述对存储单元的写入和读出包括按照存储地址升序和降序的读写操作。

8.如权利要求1所述的一种tcam存储器的内建自测试方法,其特征在于,所述方法中,tcam mbist控制器完成与未完成、通过与失败的状态指示由两个专用信号bist_busy,bist_go送出,以供自动化测试设备观测。

9.如权利要求1所述的一种tcam存储器的内建自测试方法,其特征在于:所述方法用以检测固定故障和地址译码故障,以及相邻存储单元敏感耦合故障和跳变故障。

技术总结本发明公开了一种TCAM存储器的内建自测试方法,所述方法先通过一种简化的March算法检测固定故障,然后再使用自定义的加强型棋盘格方法和对角线方法测试相邻单元敏感耦合故障、转换故障以及地址译码故障。此算法通过Verilog硬件描述语言实现,相对于一般的常规TCAM测试,它在节省芯片面积的同时,提高了测试覆盖率,降低了产品缺陷率(DPPM)。技术研发人员:陈希恒,韦红芳,李力游,小约翰·罗伯特·罗兰受保护的技术使用者:南京蓝洋智能科技有限公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240731/185575.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表