存储装置的制作方法

- 国知局

- 2024-08-02 15:54:14

本发明构思总体涉及存储装置、存储装置的使用以及用于制作存储装置的方法。

背景技术:

1、诸如电子非易失性存储装置的存储装置被广泛地用于电子装置中。例如,闪存可以将信息以电荷的形式存储在存储单元中。为了增加存储容量,可以使用3d集成电路技术以将存储单元堆叠成多层。然而,存储装置仍存在进一步改进的空间。

技术实现思路

1、本发明构思的目的是提供具有高存储容量的存储装置。另外的目的是提供低成本的存储装置。另外的目的是提供用于高频率操作和/或高功率操作和/或高温操作的存储装置。本发明构思的这些和其他目的由如独立权利要求中限定的发明来至少部分地满足。在从属权利要求中陈述了优选实施方式。

2、在该文本中,自然元素的缩写将根据元素周期表使用。例如,al意指铝,ga意指镓,as意指砷,mg意指镁,o意指氧,si意指硅,n意指氮。

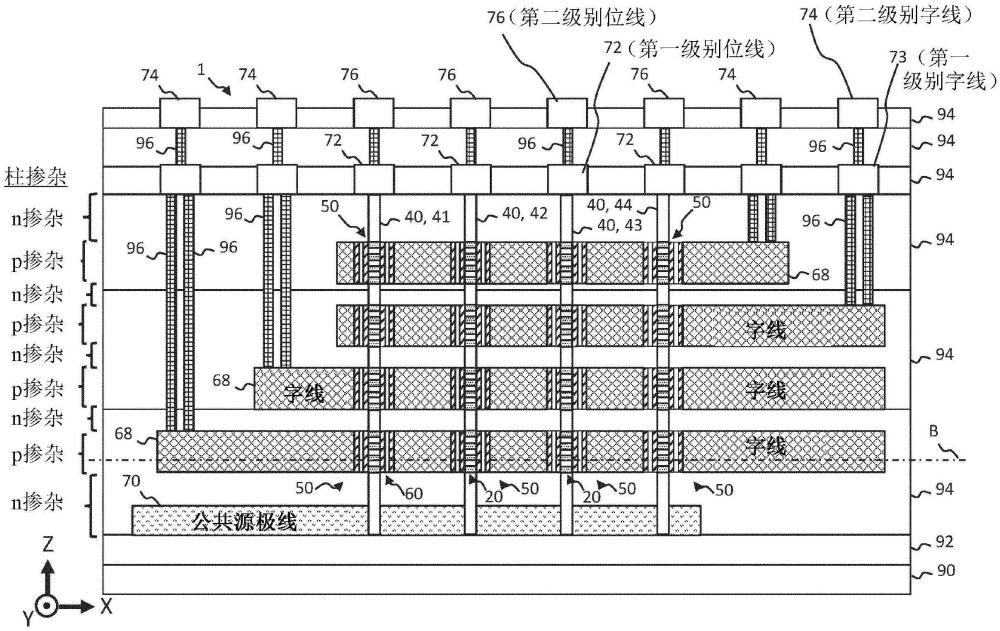

3、根据第一方面,提供了一种存储装置,其包括半导体材料的柱和与柱相关联的至少一个存储单元,其中,至少一个存储单元中的每一个包括电荷陷阱和晶体管,其中,对于至少一个存储单元中的每一个:

4、存储单元的电荷陷阱被配置成存储电荷,并且通过所述存储的电荷控制存储单元的晶体管的阈值电压;以及

5、存储单元的晶体管包括源极、本体和漏极,其中,源极、本体和漏极是沿着柱的轴向方向的相应柱段,其中,源极柱段和漏极柱段被本体柱段分隔,其中,晶体管是

6、-npn晶体管,其中,源极柱段为n掺杂,本体柱段为p掺杂,以及漏极柱段为n掺杂;或者

7、-pnp晶体管,其中,源极柱段为p掺杂,本体柱段为n掺杂,以及漏极柱段为p掺杂;

8、其中,晶体管的至少一个p掺杂柱段包括在柱的轴向方向上堆叠的多个半导体层,其中,多个半导体层的层由algan或gan制成,并且其中,多个半导体层被配置成使得铝含量在每个连续层之间改变,使得每隔一层具有比与其相邻的相互相对层低的铝含量。

9、意识到存储装置可以包括基于gan的材料。如本文中所使用的,术语“基于gan的材料”应当被解释为包括镓和氮的任何半导体材料,例如gan、algan、ingan、alingan。根据上文,存储单元的晶体管的至少一个p掺杂柱段包括多个半导体层,其中,多个半导体层的层由algan或gan制成,并且其中,多个半导体层被配置成使得铝含量在每个连续层之间改变。晶体管的其他柱段,例如n掺杂柱段,可以包括任何基于gan的材料,例如gan。

10、基于gan的材料可以促进高频率操作和/或高功率操作和/或高温操作。因此,包括基于gan的材料的存储装置可以在高频和/或高功率和/或高温下操作。可替选地或附加地,包括基于gan的材料的存储装置可以与同样由基于gan的材料制成的电子装置一起被嵌入,例如嵌入在同一芯片中或同一基板上。

11、可能在基于gan的材料中难以实现p掺杂。用于p掺杂的掺杂原子例如mg经常被氢杂质或氮空位钝化。因此,即使掺杂浓度高,自由空穴浓度也可能低。为了去除钝化(或激活掺杂原子),可以使用生长后退火,例如在低氢浓度的大气中的生长后退火。

12、意识到多个半导体层可以去除或减少对p掺杂基于gan的材料的生长后退火的需求。这有利于npn晶体管和/或pnp晶体管的制作,并且从而也有利于基于npn或pnp晶体管的存储装置的制作。因此,存储装置的存储单元的npn晶体管的p掺杂本体柱段可以包括所述多个半导体层。可替选地或附加地,存储装置的存储单元的pnp晶体管的p掺杂源极和/或漏极柱段可以包括所述多个半导体层。有利地,存储装置的存储单元的pnp晶体管的p掺杂源极柱段和漏极柱段二者可以包括所述多个半导体层。

13、多个半导体层可以通过价带边缘的变化来增强p掺杂,如由kozodoy等人[appl.phys.lett.75,2444(1999)]所描述的。价带边缘的变化在本文中由多个半导体层中的al含量的变化引起。在带边缘远低于费米能量的情况下,受主可以被电离,并且在带边缘接近费米级的情况下,产生的空穴可以积累。在本文中,价带边缘可以在与多个半导体层的层垂直的方向上变化。由于价带边缘的变化,空穴浓度也可能变化。然而,平均空穴浓度可以高于体膜中的平均空穴浓度,其中,价带边缘不变化。应当理解,价带边缘的变化可能由于多个半导体层中的变化带隙以及由于带弯曲导致的极化效应。

14、多个半导体层还可以增强空穴迁移率,如由kozodoy等人[appl.phys.lett.75,2444-2446(1999)]进一步描述的。

15、存在各种方式来实现多个半导体层,所述多个半导体层被配置成使得铝含量在每个连续层之间改变,使得每隔一层具有比其相邻的相互相对层低的铝含量。下面给出几个示例。

16、在第一示例中,多个半导体层包括层的序列,其中,偶数编号的层具有低铝含量,并且奇数编号的层具有高铝含量,或者反之亦然。

17、在第二示例中,多个半导体层包括层的序列,其中,每个层与编号n相关联,其中,n表示在层的序列中的位置,其中,具有偶数n的层具有比层编号n-1和层编号n+1低的铝含量。

18、在第三示例中,多个半导体层包括层的序列,其中,每个层与编号n相关联,其中,n表示在层的序列中的位置,其中,具有奇数n的层具有比层编号n-1和层编号n+1低的铝含量。

19、如本文所使用的,术语“存储单元”应当被解释为存储至少一比特的二进制信息的单元。存储在存储单元的电荷陷阱中的电荷可以表示所存储的二进制信息。

20、例如,存储单元可以被配置成存储一个比特。在本文中,电荷陷阱中不存在电荷(例如,电荷陷阱存储低于阈值的电荷)可以表示1。电荷陷阱中存在电荷(例如,电荷陷阱存储高于阈值的电荷)可以表示0。

21、由于存储单元的电荷陷阱被配置成存储电荷,并且通过所述存储的电荷控制存储单元的晶体管的阈值电压,因此存储单元可以通过在源极柱段与漏极柱段之间施加电压被读出。晶体管接通处的阈值电压由此指示存储了哪个比特值。存储单元的电荷陷阱可以布置在存储单元的晶体管的本体柱段附近。因此,存储在电荷陷阱中的电荷可以有效地控制晶体管的阈值电压。存储单元的电荷陷阱可以例如布置在存储单元的晶体管的本体柱段的横向侧上。

22、存储装置提供高存储容量,因为晶体管的源极、本体和漏极是沿着柱的轴向方向的相应柱段。因此,源极、本体和漏极可以堆叠在彼此的顶部上,并且从而在基板上具有小的占地面积。

23、如果多个存储单元与柱相关联,则可以实现存储容量的进一步改进。因此,存储单元可以堆叠成多层,使得可以在基板上的小区域内实现大的存储容量。应当理解,由于可以从同一基板制作更多的存储单元,因此在小区域内促进大的存储容量可以确保低成本的存储装置。

24、可以通过沿着柱的高度将晶体管堆叠在彼此的顶部上来实现与柱相关联的多个存储单元。应当理解,柱段可以由相邻晶体管共享。例如,包括具有两个npn晶体管的柱的存储装置可以通过以下掺杂序列来实现:npnpn。在本文中,中间中的n掺杂柱段可以用作第一晶体管的漏极柱段和第二晶体管的源极柱段二者。在每个本体柱段的附近可能存在电荷陷阱。在包括具有两个npn晶体管的柱的存储装置的上面示例中,可能在两个p掺杂段中的每一个的附近(例如在两个p掺杂段中的每一个的横向侧上)存在电荷陷阱。

25、如本文所使用,术语“柱”应当被解释为任何伸长构件,其中,柱的轴向方向是伸长的主要方向。柱可以竖立在基板上,其中,柱的轴向方向与基板垂直。柱可以从半导体材料的层中被蚀刻出,或者从半导体材料的多个层中被蚀刻出。在本文中,半导体材料可以是单晶半导体材料。柱可以具有小于1μm,例如在5nm与500nm之间的直径。柱可以有利地是纳米线。纳米线可以具有小于100nm,例如在5nm与100nm之间或在10nm与50nm之间的直径。柱的小直径可以有利于小的占地面积。此外,小直径,例如低于100nm的直径,可以通过量子限制效应提供高的电荷载流子迁移率。这可以提供存储装置的快速读取和写入速度。

26、柱的底部可以连接至基板。柱可以被嵌入在支承和/或电绝缘材料中。可替选地,柱可以自由地竖立在基板上而不嵌入。一个或更多个电栅极可以沿着柱的高度布置。例如,控制栅极可以布置在每个本体柱段的附近,例如每个本体柱段的横向侧处。

27、底部柱段和顶部柱段可以分别电连接。底部柱段和顶部柱段处的电连接可以被配置成驱动电流从底部柱段至顶部柱段通过柱,或者反之亦然。

28、存储装置可以被配置成使得对于至少一个存储单元中的每一个:

29、存储单元包括布置在柱的横向侧处的控制栅极,控制栅极被配置成通过控制栅极的相对于晶体管的阈值电压的电压来控制通过晶体管的本体柱段的电流;以及

30、存储单元的电荷陷阱布置在存储单元的控制栅极与晶体管的本体柱段之间,电荷陷阱包括第一氧化物层、电荷陷阱层和第二氧化物层,其中,第一氧化物层使电荷陷阱层与本体柱段分隔,并且第二氧化物层使电荷陷阱层与控制栅极分隔,其中,电荷陷阱层包括介电层和/或导电层。

31、如先前所提到的,存储单元的控制栅极可以布置在存储单元的晶体管的本体柱段附近,例如,所述本体柱段的横向侧处。控制栅极可以通过第一氧化物层和第二氧化物层与本体柱段电分隔。控制栅极的电压可以在本体柱段中感应电场,并且从而控制通过本体柱段的电流。当控制栅极的电压高于存储单元的晶体管的阈值电压时,晶体管可以接通,以允许电流通过。当控制栅极的电压低于存储单元的晶体管的阈值电压时,晶体管可以关断,以不允许电流通过。如先前所提到的,存储单元的电荷陷阱被配置成存储电荷,并且通过所述存储的电荷来控制存储单元的晶体管的阈值电压。当存储单元的电荷陷阱布置在存储单元的控制栅极与晶体管的本体柱段之间时,电荷陷阱中的电荷可以屏蔽来自控制栅极的电场,并且因此改变阈值电压。

32、根据上文,第一氧化物层可以被视为隧穿氧化物层,并且第二氧化物层可以被视为栅极氧化物层。

33、以下示例描述了如何可以从存储单元中读取值。当没有电荷被存储在电荷陷阱中时,晶体管的阈值电压可以是vt1。当电荷被存储在电荷陷阱中时,晶体管的阈值电压可以是vt2,其中,vt2>vt1。因此,当电荷被存储在电荷陷阱中时,需要控制栅极上的较高电压来使晶体管接通。然后,可以将控制栅极电压设置成中间电压,中间电压在vt2与vt1之间。如果晶体管在所述中间电压下导通,则阈值电压可以采用为vt1,指示没有电荷被存储在电荷陷阱中。因此,电荷陷阱中不存在电荷可以由通过晶体管的电流来指示,其可以表示1的二进制值。类似地,如果晶体管在所述中间电压下没有导通,则阈值电压可以采用为vt2,指示电荷被存储在电荷陷阱中。因此,电荷陷阱中存在电荷可以由不存在通过晶体管的电流来指示,其可以表示0的二进制值。

34、以下示例描述了如何可以将值写入至存储单元或从存储单元擦除值。写入和擦除可以通过将电荷隧穿通过第一氧化物层进入电荷陷阱层或从电荷陷阱层隧穿出来执行。隧穿过程可以是fowler–nordheim隧穿。可替选地,可以通过热电子注入来执行写入。

35、对于至少一个存储单元中的每一个,存储单元的电荷陷阱的第一氧化物层和/或第二氧化物层可以包括al2o3。al2o3的氧化物层可能是有利的,因为其可以通过原子层沉积来提供,而在界面处没有任何寄生陷阱状态。

36、如所描述,电荷陷阱层可以包括介电层,例如硅氮化物。介电层可能是有利的,因为一个存储单元的介电层可能不需要与另一存储单元的介电层电隔离。电荷可以被存储在介电层中的局部陷阱中,使得即使相同的介电层用于两个存储单元,电荷也不能从一个存储单元移动至另一存储单元。因此,可以简化制造。介电层可以包括高k介电材料。例如,对于至少一个存储单元中的每一个,存储单元的电荷陷阱的电荷陷阱层可以包括高k介电材料,例如y2o3、tio2、hfo2、zro2或la2o3。介电层可以例如通过原子层沉积来沉积。

37、如所描述,电荷陷阱层可以包括导电层。导电层包括电导电材料,例如金属或掺杂的半导体材料,例如简并掺杂的半导体材料。导电层可以具有其对陷阱相关的可靠性问题相当不敏感的优点。当使用导电层时,由于不足的陷阱可靠性,存储单元不太可能陷入永久逻辑状态(例如,总是1)。当使用导电层时,一个存储单元的导电层可以与其他存储单元的导电层电隔离。导电层可以例如通过原子层沉积来沉积。

38、应当理解,电荷陷阱层可以包括介电层和导电层二者。这样的电荷陷阱层可以组合两种材料的优点。

39、对于至少一个存储单元中的每一个,存储单元的晶体管可以包括一对半导体层的重复,其中,每对半导体层包括:

40、具有10%以下的al含量的低al含量层;以及

41、具有15%以上的al含量的高al含量层。

42、因此,低al含量层可以是alxga1-xn的层,其中,x<0.1。类似地,高al含量层可以是alxga1-xn的层,其中,x>0.15。优选的是,所有低al含量层具有相同的组成。例如,所有低al含量层可以具有为零的al含量,即它们包括gan,即x=0。优选的是,所有高al含量层具有相同的组成,并且它们具有在20%与40%之间的al含量,即,它们包括范围从al0.2ga0.8n至al0.4ga0.6n的材料,即,0.2<x<0.4。包括四个层的多个半导体层的示例可以是al0.2ga0.8n/gan/al0.2ga0.8n/gan或al0.3ga0.7n/gan/al0.3ga0.7n/gan。

43、作为替选方案,每对半导体层可以包括低al含量层和高al含量层,但是所有低al含量层不一定具有相同的al含量。类似地,所有高al含量层不一定具有相同的al含量。因此,多个半导体层可以是例如al0.2ga0.8n/al0.05ga0.95n/al0.16ga0.84n/gan或al0.3ga0.7n/al0.09ga0.91n/al0.22ga0.78n/al0.02ga0.98n/al0.2ga0.8n/al0.07ga0.93n。

44、作为第一近似,具有低al含量的层可以具有比具有高al含量的层小的带隙。这可能引起价带边缘的变化。然而,低al含量层与高al含量层之间的极化效应和/或应变效应可以修改价带边缘的变化。例如,变化的价带边缘中的局部能量最小值和局部能量最大值可以位于高al含量层与低al含量层之间的界面处。举例说明,假设晶体的表面是从基板延伸并且向上通过多个半导体层的ga面(当使用mocvd在蓝宝石上开始生长时可能是这样的情况),局部能量最小值可能出现在导带中的低al含量层过渡至高al含量层中的界面(让我们标记该区域为a)处,以及局部能量最大值可能出现在高al含量层过渡至低al含量层的界面(让我们标记该区域为b)处。上文的描述与[appl.phys.lett.75,2444-2446(1999)]的2445页上的描述类似,该描述通过引用包括于此。

45、应当注意,当该文本涉及多个半导体层为p掺杂时,其可以被解释为多个半导体层在a区域中被p掺杂但在b区域中不被p掺杂。这样的掺杂可以引起最高的空穴迁移率。然而,这样的掺杂当然也可以被解释为多个半导体层在多个半导体层的整个层中被p掺杂。

46、对于至少一个存储单元中的每一个,晶体管的至少一个p掺杂柱段的多个半导体层中的每个层可以具有3nm与10nm之间的厚度。层可以都具有相同的厚度,例如所有层具有3nm的厚度,所有层具有6nm的厚度,或者所有层具有10nm的厚度。可替选地,多个半导体层可以包括不同厚度的层。例如,所有低al含量层可以具有3nm与10nm之间的厚度,并且所有高al含量层可以具有3nm与10nm之间的厚度,其中,低al含量层的厚度与高al含量层的厚度不同。例如,每对半导体层可以包括例如6nm厚的低al含量层和5nm厚的高al含量层。

47、在3nm至10nm厚度范围内,p掺杂的增强可能是最有效的。例如,低al含量层与高al含量层之间的极化效应和/或应变效应可能在所述厚度范围内是最有效的。

48、应当理解,存储装置可以包括多个柱。例如,存储装置可以包括第一柱和第二柱,第一柱和第二柱中的每一个具有与所述柱相关联的至少一个存储单元,其中,第一柱的存储单元和第二柱的存储单元共享公共控制栅极,公共控制栅极被配置成通过公共控制栅极的电压来同时控制通过第一柱的存储单元的晶体管的本体柱段的电流和通过第二柱的存储单元的晶体管的本体柱段的电流。

49、因此,公共控制栅极可以是存储装置的字线。公共控制栅极使得能够从若干存储单元中同时读出。

50、根据第二方面,提供了根据第一方面的存储装置的供模数转换的使用,其中,用于模数转换的转换规则被存储在存储装置中。

51、转换规则可以是存储在存储装置中的查找表,其中,查找表使输入的模拟信号的幅度与所述幅度应转换成的数字值相关。

52、转换规则可以是存储在存储装置中的算法,其中,算法使输入模拟信号的幅度与所述幅度应转换成的数字值相关。算法可以是自校准算法。

53、根据第一方面的存储装置的使用可以有利于精确的模数转换。此外,模数转换器可以包括根据第一方面的存储装置,其中,用于模数转换的转换规则被存储在存储装置中。因此,包括基于gan的材料的模数转换器可以有利地包括根据第一方面的存储装置。

54、存储装置的其他使用可以包括现场可编程门阵列(fpga)中例如用于高功率或高温使用的fpga中的使用。

55、根据第二方面,提供了一种用于制作存储装置的方法,该方法包括:

56、将半导体层沉积在基板上,半导体层堆叠在堆叠方向上,由此由沉积的半导体层形成半导体结构;

57、蚀刻半导体结构以形成柱,柱具有在堆叠方向上的轴向方向;

58、在柱中形成晶体管,晶体管包括源极、本体和漏极,其中,源极、本体和漏极是沿着柱的轴向方向的相应柱段,其中,源极柱段和漏极柱段被本体柱段分隔,其中,晶体管是

59、-npn晶体管,其中,源极柱段为n掺杂,本体柱段为p掺杂,以及漏极柱段为n掺杂;或

60、-pnp晶体管,其中,源极柱段为p掺杂,本体柱段为n掺杂,以及漏极柱段为p掺杂;

61、其中,晶体管的至少一个p掺杂柱段包括在柱的轴向方向上堆叠的沉积的半导体层的多个半导体层,其中,p掺杂柱段的多个半导体层的层由algan或gan制成,并且其中,p掺杂柱段的多个半导体层被配置成使得铝含量在每个连续层之间改变,使得每隔一层具有比其相邻的相互相对层低的铝含量;

62、形成电荷陷阱,该电荷陷阱被配置成存储电荷,并且通过所述存储的电荷控制晶体管的阈值电压;

63、其中,晶体管和电荷陷阱是存储装置的存储单元的一部分。

64、该方法有利于存储装置的简单制作,特别是与常规3d闪存架构的制作相比。常规3d闪存架构装置可以通过在支承材料中蚀刻沟道空穴,并且然后将沟道材料沉积至所述空穴中来制作。意识到常规3d闪存架构的制作具有当前方法克服的几个缺点。

65、意识到在常规3d闪存架构的制作中,沟道空穴的干法蚀刻是具有挑战性的步骤,其中,经典的干法蚀刻化学物质被使用至其极限。

66、常规3d闪存架构可能需要沉积交替的层堆叠,并且然后以极高的精度蚀刻那些堆叠层。用于接触着陆的台阶蚀刻、硬掩模蚀刻、栅极沟槽蚀刻、沟道空穴蚀刻和台阶接触蚀刻是制造常规3d闪存装置可能需要的主要关键蚀刻。意识到常规3d闪存装置的制造涉及的等离子体蚀刻过程正变得越来越具有挑战性。在多个横向/竖直蚀刻周期中需要重复横向抗蚀剂掩模蚀刻,接着是竖直堆叠层蚀刻,以形成台阶形状接触着陆焊盘的台阶蚀刻在抗蚀剂掩模的横向至竖直蚀刻速率控制、抗蚀剂掩模形状控制、堆叠层蚀刻的选择性控制、台阶台阶宽度控制和台阶宽度均匀性控制方面提供了独特的挑战。硬掩模开口、栅极沟槽蚀刻、沟道空穴蚀刻和台阶接触蚀刻给蚀刻,尤其是范围在纵横比从30:1至>80:1的高纵横比(har)特征的蚀刻带来了显著挑战。此外,通过har交替层堆叠进行的蚀刻加剧了对蚀刻过程的需求,该蚀刻过程必须能够蚀刻无失真、竖直轮廓无弯曲、小面化(faceting)和特征堵塞。此外,需要交替堆叠中的平滑侧壁过渡,以及对微小焊盘的非常高的选择性,特别是对于台阶接触蚀刻应用,该台阶接触蚀刻应用组合了范围从30:1至>80:1的纵横比内的极端同时多级蚀刻,以及对下层接触材料的可忽略损失的极高选择性。

67、与常规3d闪存架构的常规自上而下制作相比,当前方法可以被视为自下而上的制作方法。

68、应当理解,根据该方法,可以蚀刻多于一个的柱。可以蚀刻多个柱,例如柱的阵列。

69、该方法还可以包括通过压印光刻来光刻地限定柱的横向大小和位置。压印光刻可以是纳米压印光刻。该方法可以包括通过压印光刻来光刻地限定柱的阵列。压印光刻是对大面积(例如,整个晶片)进行图案化的便宜且简单的方式。

70、电荷陷阱可以通过将第一氧化物层、电荷陷阱层、第二氧化物层和控制栅极沉积在柱的横向侧上来形成,

71、其中,第一氧化物层使电荷陷阱层与本体柱段分隔,并且第二氧化物层使电荷陷阱层与控制栅极分隔;

72、其中,电荷陷阱层包括介电层和/或导电层;

73、其中,控制栅极被配置成通过控制栅极的相对于晶体管的阈值电压的电压来控制通过晶体管的本体柱段的电流。

74、如先前所描述,第一氧化物层可以被视为隧穿氧化物层,并且第二氧化物层可以被视为栅极氧化物层。

75、通过将层沉积在柱的横向侧上,可以形成高质量的电荷陷阱。层厚度通过沉积来精确地控制。因此,隧穿氧化物层、电荷陷阱层和栅极氧化物层具有从柱至柱和从装置至装置的均匀厚度。

76、该方法可以包括蚀刻半导体结构以形成第一柱和第二柱,第一柱和第二柱中的每一个具有与所述柱相关联的至少一个存储单元,该方法还包括:

77、形成公共控制栅极,公共控制栅极在第一柱的存储单元与第二柱的存储单元之间共享,公共控制栅极被配置成通过公共控制栅极的电压来同时控制通过第一柱的存储单元的晶体管的本体柱段的电流和通过第二柱的存储单元的晶体管的本体柱段的电流,其中,公共控制栅极在蚀刻半导体结构以形成第一柱和第二柱之后形成。

78、因此,公共控制栅极可以是存储装置的字线。公共控制栅极使得能够从若干存储单元同时读出。在蚀刻半导体结构以形成第一柱和第二柱之后形成公共控制栅极有利于稳定的制作过程。换句话说,在柱周围形成字线有利于稳定的制作过程。相比之下,在字线之间蚀刻空穴以在空穴中形成沟道可能创建脆弱的结构,很像“纸牌屋”。

79、根据该方法,第一氧化物层、电荷陷阱层和第二氧化物层可以通过一种或更多种保形沉积技术例如原子层沉积和/或化学气相沉积和/或等离子体增强化学气相沉积来沉积。

80、所述保形沉积技术可以是被配置成沉积具有少方向或不考虑方向的层的技术。

81、控制栅极可以通过定向沉积技术例如蒸镀或溅射来沉积。所述定向沉积技术可以是被配置成主要在一个方向,例如由蒸镀器的加热舟皿(boat)与蒸镀器的目标区域之间的直线路径限定的方向上沉积层的技术。

82、应当注意,根据第一方面的存储装置、根据第二方面的对存储装置的使用以及根据第三方面的用于制作存储装置的方法都可以具有相同的优点或相似的优点。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248421.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表