CMOS工艺中的浮栅型分栅闪存结构及其制造方法与流程

- 国知局

- 2024-08-02 15:56:57

本发明涉及半导体,特别是涉及一种cmos工艺中的浮栅型分栅闪存结构及其制造方法。

背景技术:

1、分栅(split-gate)浮栅(floating-gate)闪存技术被广泛用于各种嵌入式电子产品如金融ic卡、汽车电子等应用。提高存储集成密度有利于节省芯片面积、降低制造成本。

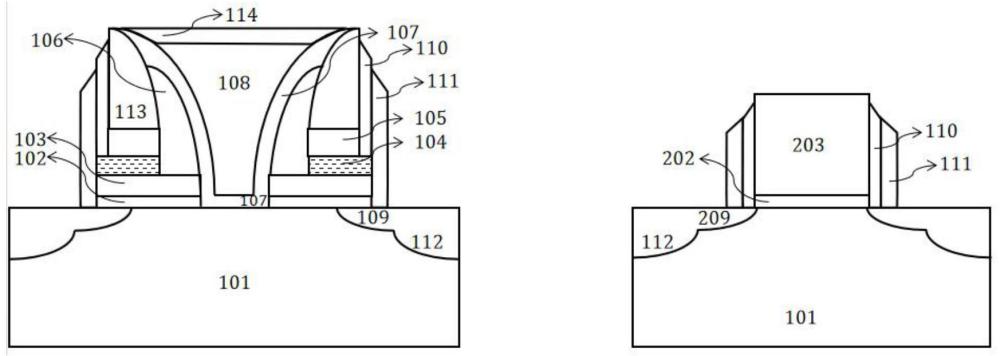

2、现有的2-bit/cell(二比特每存储单元)的分栅浮栅闪存的结构如图1所示,其中各附图标记为:

3、分栅闪存区:101—p型衬底上形成的中-高压的p型阱,102—浮栅介质层,103—浮栅多晶硅,104—多晶硅间ono(oxide-nitride-oxide)介质叠层,105—控制栅多晶硅,106—第二侧墙介质层,107—选择栅介质层,108—选择栅多晶硅层,109—轻掺杂漏(lightly doped drain,ldd)、halo/pocket离子注入,110—第三侧墙介质层,111—第四侧墙介质层,112—源漏重掺杂离子注入,113—第一侧墙介质层,114—保护选择栅多晶硅的介质层氧化硅

4、以低压cmos为例,cmos区:201—p型衬底上形成的cmos阱注入,202—cmos栅介质层,203—cmos多晶硅层,209—cmos轻掺杂漏(lightly doped drain,ldd)、halo/pocket离子注入,110—cmos器件的第一侧墙介质层(与闪存share,即闪存器件的第三侧墙),111—cmos器件的第二侧墙介质层(与闪存share,即闪存器件的第四侧墙),112—源漏重掺杂离子注入。

5、2bit/cell的浮栅型分栅闪存器件的进一步微缩发现,由于cg(control-gate/coupling-gate,控制栅)与fg交叠的面积的减小,cg至fg的耦合系数大幅下降,而wl(word-line/select-gate,字线/选择栅)和fg的交叠面积基本不变,wl至fg的耦合系数迅速增加,wl耦合系数的迅速增大使得器件cg的关断能力(cg的控制能力)变差,漏电十分严重,即闪存cell的亚域的电流特性变差。因此如何增大cg的耦合系数(即增大cg与fg的交叠面积)、改善fg的短沟道效应、减小wl的耦合系数对于进一步微缩浮栅型分栅闪存十分关键。该器件中,先进cmos器件中的第一侧墙和第二侧墙作为闪存单元的第三和第四侧墙,由于cell的第三和第四侧墙较厚,不利于闪存器件的微缩,有待于进一步改善。

6、为解决上述问题,需要提出一种新型的cmos工艺中的浮栅型分栅闪存结构及其制造方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种cmos工艺中的浮栅型分栅闪存结构及其制造方法,用于解决现有技术中先进cmos器件中的第一侧墙和第二侧墙作为闪存单元的第三和第四侧墙,由于存储单元的第三和第四侧墙较厚,不利于闪存器件的微缩的问题。

2、为实现上述目的及其他相关目的,本发明提供一种cmos工艺中的浮栅型分栅闪存结构,包括:

3、衬底,在所述衬底上形成有sti以定义出闪存区和外围逻辑区的有源区;

4、形成于所述衬底上的闪存区掺杂阱;

5、形成于所述闪存区上的浮栅介质层、浮栅多晶硅层、极间介质层和控制栅多晶硅层及其上的第一侧墙,所述控制栅多晶硅层的长度为所述第一侧墙的厚度;由所述第一侧墙为掩膜刻蚀形成的第二沟槽;在所述第二沟槽中形成有第二侧墙,所述第二侧墙覆盖所述第二沟槽的部分侧壁;由所述第一、二侧墙为掩膜刻蚀所述第二沟槽底壁的所述浮栅多晶硅层和所述浮栅介质层形成的第三沟槽;

6、栅介质层,所述栅介质层覆盖所述第三沟槽的底壁和侧壁;

7、选择栅多晶硅层,所述选择栅多晶硅层填充所述第三沟槽;以及,

8、选择栅氧化层,所述选择栅氧化层覆盖所述选择栅多晶硅层;

9、形成于所述衬底上的cmos区域掺杂阱,形成于所述cmos区域掺杂阱上的cmos栅介质层,在所述cmos栅介质层上形成有cmos栅极;

10、第三、四侧墙:在所述闪存区上,所述第三侧墙由所述控制栅多晶硅层上延伸至所述控制栅多晶硅层、所述第一侧墙的侧壁上,所述浮栅多晶硅层的长度为所述第一至三侧墙的厚度之和,所述第四侧墙由所述浮栅介质层、浮栅多晶硅层、极间介质层的侧壁延伸至所述第三侧墙上;在所述外围逻辑区上,所述第三、四侧墙依次形成于所述cmos栅介质层、cmos栅极的侧壁上;

11、位于所述闪存区的第一轻掺杂漏,位于所述cmos区域的第二轻掺杂漏;

12、在所述闪存区域和所述coms区域上形成的源漏重掺杂离子注入。

13、优选地,所述衬底为p型衬底,所述闪存区掺杂阱为形成于所述衬底上的p型掺杂阱。

14、优选地,所述极间介质层由自下而上依次堆叠的第一氧化层、氮化层、第二氧化层组成。

15、优选地,所述cmos栅介质层的材料为二氧化硅。

16、优选地,所述浮栅介质层的材料为二氧化硅。

17、本发明还提供一种上述cmos工艺中的浮栅型分栅闪存结构的制造方法,包括:

18、步骤一、提供衬底,在所述衬底上形成有sti以定义出闪存区和外围逻辑区的有源区,在所述衬底上形成有闪存区掺杂阱,在所述有源区上依次形成浮栅介质层、浮栅多晶硅层、极间介质层和控制栅多晶硅层;

19、步骤二、在控制栅多晶硅层上形成硬掩膜层,在所述硬掩膜层上形成形成第一沟槽,以定义出闪存单元的形成区域;

20、步骤三、在所述第一沟槽中形成第一侧墙,所述第一侧墙覆盖所述第一沟槽的侧壁;刻蚀所述第一沟槽底壁的所述控制栅多晶硅层和所述极间介质层以形成第二沟槽;在所述第二沟槽中形成第二侧墙,所述第二侧墙覆盖所述第二沟槽的部分侧壁;刻蚀所述第二沟槽底壁的所述浮栅和所述栅氧化层以形成第三沟槽;形成栅介质层,所述栅介质层覆盖所述第三沟槽的底壁和侧壁;形成选择栅多晶硅层,所述选择栅多晶硅层填充所述第三沟槽;以及,形成选择栅氧化层,所述选择栅氧化层覆盖所述选择栅多晶硅层,从而形成第一叠层结构;

21、步骤四、利用光刻、刻蚀去除所述外围逻辑区中的所述浮栅介质层、浮栅多晶硅层、极间介质层和控制栅多晶硅层,利用离子注入在所述外围逻辑区中形成cmos区域掺杂阱,之后在所述cmos区域掺杂阱上形成cmos栅介质层,在所述cmos栅介质层上形成cmos栅极,之后去除所述外围逻辑区上的所述硬掩膜层;

22、步骤五、利用淀积、刻蚀在所述第一叠层结构的侧壁和所述cmos栅介质层、所述cmos栅极的侧壁形成第三侧墙,定义外围逻辑区上的结构为第一叠层结构;

23、步骤六、形成覆盖所述cmos区域的第一光刻胶层,利用所述第一侧墙、栅介质层、选择栅氧化层、第三侧墙为掩膜刻蚀去除两侧的所述极间介质层、浮栅多晶硅层和浮栅介质层,使得所述浮栅多晶硅层的长度为所述第一至三侧墙的厚度之和,控制栅多晶硅层的长度为所述第一侧墙的厚度,从而形成第二叠层结构,在所述第二叠层结构两侧的所述衬底上形成第一轻掺杂漏,去除所述第一光刻胶层;

24、步骤七、形成覆盖所述闪存区域的第二光刻胶层,利用所述cmos栅极及其侧壁的第三侧墙为掩膜进行自对准离子注入形成第二轻掺杂漏;

25、步骤八、利用淀积、刻蚀在所述第二叠层结构的侧壁和所述cmos区域上的所述第三侧墙上形成第四侧墙;

26、步骤九、分别在所述闪存区和所述coms区域上进行源漏重掺杂离子注入。

27、优选地,步骤一中的所述衬底包括块状半导体衬底或绝缘体上硅(soi)衬底。

28、优选地,步骤一中的所述极间介质层由自下而上依次堆叠的第一氧化层、氮化层、第二氧化层组成。

29、优选地,步骤一中的所述浮栅介质层的材料为二氧化硅。

30、优选地,步骤二中的所述硬掩膜层的材料为氮化硅。

31、优选地,步骤四中的所述cmos栅介质层的材料为二氧化硅。

32、如上所述,本发明的cmos工艺中的浮栅型分栅闪存结构及其制造方法,具有以下有益效果:

33、本发明控制栅多晶硅层的外侧仍是第三侧墙和第四侧墙,与现有结构一致,有利于保持控制栅多晶硅层与位线之间的隔离能力;浮栅多晶硅层的长度等于第一、二侧墙的厚度+先进cmos工艺中cmos器件的第三侧墙的厚度,而cmos器件中的第四侧墙用作闪存浮栅多晶硅层侧面的侧墙,因此增大了浮栅多晶硅层,有利于改善浮栅多晶硅层的短沟道效应,改善器件i-v的亚域区的特性,降低器件的漏电;相比现有工艺,浮栅多晶硅层的增加的长度等于浮栅多晶硅层侧壁侧墙减小的长度,因此并没有增大闪存单元的面积。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248599.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表