一种光电芯片封装结构的制作方法

- 国知局

- 2024-08-22 14:38:53

本发明涉及芯片封装,具体涉及一种光电芯片封装结构。

背景技术:

1、目前,集成电路封装通常有两种方案:

2、一、光子芯片(也被称为:光芯片)设置在电子芯片(也被称为:电芯片)上方

3、例如,专利申请cn115706058a公开了一种半导体封装装置及其制造方法。其中,该半导体封装装置中的光子芯片通过第一互连结构、光学器件、重布线结构等结构设置在电子芯片的上表面,以使得光子芯片和电子芯片达到较佳的对位耦光效果。

4、又例如,专利申请cn115706108a公开了一种半导体封装结构及其制造方法,所述半导体封装结构中通过两个电子芯片并列设置,以在其上表面共同承载光子芯片。

5、二、电子芯片设置在光子芯片上方

6、例如,专利申请cn114063229a公开了半导体装置。所述半导体装置包括:pic芯片(也即光芯片),其包括孔中导电结构;第一电子集成电路芯片即第一eic芯片(也即电芯片),所述第一eic芯片设置在所述pic芯片的第一表面;第二电子集成电路芯片即第二eic芯片,所述第二eic芯片设置在所述pic芯片的第二表面。但是,这种将光芯片设置在电芯片之下的方案需要在光芯片上设置硅通孔(through silicon via, 常简写为tsv)。而在光芯片上开硅通孔的加工工艺难度很高,成本也非常高昂。

7、但是,随着大数据、人工智能、远程医疗、物联网、电子商务、5g通信的不断发展,全球数据流量爆发式地增长,更低成本、更可靠、更快及更高密度的电路是集成电路封装追求的目标。而以上这种传统的封装方案在应对高密度电路集成时,在加工难度、工作稳定性上均存在一定缺陷。

技术实现思路

1、本发明的目的在于提供一种光电芯片封装结构(或者说,一种光电芯片的3d封装结构),部分地解决或缓解现有技术中的上述不足,能够简化光电芯片的封装结构(进而简化加工工艺),提升光电芯片的工作稳定性。

2、为了解决上述所提到的技术问题,本发明具体采用以下技术方案:

3、本发明的第一方面,在于提供一种光电芯片封装结构,包括:

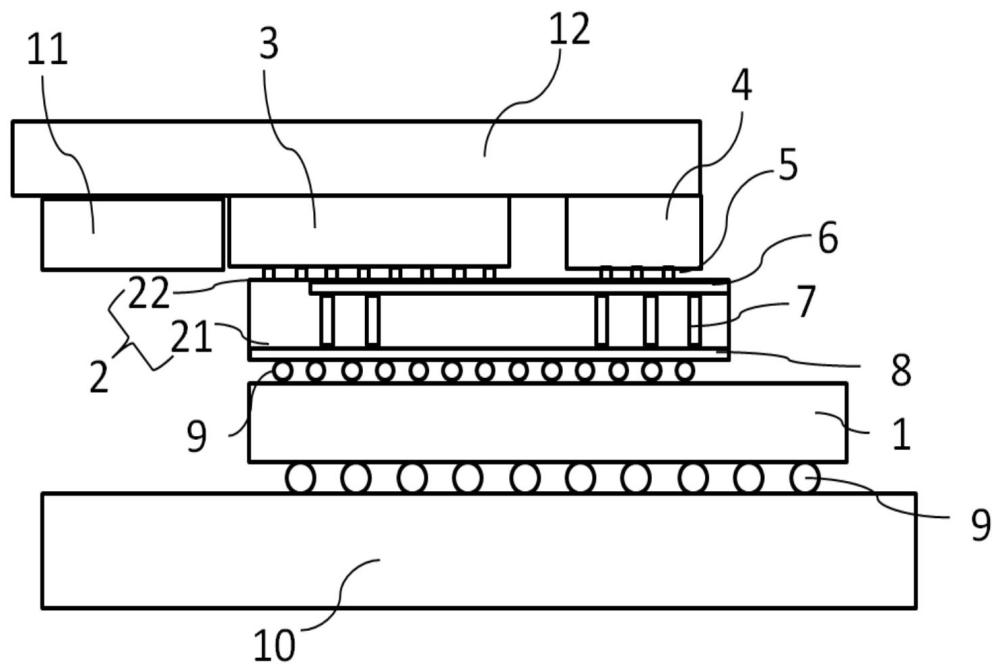

4、基板,所述基板的上表面设置有信号传输层,所述信号传输层上设置有信号处理层;

5、所述信号传输层包括:至少一个第一电芯片,所述第一电芯片具有第一表面和第二表面,且所述第一表面面向所述基板设置,所述第二表面朝向所述信号处理层设置;

6、所述信号处理层包括:信号转化区,以及数据存储区;

7、所述信号转化区对应设置有至少一个光芯片,所述光芯片包括:n*m个光子计算单元,所述光子计算单元包括:光波导层,位于所述光波导层上的调制层,所述调制层为相变材料层或所述调制层包括相变材料层;

8、所述光芯片用于接收所述第一电芯片所输入的调制信号,至少一组所述光子计算单元响应于所述调制信号将对应的所述相变材料层调制为特定状态,且所述光子计算单元将在所述特定状态下完成对应计算任务,并输出相应的计算数据;

9、所述数据存储区对应设置有至少一个第二电芯片,所述第二电芯片用于接收并存储所述计算数据;其中,所述信号处理层到所述信号传输层的电连接路径包括先后经过的第一键合结构、第一再分布层、硅通孔、第二再分布层。

10、在一些实施例中,至少一个所述第二电芯片的尺寸小于所述信号传输层的尺寸,所述信号传输层的尺寸为所述至少一个第一电芯片的总尺寸。

11、在一些实施例中,所述第一电芯片的第二表面上设置有至少两个高带宽内存芯片,至少两个所述高带宽内存芯片分别设置在所述光芯片的两侧;

12、所述第一电芯片上包括:xdac控制电路、xadc控制电路、wdac控制电路,以及与所述高带宽内存芯片通信的通信控制电路;其中,所述xdac控制电路用于向所述调制层提供对应的所述调制信号,所述xadc控制电路用于接收所述光子计算单元中的光电探测器的输出信号,且所述wdac控制信号用于向调制之后的所述光子计算单元提供计算输入信号,且所述光子计算单元响应于所述计算输入信号完成计算并输出所述计算数据。

13、在一些实施例中,所述信号处理层还包括:与所述数据存储区通信连接的数据转换区,且所述数据转换区对应设置有至少一个第二电芯片,且对应所述第二电芯片通过所述第一电芯片接收到对应的所述计算数据,以按照设定数据转换规则将所述计算数据转换为特定格式,并将转换为特定格式的所述计算数据输入至位于所述数据存储区中的所述第二电芯片中。

14、在一些实施例中,还包括:至少一个任务分配单元,且至少一个所述任务分配单元与对应功能分区相连接,所述功能分区中排列设置有多个所述第二电芯片;所述功能分区包括:数据存储区和/或数据转换区;对应地,所述任务分配单元被配置为执行以下步骤:

15、当至少一个所述第二电芯片接收到对应的所述计算数据时,监测所述第二电芯片在第一时段中的功耗数据;

16、当所述功耗数据大于第一设定阈值,且小于或等于第二设定阈值时,则采用第一分配规则对当前的计算数据进行分配处理;其中,所述第一分配规则要求在第二时段内暂停向当前的第二电芯片传输新的计算数据,并选用与所述当前的第二电芯片的间距大于第一间距的所述第二电芯片接收后续待处理的所述新的计算数据;

17、当所述功耗数据大于所述第二设定阈值,且小于或等于第三设定阈值时,则采用第二分配规则对所述计算数据进行分配;其中,所述第二分配规则要求在所述第二时段内暂停向所述当前的第二电芯片传输所述新的计算数据,并选用与所述当前的第二电芯片的间距大于第二间距的所述第二电芯片接收后续待处理的所述新的计算数据,且所述第二间距大于所述第一间距;

18、当所述功耗数据大于所述第三设定阈值时,采用第三分配规则对所述计算数据进行分配;其中,所述第三分配规则要求暂停当前所述第二电芯片对所述当前的计算数据的处理,并将所述当前的计算数据重新分配至与所述当前的第二电芯片之间的间距大于所述第二间距的至少一个所述第二电芯片。

19、在一些实施例中,至少一个所述第二电芯片为现场可编程逻辑门阵列芯片。

20、在一些实施例中,所述第一电芯片为专用集成电路芯片。

21、在一些实施例中,所述信号处理层上设置有散热片,所述散热片的下表面至少包覆至少一个所述光芯片和所述至少一个第二电芯片。

22、在一些实施例中,所述基板的下表面通过第二键合结构还设置有系统集成板。

23、在一些实施例中,所述散热片的下表面、系统集成板的上表面,以及依次设置在所述散热片、系统集成板之间的光芯片、第一电芯片、基板的同侧端面共同围合形成用于设置光纤阵列的容纳空间,且所述散热片的下表面对应于所述容纳空间处设置有凹槽;其中,所述光纤阵列包括:相连接的第一基片和第二基片;

24、其中,所述第一基片通过第一胶水设置在所述凹槽处,所述第二基片通过折射率匹配的第二胶水与所述光芯片的侧面相连接;所述第二基片上设置有v型槽,以用于容纳光纤并使得所述光纤与所述侧面处的感官区光耦合。

25、有益技术效果:

26、为了简化封装结构(简化工艺、降低成本),同时提升封装结构在实际应用过程中的工作稳定性,本发明提出了一种多芯片组合封装方案。

27、首先,从结构上来说,本发明采用大尺寸的芯片上承载多个小尺寸芯片的结构(如“一载多”的封装方案)。这种上小下大的设计方案在封装结构上较为简单,便于加工。并且,为了对整体计算功耗进行合理分配,本发明将下方的大芯片设置为用于完成信号输入、传输的光芯片,并将上方的至少一个芯片设置为由相变材料制备而成的光芯片,且光芯片用于完成主要的计算任务。进一步地,还将其余芯片设置为电芯片以用于对光芯片输出的计算结果进行转换、存储。

28、换个角度来看,本发明分别对封装结构的层间、层内的功能进行优化分配,将内层设置为信号传输层,外层设置为信号处理层,且在信号处理层内依次划分不同的功能区,如信号转换、数据转化以及数据存储区。

29、综上,这种位置、功能上的协同分配一方面可以简化封装结构,一方面可以确保封装结构在工作运行时整体功耗得到合理分配,减小其在运行人工智能等大数据计算时的运算压力,提升其工作稳定性及计算结果的可靠性。

30、进一步地,针对这种位置、功能优化后的封装结构(或者说,分布式芯片设置结构),本发明还提供了一种多级任务分配规则以在于对这种分布式芯片设置结构的功耗和工作稳定性进行协调与维护,既能够在一定程度上减小分散式计算形式所产生的功耗(如可以合理地调用局部芯片完成当前计算),同时结合不同功耗情况对任务进行快速合理分配,在维持计算任务有效推进的同时,确保整体结构的散热问题得到合理优化。

本文地址:https://www.jishuxx.com/zhuanli/20240822/279369.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表