一种高铝参杂超晶格碳化硅差排缺陷阻挡层的制作方法

- 国知局

- 2024-08-22 14:51:00

本发明涉及碳化硅半导体器件制作,具体是一种高铝参杂超晶格碳化硅差排缺陷阻挡层。

背景技术:

1、碳化硅半导体器件制造的过程中,mocvd外延化学气相沉积薄膜良率普遍偏低,其部分原因来自于碳化硅衬底本身缺陷密度过高导致,在单晶碳化硅的外延mocvd薄膜沉积过程中使用单晶碳化硅衬底,该单晶碳化硅衬底本身即存在10e+19缺陷差排密度,在mocvd外延化学气相沉积使用如此衬底,必出现高密度的缺陷,良率无法提升。

技术实现思路

1、本发明的目的在于提供一种高铝参杂超晶格碳化硅差排缺陷阻挡层,以解决现有技术中的问题。

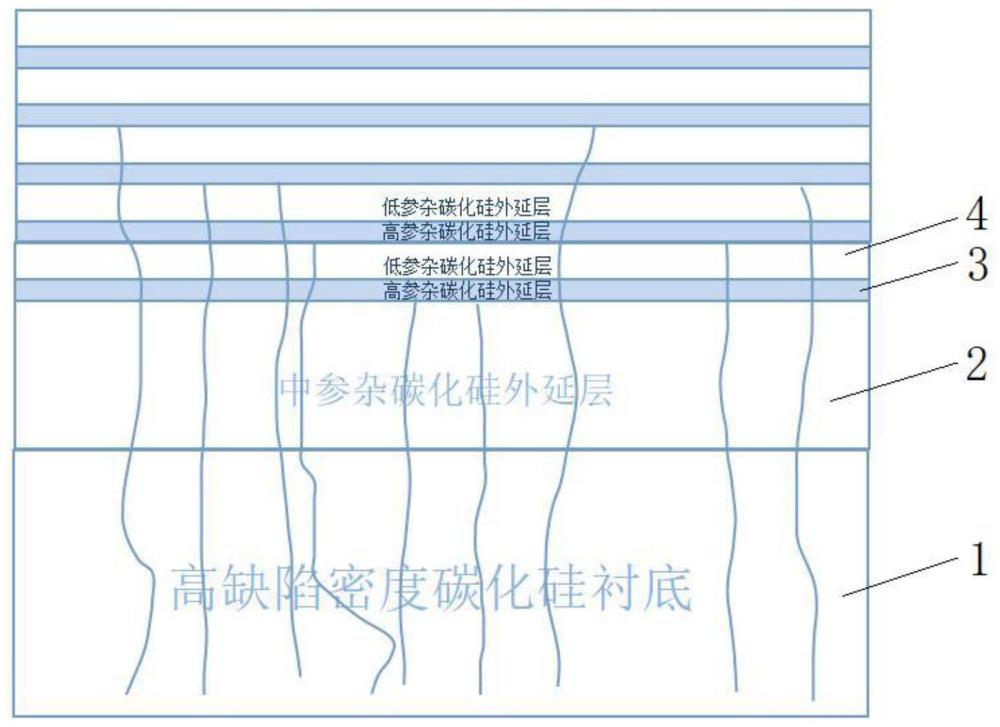

2、为实现上述目的,本发明提供如下技术方案:一种高铝参杂超晶格碳化硅差排缺陷阻挡层,包括碳化硅衬底,所述碳化硅衬底一侧设置有中参杂碳化硅外延层,所述中参杂碳化硅外延层远离碳化硅衬底一侧设置有多个高参杂碳化硅外延层和多个低参杂碳化硅外延层,所述高参杂碳化硅外延层和低参杂碳化硅外延层交替设置。

3、优选的,所述碳化硅衬底的厚度为1um。

4、优选的,所述低参杂碳化硅外延层的浓度为1.0e+16~9.0e+18个/1立方公分;所述高参杂碳化硅外延层的浓度为1.0e+21~5.0e+22个/1立方公分。

5、优选的,所述低参杂碳化硅外延层的厚度为15nm-40nm,所述高参杂碳化硅外延层的厚度为2nm-10nm。

6、优选的,所述高参杂碳化硅外延层和低参杂碳化硅外延层均设置有10-100个。

7、与现有技术相比,本发明的有益效果是:增加此高铝参杂超晶格碳化硅差排缺陷阻挡层可以降低差排密度,进而提高生产良率;使得在半导体器件的化学气相沉积制造过程中高参杂的晶格因为高参杂导致的晶格扭曲阻挡住了差排,低参杂层又将原本扭曲的晶格恢复原样更进一步提升外延层品质,如此来回进而解决薄膜成长厚度良率不佳问题。

技术特征:1.一种高铝参杂超晶格碳化硅差排缺陷阻挡层,包括碳化硅衬底(1),其特征在于:所述碳化硅衬底(1)一侧设置有中参杂碳化硅外延层(2),所述中参杂碳化硅外延层(2)远离碳化硅衬底(1)一侧设置有多个高参杂碳化硅外延层(3)和多个低参杂碳化硅外延层(4),所述高参杂碳化硅外延层(3)和低参杂碳化硅外延层(4)交替设置。

2.根据权利要求1所述的一种高铝参杂超晶格碳化硅差排缺陷阻挡层,其特征在于:所述碳化硅衬底(1)的厚度为1um。

3.根据权利要求1所述的一种高铝参杂超晶格碳化硅差排缺陷阻挡层,其特征在于:所述低参杂碳化硅外延层(4)的浓度为1.0e+16~9.0e+18个/1立方公分;所述高参杂碳化硅外延层(3)的浓度为1.0e+21~5.0e+22个/1立方公分。

4.根据权利要求1或3所述的一种高铝参杂超晶格碳化硅差排缺陷阻挡层,其特征在于:所述低参杂碳化硅外延层(4)的厚度为15nm-40nm,所述高参杂碳化硅外延层(3)的厚度为2nm-10nm。

5.根据权利要求1所述的一种高铝参杂超晶格碳化硅差排缺陷阻挡层,其特征在于:所述高参杂碳化硅外延层(3)和低参杂碳化硅外延层(4)均设置有10-100个。

技术总结本发明公开了一种高铝参杂超晶格碳化硅差排缺陷阻挡层,包括碳化硅衬底,所述碳化硅衬底一侧设置有中参杂碳化硅外延层,所述中参杂碳化硅外延层远离碳化硅衬底一侧设置有多个高参杂碳化硅外延层和多个低参杂碳化硅外延层,所述高参杂碳化硅外延层和低参杂碳化硅外延层交替设置。本发明,使得在半导体器件的化学气相沉积制造过程中高参杂的晶格因为高参杂导致的晶格扭曲阻挡住了差排,低参杂层又将原本扭曲的晶格恢复原样更进一步提升外延层品质,如此来回进而解决薄膜成长厚度良率不佳问题。技术研发人员:叶明发受保护的技术使用者:煜华(苏州)微电子设备有限公司技术研发日:技术公布日:2024/8/20本文地址:https://www.jishuxx.com/zhuanli/20240822/280112.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。