一种三维半导体集成电路器件及其制造方法与流程

- 国知局

- 2024-09-05 14:29:51

本发明涉及微电子,尤其涉及一种三维半导体集成电路器件及其制造方法。

背景技术:

1、在过去40年中,集成电路(ic)的功能和性能有了显著增长,主要是由于缩放,其中,借助相继的每一代技术减小(缩放)了ic内的部件尺寸。借助缩放,通常改善了晶体管性能和密度,但将晶体管连接在一起的线路(互连)使得性能劣化。线路常常支配ic的性能、功能和功耗。

2、存储器件通常被提供作为计算机或其它电子设备中的内部半导体集成电路器件。存储器件的典型例子包括随机存取存储器(ram,random access memory)、只读存储器(rom,read only memory)、随机动态存取存储器(dram,dynamic ram)、同步随机动态存取存储器(sdram,synchronous dram)、闪存存储器(flash memory)、和可变电阻式存储器件。可变电阻式存储器件包括可编程导电存储器件、电阻式随机存取存储器(reram,resistiveram)、和相变随机存取存储器(pcram,phase-change ram)。

3、可变电阻式存储器件可以包括多个排行成矩阵形式的存储器单元。所述存储器单元可以包括存取器件(诸如二极管)、场效晶体管(fet,field effect transistor)、或双极型结晶体管(bjt,bipolar junction transistor)。存取器件可以耦接至沿阵列的行延伸的字线。在存储器单元中的存储元件可以耦接至沿阵列的列延伸的位线。以这种方式,存储器单元的存取器件可以选择耦接至栅极的字线,并且存储器单元可以通过激活存储器单元的行行解码器而被存取。

4、目前,具有三维垂直沟道结构的晶体管被用作存储器单元的存取器件,以增大集成密度。如所公知的,具有三维垂直沟道结构的晶体管可以包括柱状有源区域、被形成在有源区域的外周之上的栅极、被形成在有源区域的上部的漏极、和被形成在有源区域的下部或被形成在与有源区域的下部接触的半导体衬底中的源极。加热电极、可变电阻层、和位线依序被形成,以被电耦接至晶体管的漏极,并且因此电阻式存储器单元被完成。

5、半导体芯片(管芯)的连续3d(三维)集成是解决线路性能的一个途径。通过在三维而不是在二维中布置晶体管,可以将ic晶体管彼此放置得更为接近。这减小了线路长度,并减小了信号延迟。但对于3d集成芯片的实际实现方式存在许多阻碍。一个此类阻碍是ic中的晶体管构造通常需要高温(高于约700℃),而在低温(低于约450℃)构成布线层。当暴露于高于约500℃的温度时,铜或铝布线层会受损。

技术实现思路

1、本发明克服了现有技术的不足,提供一种三维半导体集成电路器件及其制造方法。

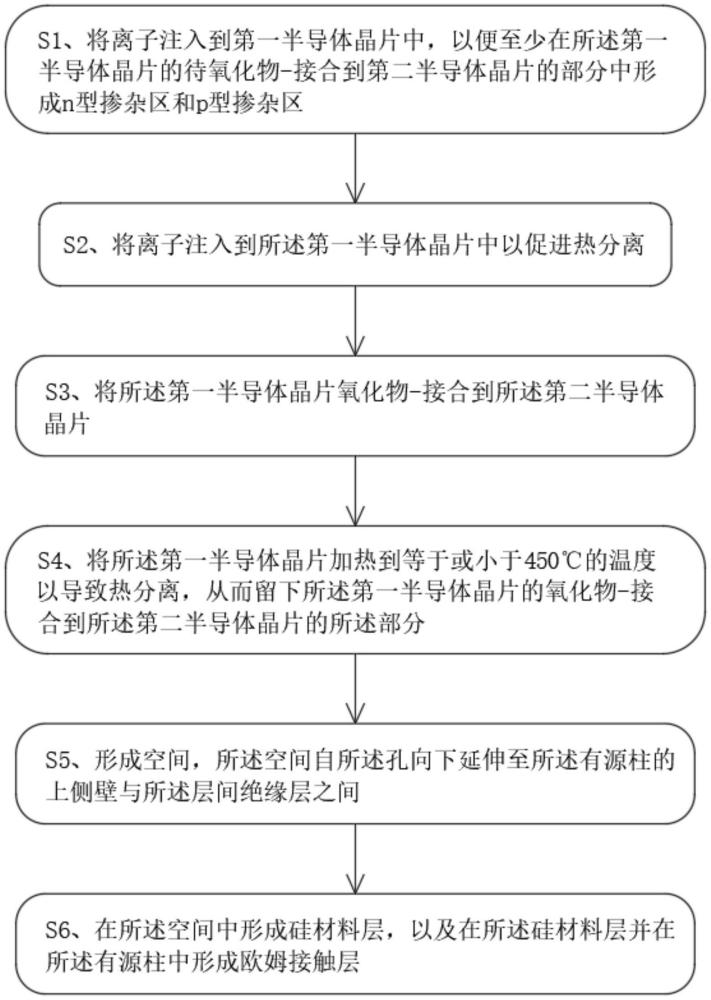

2、为达到上述目的,本发明采用的技术方案为:一种三维半导体集成电路器件的制造方法,包括以下步骤:

3、s1、将离子注入到第一半导体晶片中,以便至少在所述第一半导体晶片的待氧化物-接合到第二半导体晶片的部分中形成n型掺杂区和p型掺杂区;

4、s2、将离子注入到所述第一半导体晶片中以促进热分离;

5、s3、将所述第一半导体晶片氧化物-接合到所述第二半导体晶片;

6、s4、将所述第一半导体晶片加热到等于或小于450℃的温度以导致热分离,从而留下所述第一半导体晶片的氧化物-接合到所述第二半导体晶片的所述部分;

7、s5、形成空间,所述空间自所述孔向下延伸至所述有源柱的上侧壁与所述层间绝缘层之间;

8、s6、在所述空间中形成硅材料层,以及在所述硅材料层并在所述有源柱中形成欧姆接触层;

9、本发明一个较佳实施例中,在所述s1的步骤中,所述n型掺杂区和所述p型掺杂区包括多个纳米线晶体管的沟道。

10、本发明一个较佳实施例中,在所述s2的步骤中,所述第二半导体晶片包括底层,所述底层包括多个晶体管,其中,将所述第一半导体晶片加热到等于或小于450℃的温度以导致热分离的步骤留下了所述第一半导体晶片的氧化物-接合到所述底层的所述部分。

11、本发明一个较佳实施例中,所述多晶硅层包括未掺杂的多晶硅层。

12、本发明一个较佳实施例中,所述多晶硅层通过低温化学气相沉积cvd方法被形成。

13、本发明一个较佳实施例中,在所述s6的步骤中,所述多晶硅层包括:对所述多晶硅层执行化学机械抛光,以暴露所述层间绝缘层的上表面,其中所述层间绝缘层的上表面被定位于高于所述有源柱的上表面的水平;以及额外回蚀所述多晶硅层,使得所述多晶硅层的上表面被定位于在所述层间绝缘层的上表面与所述有源柱的上表面之间的水平。

14、本发明一个较佳实施例中,在所述s6的步骤中,所述硅材料层包括利用所述有源柱的上表面和上侧壁表面作为晶种来生长选择性外延生长seg层,使得所述选择性外延生长层延伸至所述空间中和所述孔中。

15、本发明一个较佳实施例中,所述选择性外延生长层包括杂质。

16、本发明一个较佳实施例中,还包括:在形成所述硅材料层的步骤与形成所述欧姆接触层的步骤之间,将杂质注入至所述硅材料层。

17、本发明提供一种半导体集成电路器件,所述半导体集成电路器件利用前述的制造方法获得,包括:

18、有源柱,所述有源柱自衬底向上延伸;

19、栅电极,所述栅电极被提供在所述有源柱的下侧壁之上;

20、漏极区域,所述漏极区域被形成在所述有源柱的上部中;

21、源极区域,所述源极区域被形成在有源柱的底部与邻近的有源柱的底部之间的所述衬底之中;

22、栅极绝缘层,所述栅极绝缘层被定位在所述有源柱于所述栅电极之间;

23、接触延伸区域,所述接触延伸区域自所述栅极绝缘层至在所述有源柱的上侧壁之上延伸;

24、欧姆接触层,所述欧姆接触层被形成在所述接触延伸区域中。

25、本发明解决了背景技术中存在的缺陷,本发明具备以下有益效果:

26、(1)本发明提供了一种三维半导体集成电路器件及其制造方法,在没有tsv穿硅过孔区域的不利或增大的互连信号延迟的情况下,在三维电路中组装并连接晶体管,减小用于每一个晶体管层的平均金属互连层,从而减小总互连rc延迟,减轻晶片接合对准的问题,从而允许穿过多层(半导体层)的非常准确的高密度过孔连接,实现许多核心分布式存储器架构,其利用几千个或甚至几百万个过孔三维ic和在每一层中具有高性能基本器件的架构,和通过削减金属层使用、降低缺陷密度、增大产量并降低测试成本而减小晶体管集成成本。

27、(2)本发明中选择性外延生长层被形成之后,可以在氢气的气氛中对对选择性外延生长层的表面进一步执行热处理工艺,当热处理工艺在氢气的气氛中执行时,选择性外延生长层内的杂质可以被激活,然后向上移动至选择性外延生长层的表面,因此,选择性外延生长层结束于波纹表面拓扑结构,由于选择性外延生长层的波纹表面,选择性外延生长层的表面面积显著增大。

28、(3)本发明中金属层被沉积在具有波纹表面拓扑结构的选择性外延生长层上,且经受热处理以形成的硅化物层,因此,在选择性外延生长层与硅化物层之间的接触面积可以由于选择性外延生长层的波纹表面拓扑结构而增大,并且因此选择性外延生长层与硅化物层之间的接触电阻可以降低,选择性外延生长层的拓扑结构被转移至硅化物层,并且因此硅化物层也可以具有波纹表面拓扑结构,在硅化物层与稍后被形成的下电极之间的接触面积可以增大。

本文地址:https://www.jishuxx.com/zhuanli/20240905/286770.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表