半导体器件及其制备方法与流程

- 国知局

- 2024-09-11 15:13:33

本发明涉及半导体,特别涉及一种半导体器件及其制备方法。

背景技术:

1、soi(绝缘体上硅)工艺是一种平面工艺技术,依赖于两项主要技术创新: 首先,在衬底上面制作一个绝缘层,又称埋氧层;其次用一个硅膜制作晶体管沟道,因为沟道非常薄,无需对通道进行掺杂工序。从结构上看,soi晶体管的静电特性优于传统体硅技术,包括:soi晶体管的埋氧层可以降低源极和漏极之间的寄生电容,还能有效地抑制电子从源极流向漏极,从而大幅降低导致性能下降的漏电流;此外,soi晶体管还具有许多其他方面的独特优点,包括具有背面偏置能力、极好的晶体管匹配特性、可使用接近阈值的低电源电压、对辐射具有超低的敏感性以及具有非常高的晶体管本征工作速度等。

2、 soi工艺优势在于栅极对沟道的更好控制,从而减少短沟道效应,最终无需掺杂来弥补vth值(阈值电压)的下降,或者至少可以将掺杂浓度降至较低水平,这可以提高载流子的迁移率,因为载流子和杂质之间的散射(由于掺杂)被阻止了,它还能减少随着杂质数量的增加而出现的随机掺杂波动引起的vth 波动。

3、但是,随着市场对半导体器件的要求越来越高以及半导体器件尺寸的缩减,需要进一步提升栅极对沟道的控制能力,以减少漏电问题。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制备方法,以提升栅极对沟道的控制能力。

2、为了实现上述目的以及其他相关目的,本发明提供了一种半导体器件的制备方法,包括以下步骤:

3、提供一soi衬底,所述soi衬底从下至上依次包括基底层、埋氧层以及半导体层;

4、去除至少第一方向上部分soi衬底,露出所述埋氧层的上表面以及半导体层的两个第二方向的侧面,所述第二方向与所述第一方向垂直,所述第一方向为有源区的宽度方向;

5、形成栅极于所述半导体层的上表面以及露出的侧面上。

6、可选的,在所述的半导体器件的制备方法中,所述soi衬底还包括位于所述半导体层上的牺牲氧化层,所述形成栅极于所述半导体层的上表面以及露出的侧面上的步骤之前,所述制备方法还包括:去除所述牺牲氧化层,露出所述半导体层的上表面。

7、可选的,在所述的半导体器件的制备方法中,所述去除至少第一方向上部分soi衬底的步骤包括:

8、形成光刻胶层于所述soi衬底上;

9、执行光刻工艺,以形成图案化的光刻胶层,所述图案化的光刻胶层露出至少第一方向上部分所述soi衬底;

10、执行刻蚀工艺,利用所述图案化的光刻胶层为掩膜去除部分soi衬底,露出所述埋氧层的上表面以及半导体层的两个第二方向的侧面。

11、可选的,在所述的半导体器件的制备方法中,所述形成栅极于所述半导体层的上表面以及露出的侧面上的步骤之前,所述制备方法还包括:形成栅极氧化层于所述半导体层的上表面以及露出的侧面上。

12、可选的,在所述的半导体器件的制备方法中,所述soi衬底还包括浅沟槽隔离结构,所述浅沟槽隔离结构包围的区域为所述有源区,所述栅极还沿着所述第一方向延伸至所述浅沟槽隔离结构上。

13、可选的,在所述的半导体器件的制备方法中,所述形成栅极于所述半导体层的上表面以及露出的侧面上的步骤之后,所述制备方法还包括:形成源极和漏极于所述栅极两侧的有源区中。

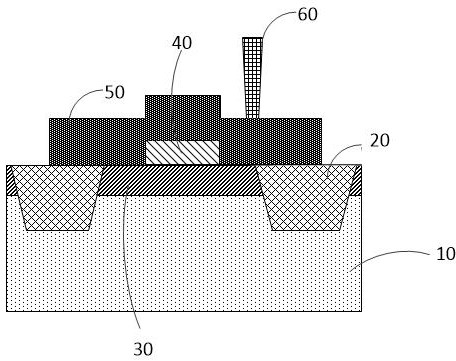

14、为了实现上述目的以及其他相关目的,本发明还提供了一种半导体器件,从下至上依次包括:soi衬底和栅极,所述soi衬底从下至上依次包括:基底层、埋氧层以及半导体层,其中,第一方向上部分soi衬底被去除露出所述埋氧层的上表面以及半导体层的两个第二方向的侧面,所述栅极位于所述半导体层的上表面以及两个第二方向的侧面上,所述第二方向与所述第一方向垂直,所述第一方向为有源区的宽度方向。

15、可选的,在所述的半导体器件中,所述栅极的材料包括纯的多晶硅或者掺杂的多晶硅,且掺杂的多晶硅中掺杂的元素包括硼或者磷;和/或,所述半导体层的材料包括硅。

16、可选的,在所述的半导体器件中,所述soi衬底还包括浅沟槽隔离结构,所述浅沟槽隔离结构包围的区域为所述有源区,所述栅极还沿着第一方向延伸至所述浅沟槽隔离结构上。

17、可选的,在所述的半导体器件中,所述半导体器件还包括栅极氧化层,且所述栅极氧化层位于所述栅极与所述半导体层之间。

18、可选的,在所述的半导体器件中,至少部分所述浅沟槽隔离结构的上表面与所述埋氧层的上表面齐平。

19、与现有技术相比,本发明的技术方案具有以下意想不到的有益效果:

20、本发明提供的半导体器件及其制备方法中,通过光刻和刻蚀工艺去除至少第一方向上部分soi衬底,露出半导体层的两个第二方向的侧面,栅极将半导体层的上表面和第二方向的侧面包裹,可以增加栅极对沟道的控制面积,进而可以增大栅极对沟道的控制能力,减少漏电流,提升器件性能。

技术特征:1.一种半导体器件的制备方法,其特征在于,包括以下步骤:

2.如权利要求1所述的半导体器件的制备方法,其特征在于,所述soi衬底还包括位于所述半导体层上的牺牲氧化层,所述形成栅极于所述半导体层的上表面以及露出的侧面上的步骤之前,所述制备方法还包括:去除所述牺牲氧化层,露出所述半导体层的上表面。

3.如权利要求1所述的半导体器件的制备方法,其特征在于,所述去除至少第一方向上部分soi衬底的步骤包括:

4.如权利要求1所述的半导体器件的制备方法,其特征在于,所述形成栅极于所述半导体层的上表面以及露出的侧面上的步骤之前,所述制备方法还包括:形成栅极氧化层于所述半导体层的上表面以及露出的侧面上。

5.如权利要求1所述的半导体器件的制备方法,其特征在于,所述soi衬底还包括浅沟槽隔离结构,所述浅沟槽隔离结构包围的区域为所述有源区,所述栅极还沿着所述第一方向延伸至所述浅沟槽隔离结构上。

6.如权利要求5所述的半导体器件的制备方法,其特征在于,所述形成栅极于所述半导体层的上表面以及露出的侧面上的步骤之后,所述制备方法还包括:形成源极和漏极于所述栅极两侧的有源区中。

7.一种半导体器件,其特征在于,从下至上依次包括:soi衬底和栅极,所述soi衬底从下至上依次包括:基底层、埋氧层以及半导体层,其中,第一方向上部分soi衬底被去除露出所述埋氧层的上表面以及半导体层的两个第二方向的侧面,所述栅极位于所述半导体层的上表面以及两个第二方向的侧面上,所述第二方向与所述第一方向垂直,所述第一方向为有源区的宽度方向。

8.如权利要求7所述的半导体器件,其特征在于,所述栅极的材料包括纯的多晶硅或者掺杂的多晶硅,且掺杂的多晶硅中掺杂的元素包括硼或者磷;和/或,所述半导体层的材料包括硅。

9.如权利要求7所述的半导体器件,其特征在于,所述soi衬底还包括浅沟槽隔离结构,所述浅沟槽隔离结构包围的区域为所述有源区,所述栅极还沿着第一方向延伸至所述浅沟槽隔离结构上。

10.如权利要求7所述的半导体器件,其特征在于,所述半导体器件还包括栅极氧化层,且所述栅极氧化层位于所述栅极与所述半导体层之间。

11.如权利要求7所述的半导体器件,其特征在于,至少部分所述浅沟槽隔离结构的上表面与所述埋氧层的上表面齐平。

技术总结本发明提供了一种半导体器件及其制备方法,通过去除至少第一方向上部分SOI衬底,露出半导体层的两个第二方向的侧面,并形成栅极于半导体层的上表面以及侧面上,可以增加栅极对沟道的控制面积,进而可以增大栅极对沟道的控制能力,减少漏电流,提升器件性能。技术研发人员:田国军,张伟光,高志强,王同信,郑重受保护的技术使用者:武汉新芯集成电路股份有限公司技术研发日:技术公布日:2024/9/9本文地址:https://www.jishuxx.com/zhuanli/20240911/293621.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表