半导体器件及其制造方法与流程

- 国知局

- 2024-09-14 14:27:56

本公开涉及一种半导体器件及其制造方法,并且可以适当地用于例如包括反熔丝元件的半导体器件及其制造方法。

背景技术:

1、作为包括由形成在半导体衬底上的半导体元件形成的存储器的半导体器件,存在以下半导体器件,该半导体器件包括具有反熔丝元件的存储器单元。在该半导体器件中,高电压被施加在反熔丝元件的栅极电极与源极区域及漏极区域之间,以使反熔丝元件的栅极电介质膜击穿,由此数据被写入到存储器单元。在栅极电介质膜被击穿的反熔丝元件中,栅极泄漏电流增加。因此,信息(“0”或“1”)可以通过向栅极电极施加读取电压并且测量栅极电极与源极区域和漏极区域之间的读取电流来进行确定。即,指示足够读取电流值(等于或大于确定基准值)的存储器单元被确定为例如信息“1”。

2、下面列出了公开的技术。

3、[专利文献1]日本未审查专利申请公开号2011-119640

4、此外,由于反熔丝元件中的栅极电介质膜的击穿仅一次,因此存储器单元的写入被称为otp(one time program)。此外,包括反熔丝元件的存储器元件被称为otp存储器元件,并且被用于rom(只读存储器)。例如,专利文献1公开了一种反熔丝元件。

技术实现思路

1、本申请的发明人已经确认,在包括存储器单元(其包括具有mos结构的反熔丝元件(在下文中被称为熔丝晶体管))的半导体器件中存在以下问题。

2、半导体器件被内置到芯片中。在半导体器件的制造步骤中,使用其中大量半导体芯片以矩阵形式布置的半导体晶片(例如,300mm直径的盘)。制造步骤包括诸如光刻、导电膜和电介质膜的沉积、蚀刻、以及抛光(cmp(化学机械抛光))的步骤。在每个制造步骤中,不能以相同的处理准确性对半导体晶片中的所有半导体芯片进行处理,并且半导体晶片中出现被称为“面内变化”的处理变化。“面内变化”是由半导体芯片的布置位置上的差异引起的处理变化。例如,在布置在半导体晶片的中心部分中的半导体芯片与布置在外围部分中的半导体芯片之间,出现相对于设计值的最终尺寸误差。

3、本申请的发明人已经确认,指示读取电流不足的存储器单元(被称为“缺陷位”)出现在包括具有熔丝晶体管的存储器单元的半导体器件中。继而,发明人已经确认,缺陷位的产生原因是半导体器件的制造步骤中的“面内变化”。在包括具有熔丝晶体管的存储器单元的半导体器件中,需要对存储器单元的读取电流的改进。其他目的和新颖特征将从本说明书的描述和附图变得明显。

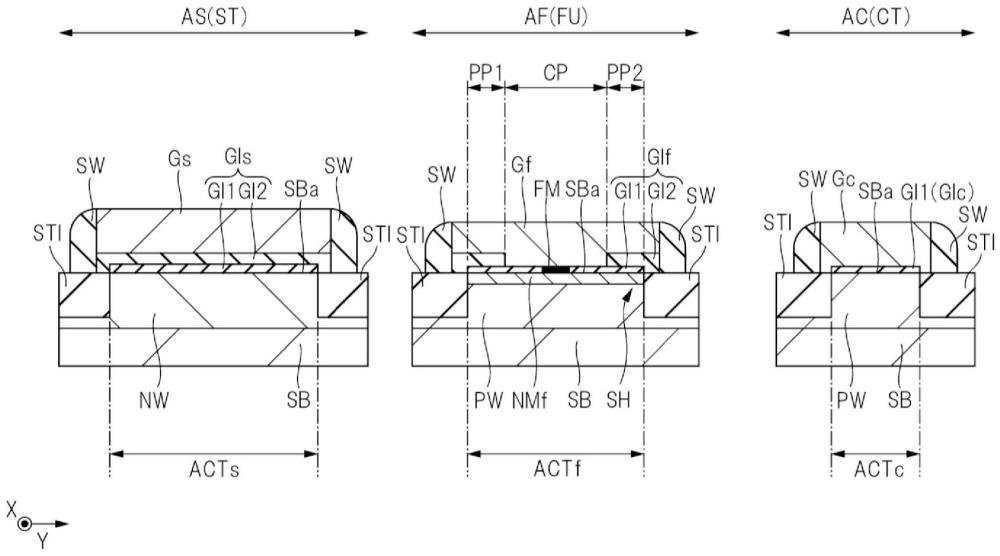

4、在一个实施例中,半导体器件包括具有主表面的半导体衬底以及第一元件隔离膜和第二元件隔离膜,第一元件隔离膜和第二元件隔离膜被布置成在沿着主表面的第一方向上将半导体衬底的部分夹在中间以限定第一有源区,并且分别从主表面朝向半导体衬底的内部延伸。在平面图中,半导体器件包括形成在第一有源区中的第一晶体管。第一晶体管包括形成在半导体衬底的主表面上的第一栅极电介质膜,并且包括形成在第一栅极电介质膜上的第一栅极电极。第一晶体管还包括第一半导体区域和第二半导体区域,第一半导体区域和第二半导体区域在垂直于第一方向的第二方向上位于第一栅极电极的两侧,并且形成在半导体衬底中。在第一方向上,第一栅极电介质膜包括被布置成与第一元件隔离膜和第二元件隔离膜间隔开的第一部分、被布置在第一部分与第一元件隔离膜之间的第二部分、以及被布置在第一部分与第二元件隔离膜之间的第三部分。第一栅极电介质膜的第二部分到达第一元件隔离膜,并且第一栅极电介质膜的第三部分到达第二元件隔离膜。此外,第一栅极电介质膜的第一部分具有第一厚度,并且第一栅极电介质膜的第二部分和第三部分中的每一者具有第二厚度,第二厚度大于第一厚度。

5、在一个实施例中,一种半导体器件的制造方法包括:制备具有主表面的半导体衬底;以及形成第一元件隔离膜和第二元件隔离膜,第一元件隔离膜和第二元件隔离膜分别从主表面朝向半导体衬底的内部延伸,并且被布置成在沿着主表面的第一方向上将半导体衬底的主表面的一个区域夹在中间,以限定第一有源区。半导体器件的制造方法还包括:在半导体衬底的主表面上形成第一栅极电介质膜,以及在第一有源区中的第一栅极电介质膜上形成第一栅极电极。半导体器件的制造方法还包括:在第一有源区中的半导体衬底中、在与第一方向垂直的第二方向上的第一栅极电极的两侧形成第一半导体区域和第二半导体区域。第一栅极电介质膜包括被布置成与第一元件隔离膜和第二元件隔离膜间隔开的第一部分、被布置在第一部分与第一元件隔离膜之间的第二部分、以及被布置在第一部分与第二元件隔离膜之间的第三部分。然后,栅极电介质膜的第二部分到达第一元件隔离膜,并且第一元件隔离膜的第三部分到达第二元件隔离膜。并且,第一栅极电介质膜的第一部分具有第一厚度,并且第一栅极电介质膜的第二部分和第三部分中的每一者具有第二厚度,并且第二厚度大于第一厚度。

6、根据实施例,改进读取电流可以改进半导体器件的可靠性。

技术特征:1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,

3.根据权利要求1所述的半导体器件,

4.根据权利要求1所述的半导体器件,

5.根据权利要求4所述的半导体器件,

6.根据权利要求4所述的半导体器件,包括:

7.根据权利要求6所述的半导体器件,包括:

8.根据权利要求7所述的半导体器件,

9.根据权利要求8所述的半导体器件,

10.根据权利要求1所述的半导体器件,

11.一种制造半导体器件的方法,所述方法包括:

12.根据权利要求11所述的方法,

13.根据权利要求11所述的方法,

14.根据权利要求11所述的方法,

15.根据权利要求14所述的方法,

16.根据权利要求14所述的方法,

17.根据权利要求16所述的方法,

18.根据权利要求11所述的方法,

19.根据权利要求11所述的方法,

20.根据权利要求19所述的方法,

技术总结本公开涉及一种半导体器件及其制造方法,其中半导体器件包括形成在有源区中的熔丝晶体管。在第一方向上,有源区由第一元件隔离膜和第二元件隔离膜限定。熔丝晶体管包括栅极电介质膜、栅极电极和半导体区域,半导体区域在与第一方向垂直的第二方向上形成在栅极电极的两侧。在第一方向上,栅极电介质膜具有中心部分、第一外围部分和第二外围部分。中心部分与第一元件隔离膜和第二元件隔离膜间隔开,第一外围部分到达第一元件隔离膜,并且第二外围部分到达第二元件隔离膜。栅极电介质膜的中心部分具有第一厚度,并且第一外围部分和第二外围部分中的每一者具有大于第一厚度的第二厚度。技术研发人员:平岩英治,长井大诚,清水秀,奈仓健受保护的技术使用者:瑞萨电子株式会社技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/294214.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表