一种双沟槽结构的高压MOSFET器件及制造方法与流程

- 国知局

- 2024-09-19 14:37:24

本发明涉及半导体器件,尤其涉及一种双沟槽结构的高压mosfet器件及制造方法。

背景技术:

1、目前,在现有的技术领域,击穿电压是衡量mosfet器件性能的主要参数,是工程师选用产品的重要指标之一。通常mosfet器件其击穿电压越高,导通电阻就越高,单胞的设计尺寸也越大,这些主要受到原材料规格以及产品设计原则的限制。

2、通常,在高压mosfet器件(通常指额定电压≥300v的产品)中,多数上采用平面型结构的设计方式,导致芯片整体设计尺寸较大,且尺寸较大的高压mosfet器件的结构集成化不理想,导致芯片有效图形较少。

3、有鉴于此,有必要提出对目前的双沟槽结构的高压mosfet器件结构进行进一步的改进。

技术实现思路

1、为此,本发明目的在于至少一定程度上解决现有技术中的不足,从而提出一种双沟槽结构的高压mosfet器件及制造方法。

2、为实现上述目的,本发明采用的一个技术方案为:

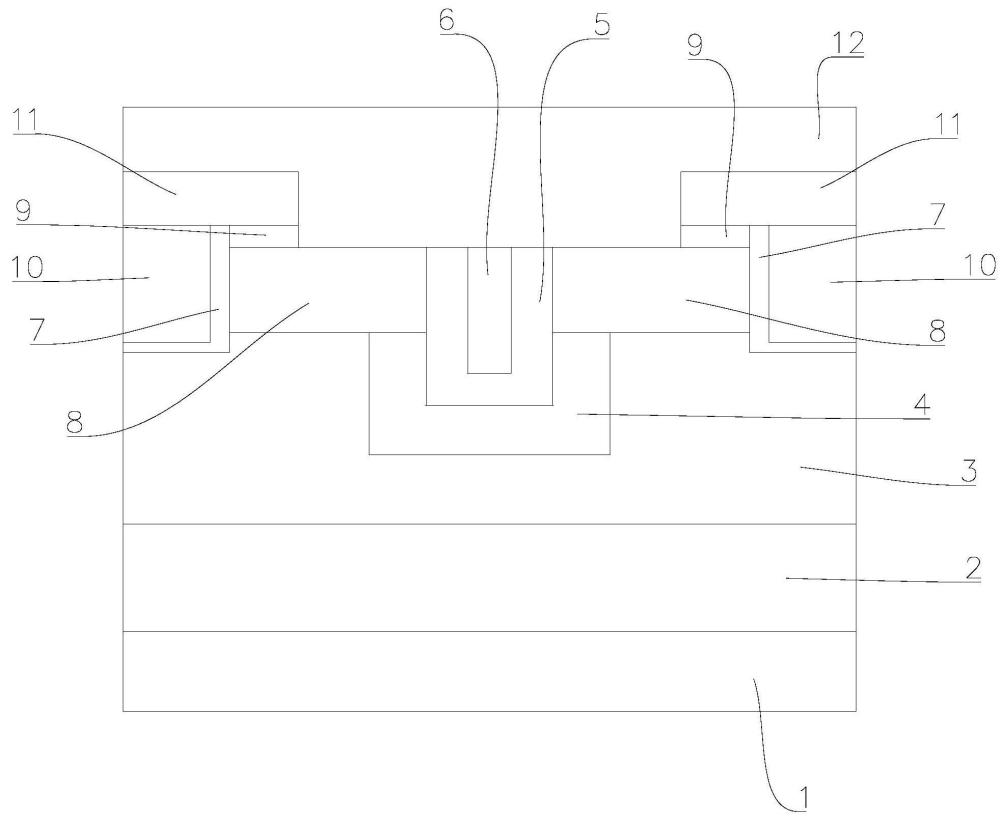

3、本发明提供了一种双沟槽结构的高压mosfet器件,包括依次层叠设置的n+衬底、第一n-外延层、第二n-外延层、p+掩蔽层、第一trench槽、源极、n+层、绝缘层、金属层,所述第一trench槽的两侧分别设置有pwell区,且两个所述pwell区远离所述第一trench槽的两侧还分别设置有第二trench槽,所述pwell区的一端连接有所述第二n-外延层和所述p+掩蔽层,另一端连接有所述n+层和所述金属层,两个所述第二trench槽远离所述pwell区的两侧还设置有栅极,所述栅极还与所述绝缘层连接,所述栅极和所述源极的成分均包括多晶硅。

4、进一步地,所述高压mosfet器件的宽度为6.5-8.5μm。

5、进一步地,所述第一trench槽的宽度为1-2μm,深度为4-5μm。

6、进一步地,所述第二trench槽的宽度为0.5-1.5μm,深度为1.5-2.5μm。

7、进一步地,所述第二trench槽的底部设置有jfet区。

8、进一步地,所述n+衬底的正面层叠设置有所述第一n-外延层和所述第二n-外延层,且所述n+衬底的正面的材质为铝,所述n+衬底的背面包括层叠设置的ti-ni-ag结构。

9、进一步地,本发明还提供了一种如上述任一项所述的双沟槽结构的高压mosfet器件的制造方法,包括如下步骤:

10、s1、在n+衬底上通过外延生长依次制备第一n-外延层和第二n-外延层;

11、s2、在所述第二n-外延层通过sio2硬掩模、光刻刻蚀的方式形成第一trench槽;

12、s3、在所述第一trench槽内采用离子注入、热氧化推结的方式形成p+掩蔽层和氧化层;

13、s4、将所述氧化层作为硬掩膜,利用光刻刻蚀的方式形成第二trench槽;

14、s5、利用化学气相沉积法对所述第一trench槽、第二trench槽进行多晶硅填充,并采用原位掺杂工艺,从而同步实现多晶硅的掺杂,形成主要成分为多晶硅的源极和栅极,再采用cmp的方式去除表面的多晶硅,进行大面积的离子注入、热氧化推结,形成pwell区;

15、s6、在所述第二n-外延层上进行大面积的离子注入形成n+层,并采用退火方式激活杂质;

16、s7、在所述第二n-外延层上利用化学气相沉积的方式进行绝缘层的生长;

17、s8、在所述绝缘层的表面沉淀形成金属层。

18、进一步地,步骤s4中,在所述第二trench槽内的底部进行大面积的磷元素的离子注入、热氧化推结,形成jfet区,并进行栅氧化层的生长。

19、进一步的,步骤s8中,采用光刻的方式实现源极窗口,采用湿法腐蚀的方式去除所述绝缘层和所述氧化层相应的厚度,再利用干法刻蚀的方式同步去除多晶硅,实现接触孔浅槽结构,所述接触孔连接所述金属层;

20、步骤s8中,采用背面减薄工艺,在所述n+衬底上的背面蒸镀ti-ni-ag结构层。

21、进一步地,步骤s1中,所述第一n-外延层原材料的掺杂浓度为1.9e14,原材料的厚度为65-70μm;所述第二n-外延层原材料的掺杂浓度为3.0e15,原材料的厚度为3-8μm;掺杂元素为磷;

22、步骤s3中,离子注入的剂量为1e13,注入能量为80kev,注入元素为硼,热氧化温度为1150℃;

23、步骤s4中,在所述第二trench槽内注入的离子剂量为2.5e12,注入能量为100kev,所述栅氧化层的厚度为1100a;

24、步骤s5中,多晶硅厚度为掺杂元素为磷,掺杂浓度为2.9e14。离子注入元素为硼,注入剂量为1.5e13,注入能量为60kev,热氧化推结温度为1150℃;

25、步骤s6中,离子注入元素为砷,注入剂量为1.0e16,注入能量为100kev,退火温度为950℃;

26、步骤s8中,所述绝缘层厚度为10000a,所述接触孔设计宽度为2-5um,接触孔浅槽设计深度为0.2-0.8um。

27、本发明提供了一种双沟槽结构的高压mosfet器件及制造方法,双沟槽结构的高压mosfet器件包括依次层叠设置的n+衬底、第一n-外延层、第二n-外延层、p+掩蔽层、第一trench槽、源极、n+层、绝缘层、金属层,所述第一trench槽的两侧分别设置有pwell区,且两个所述pwell区远离所述第一trench槽的两侧还分别设置有第二trench槽,所述pwell区的一端连接有所述第二n-外延层和所述p+掩蔽层,另一端连接有所述n+层和所述金属层,两个所述第二trench槽远离所述pwell区的两侧还设置有栅极,所述栅极还与所述绝缘层连接,所述栅极和源极的成分均包括多晶硅。通过本发明提供的高压mosfet器件设置有双沟槽结构,采用p+掩蔽和引入多晶硅的方式,实现了300v以上的耐压等级,该结构在降低了设计尺寸和生产成本的同时,使得主要参数性能与原有设计相当;其中,源极内的多晶硅起到了改善电场结构的作用,使原本纵向的电场产生了横向的电场分量,进而提升了产品的耐压能力。

技术特征:1.一种双沟槽结构的高压mosfet器件,其特征在于,包括依次层叠设置的n+衬底、第一n-外延层、第二n-外延层、p+掩蔽层、第一trench槽、源极、n+层、绝缘层、金属层,所述第一trench槽的两侧分别设置有pwell区,且两个所述pwell区远离所述第一trench槽的两侧还分别设置有第二trench槽,所述pwell区的一端连接有所述第二n-外延层和所述p+掩蔽层,另一端连接有所述n+层和所述金属层,两个所述第二trench槽远离所述pwell区的两侧还设置有栅极,所述栅极还与所述绝缘层连接,所述栅极和所述源极的成分均包括多晶硅。

2.根据权利要求1所述的双沟槽结构的高压mosfet器件,其特征在于,所述高压mosfet器件的宽度为6.5-8.5μm。

3.根据权利要求1所述的双沟槽结构的高压mosfet器件,其特征在于,所述第一trench槽的宽度为1-2μm,深度为4-5μm。

4.根据权利要求1所述的双沟槽结构的高压mosfet器件,其特征在于,所述第二trench槽的宽度为0.5-1.5μm,深度为1.5-2.5μm。

5.根据权利要求1所述的双沟槽结构的高压mosfet器件,其特征在于,所述第二trench槽的底部设置有jfet区。

6.根据权利要求1所述的双沟槽结构的高压mosfet器件,其特征在于,所述n+衬底的正面层叠设置有所述第一n-外延层和所述第二n-外延层,且所述n+衬底的正面的材质为铝,所述n+衬底的背面包括层叠设置的ti-ni-ag结构。

7.一种如权利要求1-6任一项所述的双沟槽结构的高压mosfet器件的制造方法,其特征在于,包括如下步骤:

8.根据权利要求7所述的制造方法,其特征在于,

9.根据权利要求8所述的制造方法,其特征在于,

10.根据权利要求9所述的制造方法,其特征在于,

技术总结本发明公开了一种双沟槽结构的高压MOSFET器件及制造方法,高压MOSFET器件包括依次层叠设置的N+衬底、第一N‑外延层、第二N‑外延层、P+掩蔽层、第一Trench槽、源极、N+层、绝缘层、金属层,第一Trench槽的两侧分别设置有Pwell区,且两个Pwell区两侧还分别设置有第二Trench槽,Pwell区的一端连接有第二N‑外延层和P+掩蔽层,另一端连接有N+层和金属层,两个第二Trench槽远离Pwell区的两侧还设置有栅极,栅极和源极的成分均包括多晶硅。通过设置双沟槽,采用P+掩蔽和引入多晶硅的方式,实现了300V以上的耐压等级,在降低设计尺寸和生产成本的同时,使得主要参数性能与原有设计相当;源极内的多晶硅起到改善电场结构的作用,使原本纵向的电场产生了横向的电场分量,进而提升了产品的耐压能力。技术研发人员:张熠鑫,苏晓山,宋炟,张雨欣,贾国,刘少博,任强受保护的技术使用者:深圳吉华微特电子有限公司技术研发日:技术公布日:2024/9/17本文地址:https://www.jishuxx.com/zhuanli/20240919/299212.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表