一种沟槽型SiC场效应晶体管及制备方法与流程

- 国知局

- 2024-09-19 14:42:40

本发明涉及半导体,尤其涉及一种沟槽型sic场效应晶体管及制备方法。

背景技术:

1、以碳化硅(sic)为代表的第三代宽禁带半导体材料,由于材料本身具备临界击穿场强大、本征载流子浓度低、饱和电子漂移速率快、热导率大等优异的物理特性,因此以sic为半导体材料制备的金属-氧化物-半导体场效应晶体管(mosfet)能够在高压、高温、高频、高辐照等领域获得优越的器件性能。尤其是随着新能源汽车、光伏等领域的快速发展,传统硅基功率器件已经接近了材料本身所限定的性能极限,无法满足这些应用领域提出的更加严苛的使用要求,使得sic功率器件已开始逐步替代硅基功率器件,未来将不再是以硅基功率器件唯一的市场格局。

2、sic mosfet器件在长期使用过程中具有两个明显缺点:

3、(1)sic mosfet器件的栅氧化层的早期击穿失效概率大,尤其是沟槽型sicmosfet器件,由于sic/sio2的界面态密度大,缺陷多从而导致栅氧化层质量差,且沟槽型栅氧由于曲率效应在底部拐角处也更容易引起电场集中,更加剧了击穿失效速率。

4、(2)常规的sic mosfet器件会集成反并联的pn结体二极管以实现对器件的续流保护,但是续流过程中p区空穴会进入到n型漂移层中,从而引起空穴和电子的复合导致漂移层中的晶格缺陷蔓延,最终使器件发生双极退化现象从而性能恶化。

5、综上两点缺点,沟槽型sic mosfet在长期使用过程中,栅氧化层的提早击穿失效和pn 结体二极管引起的双极退化效应,均对器件的可靠性提出了挑战,极大的影响了器件的大规模稳定使用,因此如何改善沟槽型 si mosfet 器件的栅氧化层使用可靠性和双极退化效应对于器件的长期使用是至关重要的。

6、现有专利文献中,如2023年06月23日申请公布的一篇“沟槽型mos场效应晶体管的制备方法和应用”发明专利,授权公告号为cn 116313809 b。其制备方法:在半导体衬底层上依次形成n型半导体外延层、阱区和掺杂区;在掺杂区的中间区域的两侧分别刻蚀一个虚拟沟槽,向虚拟沟槽的底部注入p型杂质,形成p+层;在掺杂区的中间区域刻蚀一个栅极沟槽;向虚拟沟槽的内部填充氧化物;在掺杂区远离n型半导体外延层的一侧形成金属层。该专利文献,虽然通过沟槽底部的p+层改善了沟槽栅氧底部拐角的电场集中,但是mos中的寄生体二极管仍然为pn结二极管,在器件续流过程中存在着续流损耗大以及双极退化效应等问题。

技术实现思路

1、针对以上问题,本发明提供了一种避免栅氧化层的早期击穿失效,提高栅氧化层的使用可靠性,并且在器件续流过程中,将原本pn结体二极管续流改为sbd续流,避免了p区空穴进入到n型漂移层中,提高器件的长期使用可靠性的一种沟槽型sic场效应晶体管及制备方法。

2、本发明的技术方案是:

3、一种沟槽型sic场效应晶体管制备方法,包括如下步骤:

4、s100,在碳化硅epi层上通过离子注入初步形成浅掺杂的p-body体区;

5、s200,在p-body体区的上表面通过离子注入初步形成重掺杂的n+区;

6、s300,在n+区的顶面通过刻蚀向下形成第一沟槽区;

7、s400,在第一沟槽区的底面通过离子注入初步形成重掺杂的p+区;

8、s500,通过高温激活退火使p-body体区、n+区和p+区完全形成;

9、s600,在epi层上通过刻蚀形成第二沟槽区;

10、s700,在第二沟槽区的内壁通入o2,利用干氧氧化方式生长一层栅氧化层;

11、s800,在第二沟槽区内部通过多晶硅淀积方式形成一层poly层,作为器件的门电极使用;

12、s900,在n+区和第二沟槽区的顶面通过氧化物淀积方式形成一层隔离介质层,作为器件隔离门电极和源电极的绝缘层使用;

13、s1000,在n+区的顶面和第一沟槽区内通过ni金属溅射方式形成一层ni金属层,后通过合金化退火形成一层正面欧姆合金层;

14、s1100,在器件上方通过al金属溅射方式形成一层正面电极金属,作为器件的源电极使用;

15、s1200,在epi层的底面通过ni金属溅射方式形成一层ni金属层,后通过激光退火形成背面欧姆合金层;

16、s1300,在背面欧姆合金层的底面形成一层背面电极金属,作为器件的漏电极使用。

17、具体的,步骤s100中浅掺杂的p-body体区注入离子为al离子,掺杂浓度在1e17cm-2-1e18cm-2。

18、具体的,步骤s200中重掺杂的n+区注入离子为n离子,掺杂浓度在1e18cm-2-1e19cm-2。

19、具体的,步骤s400中的重掺杂的p+区注入离子为al离子,掺杂浓度在1e17cm-2-1e18cm-2。

20、具体的,步骤s1000中的ni金属厚度为100nm。

21、具体的,步骤s1100中的正面电极金属厚度为5000nm。

22、具体的,步骤s1200中的ni金属厚度在100nm。

23、具体的,步骤s1300中背面欧姆合金层的底面通过ti/ni/ag或ni/pd/au金属蒸发方式形成一层背面电极金属;

24、ti/ni/ag或ni/pd/au金属厚度在30nm/300nm/1200nm。

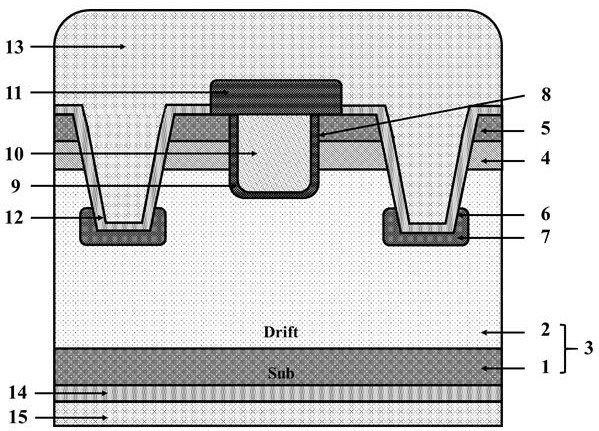

25、一种沟槽型sic场效应晶体管,包括从下而上依次设置的背面电极金属、背面欧姆合金层、epi层和正面电极金属;

26、所述epi层上设有:

27、p-body体区,从所述epi层的顶面向下延伸;

28、n+区,从所述p-body体区的顶面向下延伸;

29、第一沟槽区,从所述n+区的顶面向下延伸至p-body体区的下方;

30、p+区,从所述第一沟槽区的槽底向下延伸,并与所述第一沟槽区的槽底的拐角连接;

31、第二沟槽区,从所述n+区的顶面向下延伸至p-body体区的下方;所述第二沟槽区的槽底位于第一沟槽区槽底的上方;

32、栅氧化层,设置在所述第二沟槽区的槽壁和槽底上;

33、poly层,填充在所述第二沟槽区内,与所述栅氧化层连接;

34、隔离介质层,位于所述第一沟槽区顶部,分别与所述n+区、第二沟槽区和poly层连接;

35、正面欧姆合金层,从所述n+区的顶面向第一沟槽区的槽底延伸,底部与所述p+区连接,顶部的侧边与所述隔离介质层连接。

36、具体的,所述正面电极金属底部延伸至第一沟槽区内,与所述正面欧姆合金层连接。

37、本发明在沟槽型sic mosfet器件中设有两个沟槽区,其中采用第一沟槽区的重掺杂p+区对第二沟槽区的栅氧化层实现保护,通过p+区与n型漂移层之间的空间耗尽层来降低沟槽栅氧底部拐角的电场集中,避免了栅氧化层的早期击穿失效,从而提高栅氧化层的使用可靠性。同时本发明在第一沟槽区的侧壁上集成了sbd结构,在器件续流过程中,将原本pn结体二极管续流改为从sbd续流,避免了p区空穴进入到n型漂移层中,从而避免了器件的双极退化效应发生,提高器件的长期使用可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240919/299770.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表