一种用于晶体管垂直堆叠的集成方法

- 国知局

- 2024-10-09 15:44:44

本发明涉及半导体器件制备领域,尤其是晶体管的垂直集成。

背景技术:

1、半个世纪以来,硅基晶体管的尺寸在不断的缩小,单芯片上晶体管的数量呈指数式增长,芯片的性能得到大幅的提高。通过先进的光刻技术减小晶体管的横向尺寸,从而将更多的晶体管集成到芯片上,是当前晶体管密度提升的主要方式。随着硅基晶体管进入亚5nm节点,出现越来越多的技术难题,探索新的器件结构对进一步增加晶体管集成密度和延续摩尔定律具有重要意义。晶体管的垂直集成,增加了芯片表面的利用效率,有望在不依赖高精度光刻技术的情况下实现高集成密度,为集成电路的发展开辟一个新的维度。

2、然而,到目前为止,晶体管的垂直集成仍然非常具有挑战性,因为传统平面工艺与垂直结构的不兼容。当前制造一层晶体管至少需要四步工艺,即首先制备底部的半导体沟道材料,沉积源漏电极之后再生长中间的介电层,最后制备顶部的电极。当在垂直方向制备多个晶体管时,这些工艺需要不断重复,从而导致复杂、低产量和不可拓展的制造过程。因而,当前最先进的晶体管垂直集成技术只限于在垂直方向上几层器件的演示,从而严重限制了晶体管垂直集成的实际应用。这与平面集成电路技术相比形成了巨大的反差,因为后者中的平面晶体管可以进行批量的制造。这种差异来源于传统平面工艺中自上而下的制备过程,如光刻中的光子、刻蚀中的反应离子以及蒸发中的蒸气原子等物理粒子,它们只能在芯片平面内产生结构,难以直接应用于垂直基底。因此,发展一种可以垂直产生多个器件结构的方法,对于高密度集成电路的发展具有重要意义。

技术实现思路

1、本发明所要解决的技术问题是克服传统平面工艺与垂直结构的不兼容性,提供一种简单的垂直堆叠晶体管的方法。

2、本发明所采用的技术方案如下:一种用于晶体管垂直堆叠的集成方法,包括以下步骤:

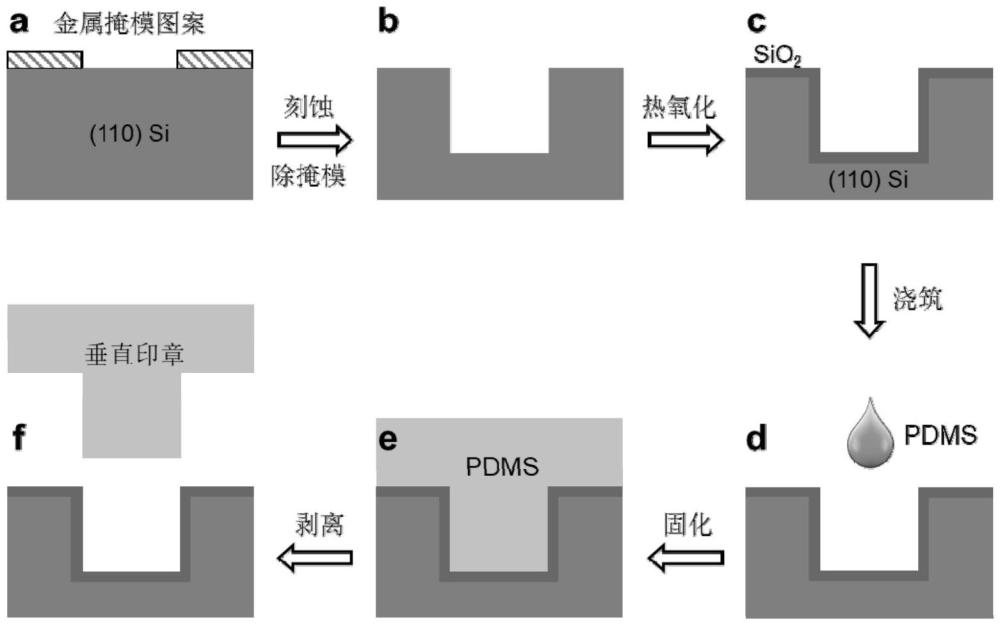

3、(1)在刚性基底上制备掩模图案,通过刻蚀、除去掩模和生长介电层,形成表面覆盖介电层的垂直凹槽;

4、(2)配置橡胶溶液,静置后浇筑在所述垂直凹槽上,加热固化并剥离,形成垂直印章;

5、(3)在平面基底上制备半导体沟道层,并在半导体沟道层上沉积金属电极阵列,通过自组装分子对所述平面基底进行疏水化修饰,然后旋涂一层电子束胶作为粘附层;

6、(4)在粘附层的辅助下,拾取半导体沟道层和金属电极阵列,然后转移并释放到所述垂直凹槽的上方,此时半导体沟道层和金属电极阵列保持悬浮状态;

7、(5)通过所述垂直印章对悬浮的半导体沟道层和金属电极阵列进行垂直下压,半导体沟道层和金属电极阵列紧密贴合到所述垂直凹槽的侧壁上,即可获得垂直堆叠的晶体管。

8、进一步,在步骤(3)与步骤(4)之间增加对所述电子束胶的局部曝光处理,以释放步骤(5)中垂直印章下压过程产生的应力。

9、进一步,所述刚性基底为si、ge、gaas或sic,所述介电层为sio2、al2o3或hfo2。

10、进一步,所述掩模图案材料为cr/au、si3n4或光刻胶;所述刻蚀为碱溶液湿法刻蚀或等离子干法刻蚀;所述除去掩模为用铬蚀刻液和i2/ki溶液除cr/au,或hf除si3n4,或丙酮溶液除光刻胶。

11、进一步,所述橡胶为硅橡胶或热塑性聚氨酯橡胶。

12、进一步,所述半导体沟道层为过渡金属硫族化合物、氧化物半导体、钙钛矿等。

13、进一步,所述金属电极为au、ag或pt等。

14、进一步,所述自组装分子为六甲基二硅氮烷(hmds)、辛基三氯硅烷(ots)、或十八烷基三氯硅烷(odts)等。

15、进一步,所述电子束胶为pmma、zep520或re650等。

16、本发明的有益效果如下:

17、(1)本发明制备的垂直印章能与垂直凹槽完全嵌合,保证了晶体管与垂直衬底的保形接触。

18、(2)本发明所实施的垂直层压不涉及任何的溶液和机械应力,是一种全干法垂直集成,避免了界面的污染和器件结构的损伤。

19、(3)本发明不仅适用于二维半导体的垂直集成,在钙钛矿和有机/无机半导体器件等集成领域都具有广阔的应用前景。

20、(4)本发明通过垂直印章可以将平面晶体管成功转移到垂直侧壁上,克服了传统平面工艺与垂直结构的不兼容性,简化了多层晶体管垂直堆叠的工艺过程,为高密度集成电路的发展提供了一种可选择的方案。

技术特征:1.一种用于晶体管垂直堆叠的集成方法,其特征在于,包括以下步骤:

2.如权利要求1所述的一种用于晶体管垂直堆叠的集成方法,其特征在于,在步骤(3)与步骤(4)之间增加对所述电子束胶的局部曝光处理,以释放步骤(5)中垂直印章下压过程产生的应力。

3.如权利要求1-2所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述刚性基底为si、ge、gaas或sic,所述介电层为sio2、al2o3或hfo2。

4.如权利要求1-3所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述掩模图案材料为cr/au、si3n4或光刻胶;所述刻蚀为碱溶液湿法刻蚀或等离子干法刻蚀;所述除去掩模为用铬蚀刻液和i2/ki溶液除cr/au,或hf除si3n4,或丙酮溶液除光刻胶。

5.如权利要求1-4所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述橡胶为硅橡胶或热塑性聚氨酯橡胶。

6.如权利要求1-5所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述半导体沟道层为过渡金属硫族化合物、氧化物半导体或钙钛矿。

7.如权利要求1-6所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述金属电极为au、ag或pt。

8.如权利要求1-7所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述自组装分子为六甲基二硅氮烷、辛基三氯硅烷或十八烷基三氯硅烷。

9.如权利要求1-8所述的任一一种用于晶体管垂直堆叠的集成方法,其特征在于,所述电子束胶为pmma、zep520或re650。

技术总结本发明提供一种用于晶体管垂直堆叠的集成方法,首先制备垂直凹槽和垂直印章,然后转移半导体沟道层和金属电极阵列形成悬浮结构,最后通过垂直印章对悬浮的半导体沟道层和金属电极阵列进行垂直层压。本发明通过一次垂直层压即可同时获得垂直堆叠的多层晶体管,简化了晶体管垂直堆叠的工艺过程。其次,本发明中垂直印章与凹槽完全嵌合,而且层压过程中不涉及溶液和机械应力,避免了界面的污染和器件结构的损伤,实现了晶体管的保形接触和无损垂直集成。技术研发人员:刘渊,陶全洋受保护的技术使用者:湖南大学技术研发日:技术公布日:2024/9/26本文地址:https://www.jishuxx.com/zhuanli/20240929/309878.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表