分数除频电路的补偿电路的制作方法

- 国知局

- 2024-10-09 15:24:22

本发明涉及电气元件组件,具体为分数除频电路的补偿电路。

背景技术:

1、如今的集成电路(ic)上都有至少一锁相电路(phase-lock,loop,pll),以提供集成电路上所需的各种频率时钟。同时,现有集成电路随着半导体线程的精度演进,导致线程复杂度,集成电路的运作复杂度,且运作时的各种时脉可能不是整数倍的关系,例如,同一颗集成电路内可能需要用到66mhz,100mhz,133mhz的时脉。使用锁相电路来产生集成电路内所需的各种频率的时脉是最经济的方法,也就是说,锁相电路所输出的固定频率的脉波讯号经过除频处理,能够使锁相电路在固定频率输出脉波讯号,但为了得到不同频率的脉波讯号输出,则需要设置多个锁向电路,以提供多个频率之脉波讯号输出。从而导致电路的占用幅度面积过大,且功率消耗较高的问题,因而发展出单一锁相电路连结多个除频器,以提供不同频率之脉波讯号输出。

2、如图1所示,现有技术中,时脉产生电路10包括一时脉振温器12、一锁相电路14与复数个除频器26,时脉振温器12产生一基频脉波讯号fosc。该锁相电路14接收该基频脉波讯号fosc,以产生输入脉波讯号fin至除频器16,该除频器16各自输入对应的除频比例整数n1、n2、…、nk,以及除频比例小数al、αl、…、ak,使该除频器16分别依据对应的除频比例整数n1、n2、…、nk,以及除频比例小数αl、α2、……、ak,因而产生出对应的输出脉波讯号fout1、fout2、…、foutk。

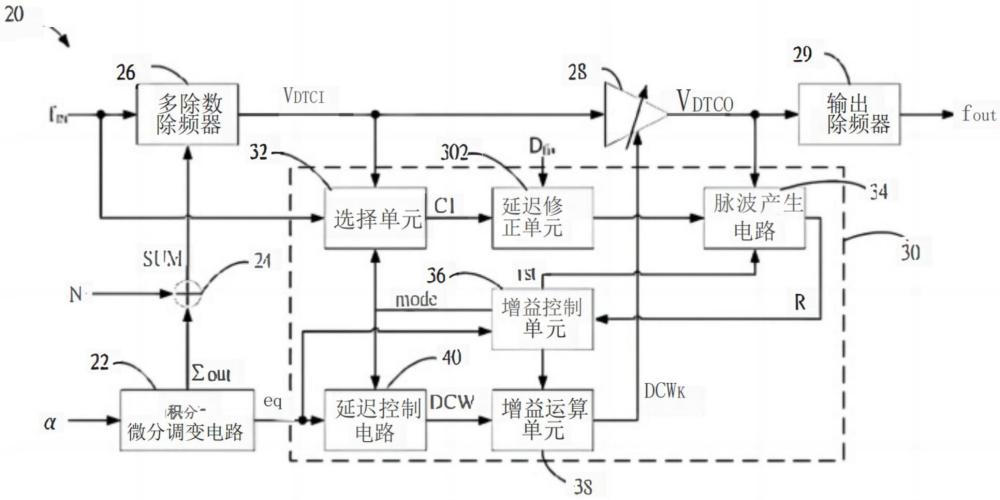

3、如图2所示,每个除频器16为一数位除频器,其设有一多除数除频器162、一数位时间转换器164、一加总单元166、一调变器167与一增益校准电路168。而该多除数除频器162为接收输入脉波讯号fin,以产生一除频讯号vdtc1至该数位时间转换器164,该加总单元166接收一除频比例整数n与该调变器167的一输出讯号∑out,以产生一加总结果sum至该多除数除频器162,供该多除数除频器162进一步依据该加总结果sum产生该除频讯号vdtc1,且该调变器167依据该除频比例小数α产生一误差讯号eq至该增益校准电路168并产生该输出讯号∑out至该加总单元166,该增益校准电路168依据该误差讯号eq产生一补偿讯号eqkg至该数位时间转换器164,以此让该数位时间转换器164将除频讯号vdtc1转换为数位时间输出讯号vdtco,以作为输出脉波讯号fout1,其中该补偿讯号eqkg为eq[k]×2^p×kdic。

4、然而,上述该增益校准电路168虽然能够改善除频器16的精确度,却因该增益校准电路168内设置了多个数位时间转换器,因而增加功率消耗。

5、基于上述问题,本发明提供一种分数除频电路的补偿电路,其减少数位时间转换器的设置,并以误差讯号结合初始讯号与第二讯号,以产生增益补偿讯号至一分数除频电路,以此让该分数除频电路藉此经补偿后产生对应之一输出脉波讯号,进而减少分数除频电路的功率消耗。

技术实现思路

1、本发明的目的在于提供分数除频电路的补偿电路,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:分数除频电路的补偿电路,包括一选择单元、一脉波产生电路、一增益控制单元与一增益运算单元,所述脉波产生电路的输入端耦接所述选择单元,所述脉波产生电路的输出端耦接所述增益控制单元,所述增益运算单元的输入端耦接一延迟控制电路与所述增益控制单元,所述增益运算单元的输出端耦接所述分数除频电路;所述选择单元接收所述输入脉波讯号与一除频讯号,所述选择单元依据所述输入脉波讯号与所述除频讯号产生一第一讯号,所述脉波产生电路依据所述第一讯号产生一第二讯号,当一数位时间输出讯号输入至所述脉波产生电路,则对应产生一初始讯号,所述增益控制单元依据所述第二讯号与所述初始讯号产生一增益控制讯号,一量化误差讯号输入至所述延迟控制电路,以对应产生一延迟控制讯号,所述增益运算单元接收所述增益控制讯号与所述延迟控制讯号,以对应产生一增益补偿讯号至所述分数除频电路而使所述分数除频电路依据所述输入脉波讯号产生一输出脉波讯号;综上,本发明的补偿电路因未使用数位时间转换器,且本发明的补偿电路所提供的增益补偿讯号相当于利用数位时间转换器所提供之增益补偿讯号,因此,本发明的补偿电路减少了电路的功率消耗。

3、作为本发明进一步的方案:所述分数除频电路包括一积分-微分调变电路、一加总单元、一多除数除频器、一数位时间转换电路和一输出除频器;一积分-微分调变电路用于接收一除频比例小数,以产生所述量化误差讯号与一调变讯号;一加总单元用于耦接所述积分-微分调变电路,以接收一除频比例整数与所述调变讯号,并产生一加总讯号;一多除数除频器用于耦接所述加总单元,以接收所述加总讯号与所述输入脉波讯号,并产生所述除频讯号;一数位时间转换电路耦接所述增益运算单元与所述多除数除频器,并接收所述除频讯号与所述增益补偿讯号,产生所述数位时间输出讯号;以及一输出除频器耦接所述数位时间转换电路,接收所述数位时间输出讯号与一除数,以产生所述输出脉波讯号。

4、作为本发明进一步的方案:所述选择单元包括一正反器和一选择元件,一正反器耦接所述分数除频电路并接收所述除频讯号,以将所述除频讯号储存为一储存除频讯号,且依据所述输入脉波讯号输出所述储存除频讯号;以及一选择元件依据一控制讯号选择所述除频讯号或所述储存除频讯号作为所述第一讯号并输出。

5、作为本发明进一步的方案:还包括一延迟修正单元,其耦接于该选择单元与该脉波産生电路之间,并依据一延迟修正讯号修正该除频讯号的一脉波宽度。

6、作为本发明进一步的方案:所述脉波产生电路包括一脉波产生器、一脉波电压转换单元和一比较器,其中,一脉波产生器接收所述第一讯号并对应产生一第二脉波讯号,且接收所述数位时间输出讯号并对应产生一初始脉波讯号;一脉波电压转换单元用于接收所述第二脉波讯号并转换为所述第二讯号,且接收所述初始脉波讯号并转换为所述初始讯号;一比较器用于接收所述初始讯号与所述第二讯号并产生一比较讯号至所述增益控制单元。

7、作为本发明进一步的方案:所述增益控制单元还产生一控制讯号至所述选择单元与所述延迟控制单元,以控制所述增益补偿讯号。

8、作为本发明进一步的方案:所述延迟控制电路包括一撷取单元,其撷取所述量化误差讯号并产生一撷取讯号;以及一延迟选择单元,其依据一控制讯号选择所述撷取讯号或一乘数因子作为所述延迟控制讯号并输出至所述增益运算单元。

9、作为本发明进一步的方案:所述第二讯号为所述初始讯号+(一乘数因子×所述增益控制讯号×一数位时间控制系数-一延迟输入讯号),当所述初始讯号与所述第二讯号相等时,所述延迟输入讯号为所述乘数因子×所述增益控制讯号×所述数位时间控制系数。

10、作为本发明进一步的方案:所述增益补偿讯号对应所述延迟控制讯号,所述延迟控制讯号为一乘数因子×所述增益控制讯号,所述增益控制讯号的一最大值为1。

11、作为本发明进一步的方案:所述第二讯号与所述初始讯号之差为一延迟输入讯号。

12、与现有技术相比,本发明的有益效果是:

13、1、本发明通过一增益控制单元依据一第二讯号与一初始讯号产生一增益控制讯号,并由一增益运算单元接收该增益控制讯号与一延迟控制讯号,以对应产生一增益补偿讯号至该分数除频电路,以使该分数除频电路依据该输入脉波讯号产生一输出脉波讯号,改善了该分数除频电路的功率消耗。

14、2、本发明通过减少数位时间转换器的设置,并根据除频讯号产生对应的初始讯号与第二讯号,进而依据该初始讯号与该第二讯号以及对应的误差讯号,以产生对应的增益补偿讯号至分数除频电路,作为补偿之用,同时能够产生一输出脉波讯号并减少功率消耗。

15、3、本发明通过避免使用多个数位时间转换器,而采用补偿电路提供的增益补偿讯号,相当于利用数位时间转换器提供的增益补偿讯号,因此本发明的补偿电路能够减少功率消耗。

本文地址:https://www.jishuxx.com/zhuanli/20241009/308628.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表