应用于DSP定点计算的指令扩展方法、系统、设备及介质与流程

- 国知局

- 2024-10-15 09:21:46

本技术涉及指令扩展,特别是涉及应用于dsp定点计算的指令扩展方法、系统、设备及介质。

背景技术:

1、指令集架构isa(instruction set architecture)是处理器的灵魂,由一组指令集合组成,对应着如加减乘除、数据读写等最小操作单元。risc-v是一个开源的精简指令集(reduced instruction set computer),秉承了简洁的设计哲学,指令设计简单,使得在芯片设计时,硬件实现开销较小,功耗和成本较低。

2、risc-v所对应的基础指令集rv32i仅有40多条,同时针对不同的应用场景,设计了模块化的指令集子集:rvm/a/f/d/c/v等,实现对原子操作、整数乘除法、单/双精度浮点、压缩指令、向量等扩展。用户可根据需求进行来决定采用或者不采用这些扩展,如在rv32i的基础上增加整数乘除法、原子操作、单精度浮点可以扩展为rv32imaf,从低功耗嵌入式扩展到高性能的浮点计算处理器。

3、risc-v标准指令集rv32g代表了rv32imafd,是一个完整功能的指令集,适用于大多数通用领域,同时risc-v还保留了用户自定义扩展指令集的可能性,可以针对特殊的领域进行指令的定制化扩展,极大的增强了risc-v的生命力,使得在细分领域能实现更优的表现。

4、在dsp领域的定点计算中,需要频繁地进行mac计算以及q31或者q15等格式的定点乘法计算。其中,risc-v原生定点计算指令中无mac功能,需要编译器根据计算功能分成多条指令组合完成,同时在面向q定点乘法运算时,计算完成乘法后需要根据q定点进行逻辑移位,分解到risc-v的基础指令,一次q计算操作也会分解为至少2条指令,中间需要对数据进行频繁的传递,影响计算效率,同时还面临着精度损失以及容易溢出的问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本技术的目的在于提供应用于dsp定点计算的指令扩展方法、系统、设备及介质,用于解决现有dsp定点计算中出现的精度损失及容易溢出的技术问题。

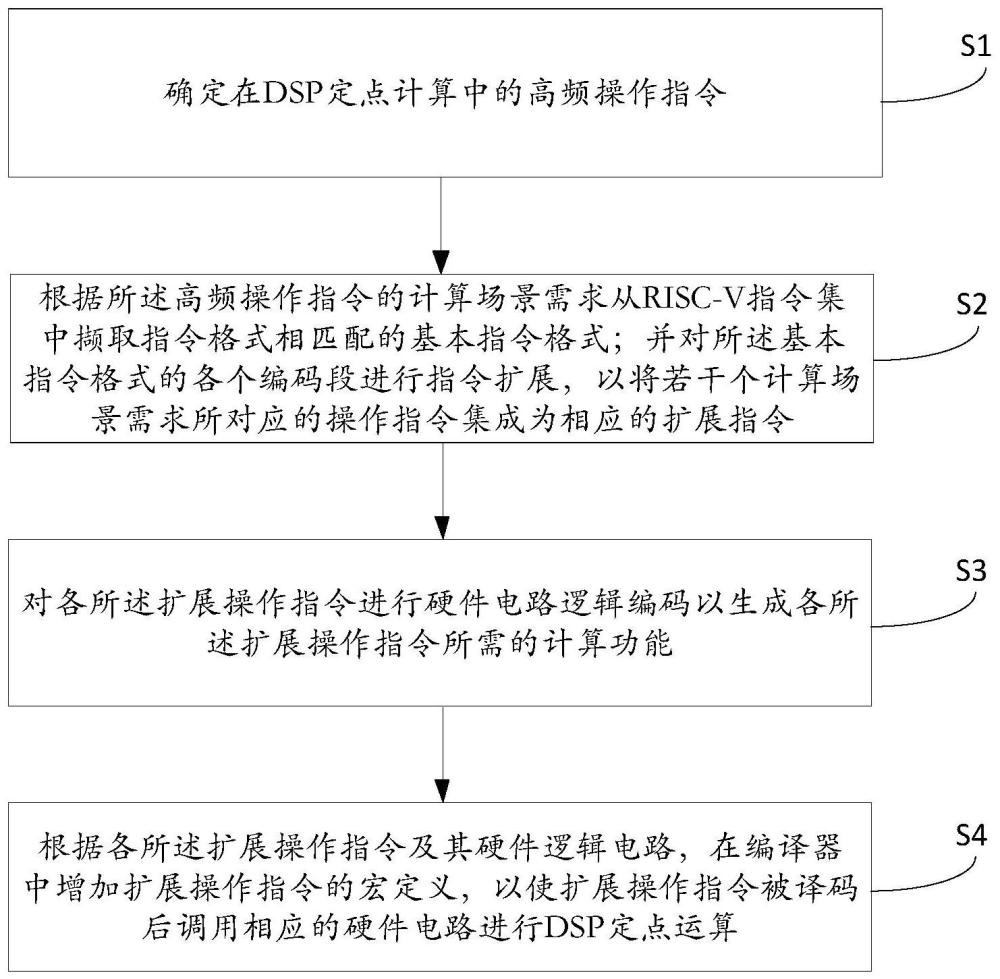

2、为实现上述目的及其他相关目的,本技术的第一方面提供一种应用于dsp定点计算的指令扩展方法,包括:确定在dsp定点计算中的高频操作指令;根据所述高频操作指令的计算场景需求从risc-v指令集中撷取指令格式相匹配的基本指令格式;并对所述基本指令格式的各个编码段进行指令扩展,以将若干个计算场景需求所对应的操作指令集成为相应的扩展指令;对各所述扩展指令进行硬件电路逻辑编码以生成各所述扩展指令所需的计算功能;根据各所述扩展指令及其硬件逻辑电路,在编译器中增加扩展指令的宏定义,以使扩展指令被译码后调用相应的硬件电路进行dsp定点运算。

3、于本技术的第一方面的一些实施例中,从risc-v指令集中撷取的基本指令格式包括r-type指令格式。

4、于本技术的第一方面的一些实施例中,对所述基本指令格式的各个编码段进行指令扩展包括:对r-type指令格式中的编码类型、寄存器编码段、操作类型编码段分别进行指令扩展。

5、于本技术的第一方面的一些实施例中,对r-type指令格式中的寄存器编码段进行指令扩展的方式包括:将r-type指令格式的编码段rs1的存储数设为指向第一输入寄存器的地址;将r-type指令格式的编码段rs2的存储数设为指向第二输入寄存器的地址;将r-type指令格式的编码段rd的存储数设为指向输出寄存器的地址;其中,所述第一输入寄存器和第二输入寄存器为q定点计算和mac计算的乘法输入寄存器;所述输出寄存器为存放q定点计算结果和mac计算结果的寄存器。

6、于本技术的第一方面的一些实施例中,对r-type指令格式中的操作类型编码段funct7进行指令扩展,指令扩展方式包括:在q定点计算中,将操作类型编码段funct7的7bit中的最高2bit设置为0x3以用于表示q定点计算程序,并将其余5bit设置为立即数;在mac计算中,将操作类型编码段funct7的7bit设置为0x20以用于表示mac计算程序。

7、于本技术的第一方面的一些实施例中,对r-type指令格式中的操作类型编码段funct3进行指令扩展,以通过对操作类型编码段funct3进行不同的编码定义来相应设定q定点计算的各类子功能。

8、于本技术的第一方面的一些实施例中,在q定点计算中:将操作类型编码段funct3的funct3[2:0]编码定义为0x0,以指向mulsri操作指令;所述mulsri操作指令用于指示相乘得到64bit结果后进行逻辑右移并保留低32bit的操作;将操作类型编码段funct3的funct3[2:0]编码定义为0x1,以指向srl64li操作指令;所述srl64li操作指令用于指示合并成64bit结果后进行逻辑右移并保留低32bit的操作。

9、于本技术的第一方面的一些实施例中,对r-type指令格式中的操作类型编码段funct3进行指令扩展,以通过对操作类型编码段funct3进行不同的编码定义来相应设定mac计算的各类子功能。

10、于本技术的第一方面的一些实施例中,在mac计算中:将操作类型编码段funct3的funct3[2:0]编码定义为0x0,以指向dmac操作指令;所述dmac操作指令用于指示相乘后进行相加并保存64bit的操作;将操作类型编码段funct3的funct3[2:0]编码定义为0x1,以指向mah操作指令;所述mah操作指令用于指示相乘后进行相加并保存高32bit的操作;将操作类型编码段funct3的funct3[2:0]编码定义为0x2,以指向mal操作指令;所述mal操作指令用于指示相乘后进行相加并保存低32bit的操作。

11、于本技术的第一方面的一些实施例中,所述高频操作指令包括q定点计算操作指令和mac计算操作指令。

12、于本技术的第一方面的一些实施例中,基于verilog硬件编程语言对所述扩展指令进行硬件电路逻辑编码。

13、为实现上述目的及其他相关目的,本技术的第二方面提供一种应用于dsp定点计算的指令扩展系统,包括:扩展指令生成模块,用于确定在dsp定点计算中的高频操作指令,并根据所述高频操作指令的计算场景需求,对risc-v指令集中r-type指令格式的各编码段进行指令扩展,以将若干个计算场景需求所对应的操作指令集成为相应的扩展指令;硬件电路逻辑编码模块,用于对各所述扩展指令进行硬件电路逻辑编码以生成各所述扩展指令所需的计算功能;宏定义模块,用于根据各所述扩展指令及其硬件逻辑电路,在编译器中增加扩展指令的宏定义,以使扩展指令被译码后调用相应的硬件电路进行dsp定点运算。

14、为实现上述目的及其他相关目的,本技术的第三方面提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现所述应用于dsp定点计算的指令扩展方法。

15、为实现上述目的及其他相关目的,本技术的第四方面提供一种计算机设备,包括:处理器及存储器;所述存储器用于存储计算机程序,所述处理器用于执行所述存储器存储的计算机程序,以使所述终端执行所述应用于dsp定点计算的指令扩展方法。

16、如上所述,本技术的应用于dsp定点计算的指令扩展方法、系统、设备及介质,具有以下有益效果:

17、(1)利用risc-v的可扩展性,基于其r-type指令格式将dsp场景中频繁使用的q定点乘法和mac计算扩展为固化的硬件电路,以将多条基本指令集成为一条指令,降低了流水线的压力和指令执行的延迟等,提升程序运行效率,集成指令相对于原指令组合获得至少一倍以上的性能提升。

18、(2)通过扩展指令集,使得32bit数相乘后可以直接保存64bit中间结果,并按q定点格式进行逻辑右移操作,保留了更多的低bit数据,提升了计算精度。

19、(3)由于同样的两个32bit数相乘最高不会超过64bit,而本发明中的扩展指令集将中间结果寄存器扩展到64bit,可以防止相乘时的溢出问题,提升了应用计算时的适配范围,防止溢出问题发生。

本文地址:https://www.jishuxx.com/zhuanli/20241015/313900.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。