半导体结构的形成方法与流程

- 国知局

- 2024-10-21 14:24:06

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构的形成方法。

背景技术:

1、在半导体制造中,随着超大规模集成电路的发展趋势,集成电路特征尺寸持续减小,为了适应更小的特征尺寸,金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)的沟道长度也相应不断缩短。然而,随着器件沟道长度的缩短,器件源极与漏极间的距离也随之缩短,因此栅极结构对沟道的控制能力随之变差,栅极电压夹断(pinch off)沟道的难度也越来越大,使得亚阈值漏电(subthreshold leakage)现象,即所谓的短沟道效应(sce:short-channel effects)更容易发生。

2、因此,为了更好的适应特征尺寸的减小,半导体工艺逐渐开始从平面mosfet向具有更高功效的三维立体式的晶体管过渡,如鳍式场效应晶体管(finfet)。finfet中,栅极结构至少可以从两侧对超薄体(鳍部)进行控制,与平面mosfet相比,栅极结构对沟道的控制能力更强,能够很好的抑制短沟道效应,且finfet相对于其他器件,与现有集成电路制造具有更好的兼容性。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构的形成方法,提高半导体结构的工作性能。

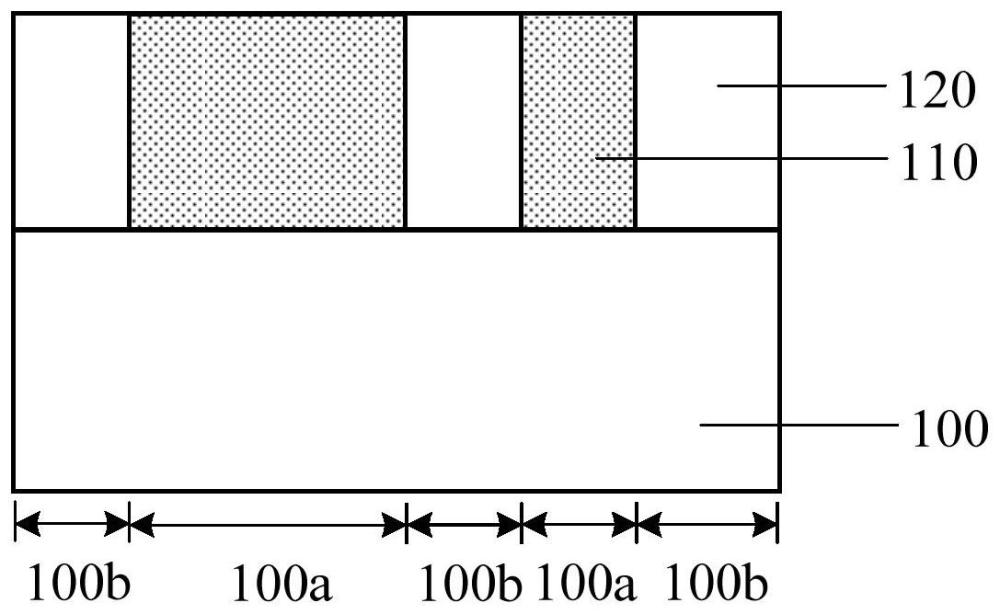

2、为解决上述问题,本发明实施例还提供了一种半导体结构的形成方法,包括:提供衬底,包括相邻的第一器件区和第二器件区,第一器件区用于形成第一器件,第二器件区用于形成第二器件;形成覆盖衬底的第一沟道材料层,第一沟道材料层的材料与衬底的材料不相同;图形化第一沟道材料层,去除位于第二器件区的第一沟道材料层,保留位于第一器件区的第一沟道材料层;在第二器件区形成第二沟道材料层;图形化第一沟道材料层和第二沟道材料层,形成位于第一器件区的第一沟道结构和位于第二器件区的第二沟道结构。

3、可选的,图形化所述第一沟道材料层的步骤包括:形成覆盖所述第一沟道材料层的掩膜材料层;图形化所述掩膜材料层,形成位于所述第一器件区的掩膜层;以所述掩膜层为掩膜图形化所述第一沟道材料层。

4、可选的,在所述第二器件区形成第二沟道材料层之后,去除所述掩膜层。

5、可选的,在所述第二器件区形成第二沟道材料层的步骤中,所述第二沟道材料层的顶面高于所述第一沟道材料层的顶面,或者,所述第二沟道材料层的顶面低于所述第一沟道材料层的顶面。

6、可选的,在所述第二器件区形成第二沟道材料层之后,图形化所述第一沟道材料层和第二沟道材料层之前,所述形成方法还包括:对所述第一沟道材料层和第二沟道材料层进行平坦化处理。

7、可选的,采用化学机械研磨工艺对所述第一沟道材料层和第二沟道材料层进行平坦化处理。

8、可选的,采用化学机械研磨工艺对所述第一沟道材料层和第二沟道材料层进行平坦化处理的步骤包括:对所述第一沟道材料层和第二沟道材料层同时进行研磨,直至目标高度;或者,以所述第一沟道材料层和第二沟道材料层中顶面较低的作为研磨停止层进行研磨,直至所述第一沟道材料层和第二沟道材料层顶面齐平;所述第一沟道材料层和第二沟道材料层顶面齐平后,对所述第一沟道材料层和第二沟道材料层同时进行研磨,直至目标高度。

9、可选的,在所述第二器件区形成第二沟道材料层的步骤中,所述第二沟道材料层与第一沟道材料层的材料不同。

10、可选的,在所述第二器件区形成第二沟道材料层的步骤中,所述第二沟道材料层与所述衬底的材料相同。

11、可选的,提供所述衬底的步骤中,所述衬底的材料为硅。

12、可选的,形成覆盖所述衬底的第一沟道材料层的步骤中,所述第一沟道材料层的材料为锗化硅。

13、可选的,形成所述第二沟道材料层的步骤中,所述第二沟道材料层的材料为硅。

14、可选的,采用外延生长工艺形成覆盖所述衬底的第一沟道材料层。

15、可选的,采用外延生长工艺形成所述第二沟道材料层。

16、可选的,图形化所述第一沟道材料层的步骤中,相邻剩余第一沟道材料层之间的间距为50nm至300nm。

17、与现有技术相比,本发明实施例的技术方案具有以下优点:

18、本发明实施例提供的形成方法中,形成覆盖衬底的第一沟道材料层,第一沟道材料层的材料与衬底的材料不相同,图形化第一沟道材料层,去除位于第二器件区的第一沟道材料层,保留位于第一器件区的第一沟道材料层,在第二器件区形成第二沟道材料层,图形化第一沟道材料层和第二沟道材料层,形成位于第一器件区的第一沟道结构和位于第二器件区的第二沟道结构;本发明实施例中,第一沟道材料层的材料与衬底的材料不同,则在图形化第一沟道材料层时,能够以衬底作为刻蚀停止位置进行图形化,有利于使得图形化后剩余的第一沟道材料层的侧壁垂直度较好,且高度一致性较好,同时,有利于减小剩余第一沟道材料层侧壁与衬底接触位置产生圆角(corner)的概率,则形成第二沟道材料层时,有利于使得第二沟道材料层的侧壁垂直度较好,且高度一致性较好,从而图形化第一沟道材料层和第二沟道材料层形成第一沟道结构和第二沟道结构时,有利于提高第一沟道结构的高度一致性、以及第二沟道结构的高度一致性,提高半导体结构的工作性能。

技术特征:1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,图形化所述第一沟道材料层的步骤包括:形成覆盖所述第一沟道材料层的掩膜材料层;

3.如权利要求2所述的半导体结构的形成方法,其特征在于,在所述第二器件区形成第二沟道材料层之后,去除所述掩膜层。

4.如权利要求1所述的半导体结构的形成方法,其特征在于,在所述第二器件区形成第二沟道材料层的步骤中,所述第二沟道材料层的顶面高于所述第一沟道材料层的顶面,或者,所述第二沟道材料层的顶面低于所述第一沟道材料层的顶面。

5.如权利要求1或4所述的半导体结构的形成方法,其特征在于,在所述第二器件区形成第二沟道材料层之后,图形化所述第一沟道材料层和第二沟道材料层之前,所述形成方法还包括:对所述第一沟道材料层和第二沟道材料层进行平坦化处理。

6.如权利要求5所述的半导体结构的形成方法,其特征在于,采用化学机械研磨工艺对所述第一沟道材料层和第二沟道材料层进行平坦化处理。

7.如权利要求6所述的半导体结构的形成方法,其特征在于,采用化学机械研磨工艺对所述第一沟道材料层和第二沟道材料层进行平坦化处理的步骤包括:对所述第一沟道材料层和第二沟道材料层同时进行研磨,直至目标高度;或者,

8.如权利要求1所述的半导体结构的形成方法,其特征在于,在所述第二器件区形成第二沟道材料层的步骤中,所述第二沟道材料层与第一沟道材料层的材料不同。

9.如权利要求1所述的半导体结构的形成方法,其特征在于,在所述第二器件区形成第二沟道材料层的步骤中,所述第二沟道材料层与所述衬底的材料相同。

10.如权利要求1所述的半导体结构的形成方法,其特征在于,提供所述衬底的步骤中,所述衬底的材料为硅。

11.如权利要求1所述的半导体结构的形成方法,其特征在于,形成覆盖所述衬底的第一沟道材料层的步骤中,所述第一沟道材料层的材料为锗化硅。

12.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述第二沟道材料层的步骤中,所述第二沟道材料层的材料为硅。

13.如权利要求1所述的半导体结构的形成方法,其特征在于,采用外延生长工艺形成覆盖所述衬底的第一沟道材料层。

14.如权利要求1所述的半导体结构的形成方法,其特征在于,采用外延生长工艺形成所述第二沟道材料层。

15.如权利要求1所述的半导体结构的形成方法,其特征在于,图形化所述第一沟道材料层的步骤中,相邻剩余第一沟道材料层之间的间距为50nm至300nm。

技术总结一种半导体结构的形成方法,包括:提供衬底,包括相邻的第一器件区和第二器件区,第一器件区用于形成第一器件,第二器件区用于形成第二器件;形成覆盖衬底的第一沟道材料层,第一沟道材料层的材料与衬底的材料不相同;图形化第一沟道材料层,去除位于第二器件区的第一沟道材料层,保留位于第一器件区的第一沟道材料层;在第二器件区形成第二沟道材料层;图形化第一沟道材料层和第二沟道材料层,形成位于第一器件区的第一沟道结构和位于第二器件区的第二沟道结构。本发明有利于提高半导体结构的工作性能。技术研发人员:司进,殷立强,李昱辰,崇二敏,张海洋受保护的技术使用者:中芯国际集成电路制造(上海)有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/317994.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。