一种铁电晶体管及其制造方法

- 国知局

- 2024-10-21 14:21:27

本发明涉及半导体领域,特别涉及一种铁电晶体管及其制造方法。

背景技术:

1、随着半导体技术的发展,集成电路的特征尺寸持续微缩,集成密度不断增加,即晶体管尺寸不断缩小以提高集成密度。但是集成电路在实现高计算性能的同时,也承担巨大功耗损失。

2、集成电路中包括铁电晶体管,当前铁电晶体管主要利用硅材料作为沟道材料,但是硅材料作为沟道材料时,具有较强的电子-声子散射,并且存在焦耳热耗散,这些都增加晶体管的功耗,影响晶体管的可靠性。

3、因此现在亟需一种低功耗的铁电晶体管。

技术实现思路

1、有鉴于此,本申请的目的在于提供一种铁电晶体管及其制造方法,能够实现铁电晶体管的高载流子迁移率以及低功耗,提高铁电晶体管的性能。

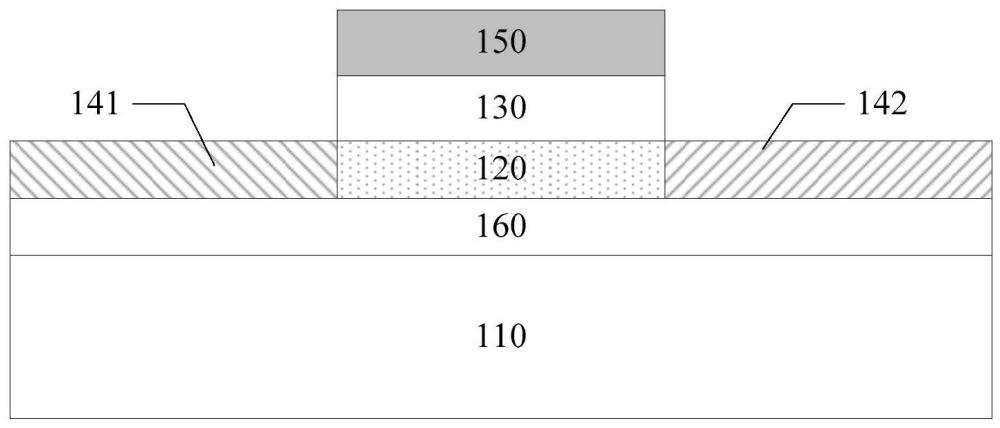

2、本申请实施例提供了一种铁电晶体管,所述铁电晶体管包括:

3、衬底;

4、沟道层,所述沟道层设置于所述衬底的一侧,所述沟道层的材料至少包括拓扑绝缘体氧化铪;

5、铁电层,所述铁电层设置于所述沟道层远离所述衬底的一侧,所述铁电层的材料至少包括掺杂氧化铪。

6、可选地,所述拓扑绝缘体氧化铪是利用电场诱导氧化铪的拓扑相变形成。

7、可选地,所述铁电层的材料可以为掺锆氧化铪、掺铝氧化铪、掺硅氧化铪、掺钆氧化铪、掺锶氧化铪和掺钪氧化铪中的一种或多种。

8、可选地,通过切换所述铁电层的极化状态,以调控所述沟道层拓扑表面态的载流子浓度。

9、可选地,所述沟道层的制造工艺为机械剥离工艺、化学剥离工艺、分子束外延生长工艺、化学气相沉积工艺或物理气相沉积工艺。

10、可选地,在平行于所述衬底所在平面的方向上,所述沟道层两侧设置有源极和漏极,所述源极和漏极的材料至少包括氧化铪。

11、可选地,还包括:栅电极;

12、所述栅电极设置于所述铁电层远离所述衬底的一侧。

13、可选地,还包括:绝缘层;

14、所述绝缘层设置于所述衬底和所述沟道层之间。

15、可选地,还包括:覆盖层和多个接触;

16、所述覆盖层设置于所述栅电极远离所述衬底的一侧,所述覆盖层覆盖所述栅电极、所述源极和所述漏极,所述多个接触贯穿所述覆盖层分别至所述栅电极、所述源极和所述漏极。

17、本申请实施例提供一种铁电晶体管的制造方法,所述方法包括:

18、在所述衬底的一侧形成沟道层,所述沟道层的材料至少包括拓扑绝缘体氧化铪;

19、在所述沟道层远离所述衬底的一侧形成铁电层,所述铁电层的材料至少包括掺杂氧化铪。

20、本申请实施例提供了一种铁电晶体管,铁电晶体管包括:衬底、沟道层和铁电层,沟道层设置于衬底的一侧,铁电层设置于沟道层远离衬底的一侧,即衬底、沟道层和铁电层层叠设置。沟道层的材料至少包括拓扑绝缘体氧化铪,也就是说,本申请实施例提供的铁电晶体管的沟道材料为拓扑绝缘体氧化铪,能够具有较高的载流子迁移率,并且不受声子散射的干扰,对杂质、温度和压强等材料参数不敏感,功耗较低。铁电层的材料至少包括掺杂氧化铪,即利用具有铁电极化性质的材料作为铁电晶体管的栅介质,可以实现对于铁电晶体管的开态或关态的控制。此外,沟道层和铁电层都包括氧化铪,两个膜层之间接触较好,沟道层和铁电层的界面质量较高,能够降低载流子的损失,降低功耗,提高铁电晶体管的性能。

技术特征:1.一种铁电晶体管,其特征在于,所述铁电晶体管包括:

2.根据权利要求1所述的铁电晶体管,其特征在于,所述拓扑绝缘体氧化铪是利用电场诱导氧化铪的拓扑相变形成。

3.根据权利要求1所述的铁电晶体管,其特征在于,所述铁电层的材料可以为掺锆氧化铪、掺铝氧化铪、掺硅氧化铪、掺钆氧化铪、掺锶氧化铪和掺钪氧化铪中的一种或多种。

4.根据权利要求1所述的铁电晶体管,其特征在于,通过切换所述铁电层的极化状态,以调控所述沟道层拓扑表面态的载流子浓度。

5.根据权利要求1所述的铁电晶体管,其特征在于,所述沟道层的制造工艺为机械剥离工艺、化学剥离工艺、分子束外延生长工艺、化学气相沉积工艺或物理气相沉积工艺。

6.根据权利要求1-5任意一项所述的铁电晶体管,其特征在于,在平行于所述衬底所在平面的方向上,所述沟道层两侧设置有源极和漏极,所述源极和漏极的材料至少包括氧化铪。

7.根据权利要求1-5任意一项所述的铁电晶体管,其特征在于,还包括:栅电极;

8.根据权利要求1-5任意一项所述的铁电晶体管,其特征在于,还包括:绝缘层;

9.根据权利要求7所述的铁电晶体管,其特征在于,还包括:覆盖层和多个接触;

10.一种铁电晶体管的制造方法,其特征在于,所述方法包括:

技术总结本申请提供一种铁电晶体管及其制造方法,包括:衬底、沟道层和铁电层,衬底、沟道层和铁电层层叠设置。沟道层的材料至少包括拓扑绝缘体氧化铪,也就是说,本申请实施例提供的铁电晶体管的沟道材料为拓扑绝缘体氧化铪,能够具有较高的载流子迁移率,并且不受声子散射的干扰,对杂质、温度和压强等材料参数不敏感,功耗较低。铁电层的材料至少包括掺杂氧化铪,即利用具有铁电极化性质的材料作为铁电晶体管的栅介质,可以实现对于铁电晶体管的开态或关态的控制。此外,沟道层和铁电层都包括氧化铪,两个膜层之间接触较好,沟道层和铁电层的界面质量较高,能够降低载流子的损失,降低功耗,提高铁电晶体管的性能。技术研发人员:王晓磊,凡洪洋,赵园园,柴俊帅,徐昊,王文武受保护的技术使用者:中国科学院微电子研究所技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/317845.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

逆变器组装结构的制作方法

下一篇

返回列表