半导体结构及其形成方法与流程

- 国知局

- 2024-10-21 14:24:59

本发明实施例是关于半导体工艺技术,特别是关于一种阻挡结构的形成方法。

背景技术:

1、随着科技的进步,存储器器件的关键尺寸也逐渐缩小,进而使得光刻工艺变得越来越困难。在常规的光刻工艺中,缩减关键尺寸的方法包含使用较大数值孔径的光学器件、较短的曝光波长、或是使用除了空气以外的界面介质(例如,水浸入)。随着常规的光刻工艺的解析度逐渐接近理论极限,制造商已开始转向诸如双重图案化(double-patterning;dp)的方法来克服光学极限,进而提升存储器器件的积集度。

2、然而,在存储器装置的形成工艺中,可能会在阵列区与周边区之间的过渡区形成掺质的移动路径,进而产生漏电流。因此,为了追求更低的成本并维持产品的性能,业界仍需要改善半导体结构的形成方法,来达到维持存储器装置的成品率的目标。

技术实现思路

1、本发明实施例提供了一种半导体结构的形成方法,包含提供衬底,衬底具有阵列区、周边区及位于阵列区与周边区之间的过渡区;形成图案化浮栅极层于衬底的阵列区及周边区上;顺应地形成堆叠层于衬底上,从而形成凹槽于过渡区上方;形成光刻胶于衬底上且填入凹槽之中;图案化光刻胶以形成阵列区图案于阵列区的堆叠层上,其中光刻胶的一部分残留于凹槽的底部,从而形成凹槽图案;以及将阵列区图案及凹槽图案依序转移至堆叠层、图案化浮栅极层及衬底,以形成多个阵列于阵列区中,且形成一对阻挡结构于过渡区中。

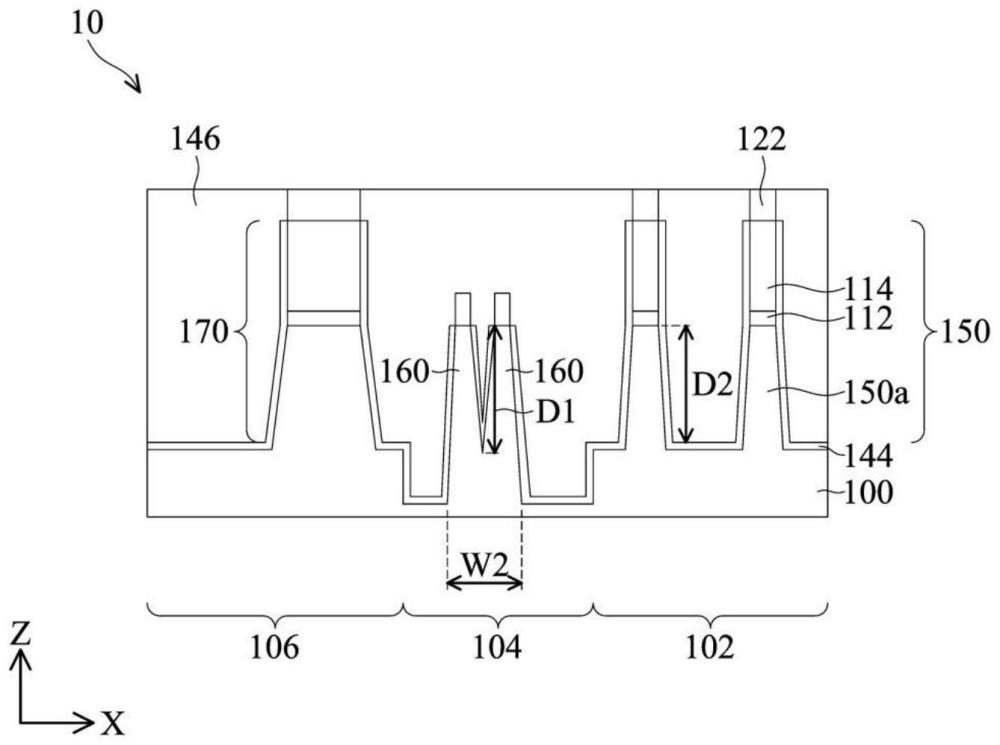

2、本发明实施例提供了一种半导体结构,包含多个阵列,设置于衬底的阵列区中;周边结构,设置于衬底的周边区中;以及一对阻挡结构,设置于衬底的过渡区中且由衬底的一部分所构成,其中过渡区位于阵列区与周边区之间。

3、本发明实施例借由使光刻胶因图案化浮栅极层的开口深宽比的改变而残留于堆叠层所形成的凹槽内,进而在后续的工艺中形成额外的侧壁间隔物于过渡区上,以及对应形成阻挡结构于过渡区中,从而避免阵列中的掺质在后续的退火工艺期间沿着介电层与衬底之间的界面扩散至周边区并造成短路,以及维持存储器装置的成品率。

技术特征:1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,将该阵列区图案及该凹槽图案依序转移至该堆叠层、该图案化浮栅极层及该衬底的步骤更包括:

3.如权利要求2所述的半导体结构的形成方法,其特征在于,在移除该图案化芯轴层的步骤之后,更包括:

4.如权利要求1所述的半导体结构的形成方法,其特征在于,在形成所述多个阵列及该对阻挡结构之后,更包括:

5.如权利要求1所述的半导体结构的形成方法,其特征在于,顺应地形成该堆叠层的步骤包括:

6.如权利要求1所述的半导体结构的形成方法,其特征在于,该图案化浮栅极层在该衬底的该阵列区与该周边区之间具有一开口,该开口的深宽比大于0.13。

7.如权利要求1所述的半导体结构的形成方法,其特征在于,形成该图案化浮栅极层的步骤更包括:

8.一种半导体结构,其特征在于,包括:

9.如权利要求8所述的半导体结构,其特征在于,该对阻挡结构之间的沟槽深度大于所述多个阵列之间的沟槽深度。

10.如权利要求8所述的半导体结构,其特征在于,更包括:

11.如权利要求8所述的半导体结构,其特征在于,该对阻挡结构的顶表面低于所述多个阵列的顶表面。

12.如权利要求8所述的半导体结构,其特征在于,所述多个阵列包括:

13.如权利要求8所述的半导体结构,其特征在于,更包括:

14.如权利要求8所述的半导体结构,其特征在于,该周边区围绕该阵列区,且该阵列区与该周边区之间的间距为定值。

技术总结本发明提供了一种半导体结构及其形成方法,包含提供衬底,衬底具有阵列区、周边区及位于阵列区与周边区之间的过渡区。方法包含形成图案化浮栅极层于阵列区及周边区上,以及顺应地形成堆叠层于衬底上,其中凹槽形成于过渡区上方。方法包含形成光刻胶于衬底上,以及图案化光刻胶以形成阵列区图案于阵列区的堆叠层上,其中光刻胶的一部分残留于凹槽的底部,且形成凹槽图案。方法更包含将阵列区图案及凹槽图案依序转移至堆叠层、图案化浮栅极层及衬底,以形成多个阵列以及一对阻挡结构。技术研发人员:蓝顺醴受保护的技术使用者:华邦电子股份有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/318063.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。