一种光子集成芯片结构及其制作方法与流程

- 国知局

- 2024-10-21 14:51:27

本发明涉及一种光子集成芯片结构及其制作方法,属于半导体激光器。

背景技术:

1、光子集成芯片是由多个独立的光子器件集成在同一衬底上形成的器件结构,常见的是将激光器、调制器、光放大器和探测器等其中的一种或几种集成在半导体ⅲ-v材料或者si衬底上。传统的光子集成芯片大部分是基于n型衬底材料,所有器件共用一种n极。这类光子集成芯片只能对分立的光子器件进行p隔离,无法实现n隔离,因此只能对每个器件分别进行单端射频驱动。如果可以对光子集成芯片中每个器件的p、n电极同时进行电隔离,能够显著减小器件之间的串扰,从而实现光子芯片p\n双侧射频驱动。

2、光子集成芯片中常见的电隔离方式是深刻蚀结构,将两个器件之间的p型材料完全或部分刻蚀,大幅提高器件之间的p隔离电阻,从而阻断器件p电极之间的串扰。虽然我们也可以对衬底一侧的n型材料进行刻蚀实现n隔离,但是集成芯片上的各个光器件一般需要通过衬底进行散热,刻蚀衬底一侧的n型材料会大幅增加热阻,使得光器件结温大幅升高,不仅限制了光器件的工作电流,还使得器件的可靠性风险大幅增加。

3、通过离子注入和扩散也可以实现芯片间的电隔离。为了避免注入粒子或者扩散元素对外延生长的影响,注入和扩散都需要在完成外延后进行。这种情况下,由于注入深度很深,需要很高的粒子注入能量,不仅设备价格昂贵,而且高能粒子会对外延材料的光学性能产生不可控的影响。对于扩散方案,尤其是需要将材料类型反型的扩散方案,为了实现电隔离,需要比较深的扩散深度和更大的扩散浓度,这会导致扩散时间增加,而且大量扩散元素会增加光波导的损耗,在后续工艺中这些扩散元素不稳定,还会影响器件的可靠性。

技术实现思路

1、本发明提供了一种光子集成芯片结构及其制作方法,能够有效实现集成芯片中各分立器件之间的p\n电隔离,从而对器件进行p\n双侧射频驱动。

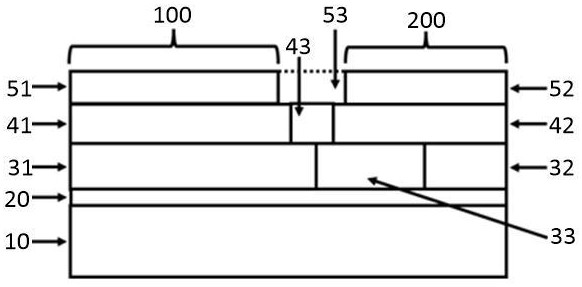

2、一方面,本发明提供了一种光子集成芯片结构,包括:

3、衬底;

4、缓冲层,形成在所述衬底上;

5、底部导电层,形成在所述缓冲层上,其包括多个底部导电区,相邻两个底部导电区之间设置有底部隔离区,底部隔离区用于将相邻两个底部导电区隔离;底部隔离区与相邻的底部导电区中掺杂杂质的类型相反;

6、核心层,形成在所述底部导电层上,其包括多个核心区,所述核心区与所述底部导电区一一对应;

7、顶部导电层,形成在所述核心层上,其包括多个顶部导电区,顶部导电区与核心区一一对应,相邻两个顶部导电区之间具有顶部隔离区。

8、可选的,相邻两个核心区之间设置有光传输区。

9、可选的,所述底部导电区与所述缓冲层中掺杂杂质的类型相反;所述衬底的类型为p型、n型或者半绝缘型。

10、可选的,所述顶部隔离区通过刻蚀工艺或掺杂工艺形成;所述顶部隔离区的宽度大于所述光传输区的宽度;所述顶部隔离区的左边缘距离所述光传输区的左边缘的距离、以及所述顶部隔离区的右边缘距离所述光传输区的右边缘的距离均大于或等于1um。

11、可选的,所述底部隔离区为p型掺杂或者n型掺杂的半导体层。

12、可选的,所述底部导电区的厚度大于或等于500nm;所述底部隔离区和所述底部导电区的厚度差不超过300nm;所述底部隔离区的左边缘距离所述光传输区的左边缘的距离、以及所述底部隔离区的右边缘距离所述光传输区的右边缘的距离均小于或等于10um。

13、可选的,所述光传输区的材料为多元半导体化合物。

14、另一方面,本发明提供了一种基于上述任一种所述的光子集成芯片结构的制作方法,所述方法包括:

15、在衬底上形成缓冲层;

16、在所述缓冲层上形成底部隔离区,并在所述底部隔离区的两侧形成底部导电区;

17、在所述底部导电区上形成对应的核心区;

18、在所述核心区上形成对应的顶部导电区,并在相邻两个顶部导电区之间形成顶部隔离区。

19、可选的,在所述底部导电区上形成对应的核心区之后,所述方法还包括:

20、在相邻两个核心区之间形成光传输区。

21、可选的,在所述缓冲层上形成底部隔离区,并在所述底部隔离区的两侧形成底部导电区,具体包括:

22、在所述缓冲层上形成底部隔离层,并对所述底部隔离层进行刻蚀工艺,得到底部隔离区;

23、在所述缓冲层上位于所述底部隔离区两侧的区域外延生长底部导电区。

24、本发明能产生的有益效果包括:

25、本发明提供的光子集成芯片结构,通过在相邻两个底部导电区之间设置底部隔离区,底部隔离区与相邻的底部导电区中掺杂杂质的类型相反,从而可以形成反型阻挡结,以此实现底部电隔离;相邻两个顶部导电区之间通过顶部隔离区实现电隔离,这样实现了集成芯片中各分立器件之间的p\n电隔离,从而可以对器件进行p\n双侧射频驱动,同时对其它器件无串扰。

技术特征:1.一种光子集成芯片结构,其特征在于,包括:

2.根据权利要求1所述的光子集成芯片结构,其特征在于,相邻两个核心区之间设置有光传输区。

3.根据权利要求1所述的光子集成芯片结构,其特征在于,所述底部导电区与所述缓冲层中掺杂杂质的类型相反;

4.根据权利要求2所述的光子集成芯片结构,其特征在于,所述顶部隔离区通过刻蚀工艺或掺杂工艺形成;

5.根据权利要求1所述的光子集成芯片结构,其特征在于,所述底部隔离区为p型掺杂或者n型掺杂的半导体层。

6.根据权利要求2所述的光子集成芯片结构,其特征在于,所述底部导电区的厚度大于或等于500nm;

7.根据权利要求2所述的光子集成芯片结构,其特征在于,所述光传输区的材料为多元半导体化合物。

8.一种基于权利要求1至7中任一项所述的光子集成芯片结构的制作方法,其特征在于,所述方法包括:

9.根据权利要求8所述的方法,其特征在于,在所述底部导电区上形成对应的核心区之后,所述方法还包括:

10.根据权利要求8所述的方法,其特征在于,在所述缓冲层上形成底部隔离区,并在所述底部隔离区的两侧形成底部导电区,具体包括:

技术总结本发明公开了一种光子集成芯片结构及其制作方法,属于半导体激光器技术领域,能够有效实现集成芯片中各分立器件之间的P\N电隔离,从而对器件进行P\N双侧射频驱动。所述光子集成芯片结构包括:衬底;缓冲层,形成在衬底上;底部导电层,形成在缓冲层上,其包括多个底部导电区,相邻两个底部导电区之间设置有底部隔离区,底部隔离区用于将相邻两个底部导电区隔离;底部隔离区与相邻的底部导电区中掺杂杂质的类型相反;核心层,其包括多个核心区,核心区与底部导电区一一对应;顶部导电层,其包括多个顶部导电区,顶部导电区与核心区一一对应,相邻两个顶部导电区之间具有顶部隔离区。本发明用于光子集成芯片中各分立器件之间的P\N电隔离。技术研发人员:张振宁,杨舒涵,李马惠,穆瑶,魏来严受保护的技术使用者:陕西源杰半导体科技股份有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/319558.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表