一种肖特基势垒二极管及其制作方法与流程

- 国知局

- 2024-10-21 14:54:42

本发明涉及半导体,尤其涉及一种肖特基势垒二极管及其制作方法。

背景技术:

1、肖特基势垒二极管(schottky barrier diode,简称sbd)是利用金属与半导体接触形成的金属-半导体结原理进行制作的一种二极管,目前通常采用高功函金属如金(au)、铂(pt)等材料作为sbd的阳极,采用n型半导体材料或低功函金属作为sbd的阴极,高功函金属与半导体之间的接触面上可以形成肖特基势垒。sbd具有开关频率高和正向压降低等优点,可以应用于整流电路、保护电路、开关电路等场景中。

2、肖特基势垒二极管器件中,形成肖特基接触的材料和肖特基接触的接触质量直接影响了其性能,为了进一步提高肖特基势垒二极管的性能,还需要探索新的材料和合适的器件结构。

技术实现思路

1、本发明提供了一种肖特基势垒二极管及其制作方法,可以提高肖特基势垒二极管的器件性能,降低器件的串联电阻。

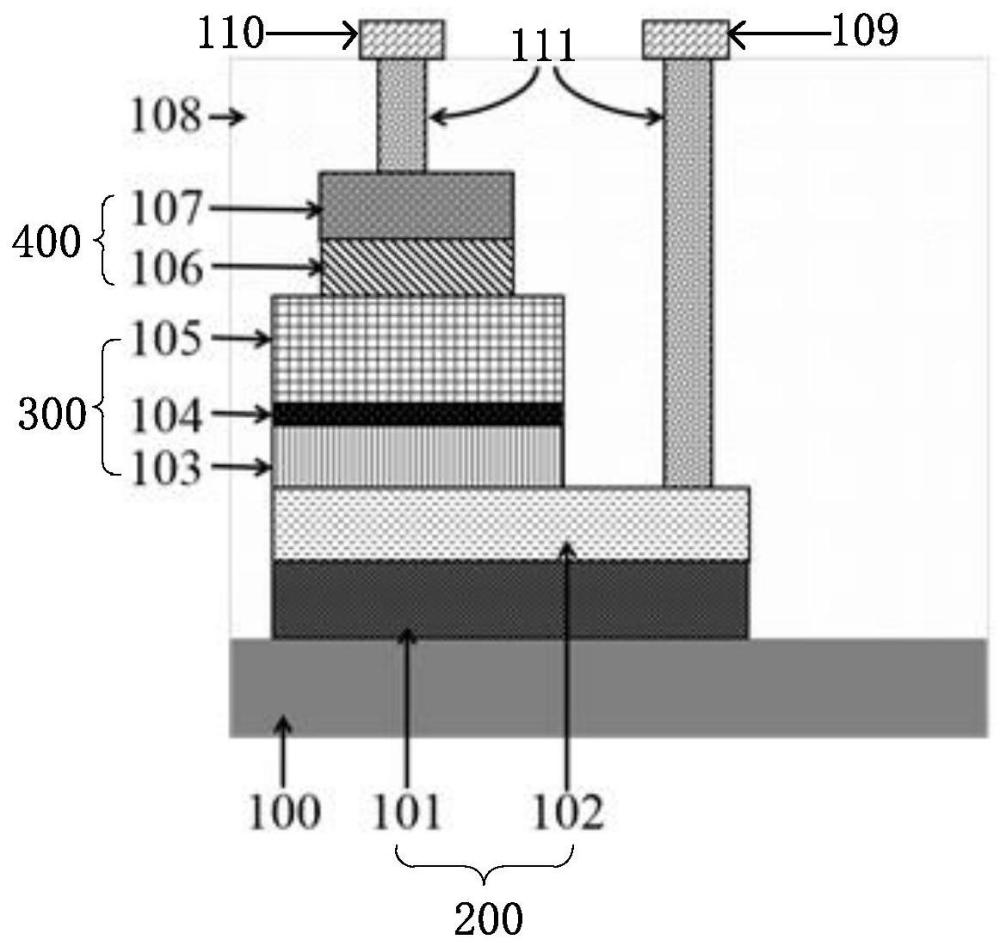

2、本发明一方面提供一种肖特基势垒二极管,包括:衬底;

3、第一电极结构层,位于所述衬底之上;所述第一电极结构层包括第一电极层;

4、半导体结构层,位于所述第一电极层背离所述衬底的一侧;

5、第二电极结构层,所述第二电极结构层包括第二电极层,所述第二电极层位于所述半导体结构背离所述第一电极结构层的一侧;

6、所述半导体结构层包括:

7、第一半导体层,位于所述第一电极层背离所述衬底的一侧;

8、第二半导体层,位于所述第一半导体层背离所述第一电极层的一侧;

9、第三半导体层,位于所述第二半导体层背离所述第一半导体层的一侧;所述第一半导体层和所述第三半导体层的材料均为铟铝锌氧化物,所述第一半导体层和所述第三半导体层的电阻不同,所述第二半导体层的导电性优于所述第一半导体层和所述第三半导体层;

10、所述半导体结构层与一侧相邻的电极层形成肖特基接触,与另一侧相邻的电极层形成欧姆接触。

11、本发明的一些实施例中,与相邻的电极层形成肖特基接触的半导体层中氧元素的含量高于与相邻的电极层形成欧姆接触的半导体层中氧元素的含量。

12、本发明的一些实施例中,所述第二半导体层采用的材料包括氧化铟、氧化锡、氧化锌、铟锡氧化物、铟锌氧化物、铝锌氧化物、氟掺杂氧化锡、石墨烯中的一种或多种;

13、所述第二半导体层的厚度小于所述第一半导体层的厚度;所述第二半导体层的厚度小于所述第三半导体层的厚度。

14、本发明的一些实施例中,与相邻的电极层形成欧姆接触的半导体层的厚度大于与相邻的电极层形成肖特基接触的半导体层的厚度。

15、本发明的一些实施例中,所述第一电极结构层还包括第三电极层;所述第三电极层位于所述衬底和所述第一电极层之间;

16、所述第三电极层采用粘附性材料,所述粘附性材料包括银、铟、镁、钛、铝、钼、铜。

17、本发明的一些实施例中,所述第二电极结构层还包括第四电极层,所述第四电极层位于所述第二电极层背离所述半导体结构层的一侧;

18、所述第四电极层用于保护所述第二电极层,所述第四电极采用的材料包括金。

19、本发明的一些实施例中,所述半导体结构层在所述衬底上的正投影面积小于所述第一电极结构层在所述衬底上的正投影面积;

20、所述半导体结构层在所述衬底上的正投影完全覆盖所述第二电极结构层在所述衬底上的正投影。

21、本发明的一些实施例中,还包括:绝缘层、第一电极和第二电极;

22、所述绝缘层覆盖所述衬底、所述第一电极结构层、所述半导体结构层、所述第二电极结构层,所述绝缘层包括多个过孔,所述过孔用于暴露出部分所述第一电极结构层和部分所述第二电极结构层;

23、所述第一电极和所述第二电极位于所述绝缘层背离所述衬底的一侧,所述第一电极通过所述过孔与所述第一电极结构层电连接,所述第二电极通过所述过孔与所述第二电极结构层电连接。

24、本发明另一方面提供一种肖特基势垒二极管的制作方法,包括:在衬底上形成第一导电材料层;

25、在所述第一导电材料层上形成第二导电材料层;

26、在所述第二导电材料层上形成第一半导体材料层;

27、在所述第一半导体材料层上形成第二半导体材料层;

28、在所述第二半导体材料层上形成第三半导体材料层;

29、在所述第三半导体材料层上形成第三导电材料层;

30、在所述第三导电材料层上形成第四导电材料层;

31、对所述第四导电材料层、所述第三导电材料层、所述第三半导体材料层、所述第二半导体材料层、所述第一半导体材料层进行图形化处理,形成第二电极结构层、半导体结构层和第一电极结构层;

32、在所述衬底、第一电极结构层、半导体结构层和第二电极结构层上覆盖绝缘层;

33、对所述绝缘层进行打孔暴露出部分所述第一电极结构层和部分所述第二电极结构层;

34、在所述绝缘层上形成第五导电材料层;

35、对所述第五导电材料层进行图形化处理,形成第一电极和第二电极;所述第一电极通过所述绝缘层的过孔与所述第一电极结构层电连接,所述第二电极通过所述绝缘层的过孔与所述第二电极结构层电连接。

36、本发明的一些实施例中,在形成所述第一半导体材料层和所述第三半导体材料层时在制备环境中通入不同含量的氧气。

37、本发明有益效果如下:

38、本发明提供的肖特基势垒二极管及其制作方法,肖特基势垒二极管包括:衬底;第一电极结构层,位于衬底之上;第一电极结构层包括第一电极层;半导体结构层,位于第一电极层背离衬底的一侧;第二电极结构层,第二电极结构层包括第二电极层,第二电极层位于半导体结构背离第一电极结构层的一侧;半导体结构层包括:第一半导体层,位于第一电极层背离衬底的一侧;第二半导体层,位于第一半导体层背离第一电极层的一侧;第三半导体层,位于第二半导体层背离第一半导体层的一侧;第一半导体层和第三半导体层的材料均为铟铝锌氧化物,第一半导体层和第三半导体层的电阻不同,第二半导体层的导电性优于第一半导体层和第三半导体层;半导体结构层与一侧相邻的电极层形成肖特基接触,与另一侧相邻的电极层形成欧姆接触,分别对两侧的半导体层进行调节,可以提高对应接触面的接触质量,加入高导电性的半导体层,还可以降低器件的串联电阻,有利于提升器件的性能。

技术特征:1.一种肖特基势垒二极管,其特征在于,包括:

2.如权利要求1所述的肖特基势垒二极管,其特征在于,与相邻的电极层形成肖特基接触的半导体层中氧元素的含量高于与相邻的电极层形成欧姆接触的半导体层中氧元素的含量。

3.如权利要求1所述的肖特基势垒二极管,其特征在于,所述第二半导体层采用的材料包括氧化铟、氧化锡、氧化锌、铟锡氧化物、铟锌氧化物、铝锌氧化物、氟掺杂氧化锡、石墨烯中的一种或多种;

4.如权利要求1所述的肖特基势垒二极管,其特征在于,与相邻的电极层形成欧姆接触的半导体层的厚度大于与相邻的电极层形成肖特基接触的半导体层的厚度。

5.如权利要求1所述的肖特基势垒二极管,其特征在于,所述第一电极结构层还包括第三电极层;所述第三电极层位于所述衬底和所述第一电极层之间;

6.如权利要求1所述的肖特基势垒二极管,其特征在于,所述第二电极结构层还包括第四电极层,所述第四电极层位于所述第二电极层背离所述半导体结构层的一侧;

7.如权利要求1所述的肖特基势垒二极管,其特征在于,所述半导体结构层在所述衬底上的正投影面积小于所述第一电极结构层在所述衬底上的正投影面积;

8.如权利要求7所述的肖特基势垒二极管,其特征在于,还包括:绝缘层、第一电极和第二电极;

9.一种肖特基势垒二极管的制作方法,其特征在于,包括:

10.如权利要求9所述的制作方法,其特征在于,在形成所述第一半导体材料层和所述第三半导体材料层时在制备环境中通入不同含量的氧气。

技术总结本发明公开了一种肖特基势垒二极管及其制作方法,肖特基势垒二极管包括:衬底、第一电极结构层、半导体结构层和第二电极结构层;半导体结构层包括:第一半导体层、第三半导体层和二者之间的第二半导体层;第一半导体层和第三半导体层的材料均为铟铝锌氧化物,第一半导体层和第三半导体层的电阻不同,第二半导体层的导电性优于第一半导体层和第三半导体层;半导体结构层与一侧相邻的电极层形成肖特基接触,与另一侧相邻的电极层形成欧姆接触,分别对两侧的半导体层进行调节,可以提高对应接触面的接触质量,加入高导电性的半导体层,还可以降低器件的串联电阻,有利于提升器件的性能。技术研发人员:徐伟东,孙明晓,李阳,谢静超,李敏华受保护的技术使用者:海信视像科技股份有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/319743.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表