一种平面高压器件的制作方法

- 国知局

- 2024-10-21 15:19:30

本发明实施例涉及集成电路,尤其涉及一种平面高压器件。

背景技术:

1、对于高压集成电路领域中高压器件的设计,为了方便与互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)器件集成,传统方式会选择平面多晶硅栅极工艺,这导致了器件的耐压提升的同时,导通电阻明显增加。换言之,传统平面式横向扩散金属氧化物半导体(laterally diffused metal oxide semiconductor,ldmos)器件会存在导通电阻大、耐压低的问题。

2、现有为了保证高压器件耐压不受影响的同时降低导通电阻,会采用优化耐压漂移区的掺杂形貌,耐压区的制造方法,或者采用不同的掺杂方式来实现。然而,该些方式对于提高耐压同时降低导通电阻无法达到更好的平衡,无法较好地解决提升耐压的同时降低导通电阻的问题。

技术实现思路

1、本发明提供一种平面高压器件,以显著的提升器件的耐压值,同时降低器件的导通电阻。

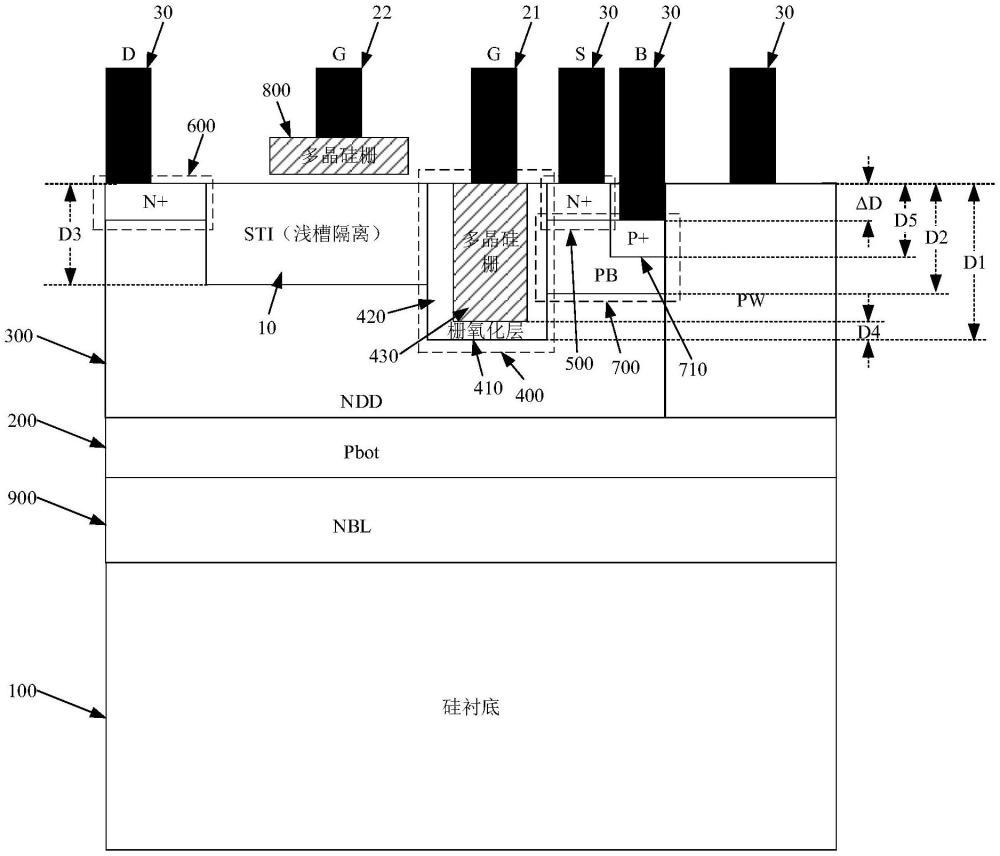

2、第一方面,本发明实施例提供了一种平面高压器件,包括:

3、半导体衬底;

4、p型隔离层,位于所述半导体衬底上方;

5、n型漂移层,位于所述p型隔离层的上方;

6、栅区、源区、漏区和体区,位于所述n型漂移层上方;所述体区、所述栅区和所述漏区在水平方向排列,且所述栅区位于所述体区和所述漏区之间,所述源区位于所述体区上方且与所述栅区邻接;

7、所述栅区包括栅极深槽以及位于所述栅极深槽中的第一栅氧化层和第一多晶硅栅,所述第一栅氧化层包裹所述第一多晶硅栅;

8、所述栅区和所述漏区之间设置有浅槽隔离区,所述栅极深槽的深度大于所述体区和所述浅槽隔离区的深度。

9、可选地,所述浅槽隔离区上方设置有第二多晶硅栅,所述第一多晶硅栅通过纵向硅栅接触孔、所述第二多晶硅栅通过平面硅栅接触孔与栅极金属层连接。

10、可选地,所述栅极深槽的深度范围为0.3~3um,和/或,所述第一栅氧化层的厚度范围为20nm~1000nm。

11、可选地,所述源区和所述漏区均包括n型重掺区,所述源区中的所述n型重掺区通过接触孔连接至源极金属层;所述漏区中的所述n型重掺区通过接触孔连接至漏极金属层。

12、可选地,所述体区包括体极深槽以及位于所述体极深槽中的p型重掺区,所述体极深槽中的所述p型重掺区通过接触孔连接体极金属层;所述体极深槽的深度小于所述体区的深度。

13、可选地,所述体区中的所述p型重掺区的上表面低于所述源区的所述n型重掺区的上表面。

14、可选地,所述体区的深度范围为0.3~3um,和/或,所述体区中的所述p型重掺区的上表面与所述源区的所述n型重掺区的上表面的深度差范围为0.3~3um。

15、可选地,

16、所述体区中的所述p型重掺区与所述源区的所述n型重掺区上表面平齐且深度相同。

17、可选地,还包括p型阱区,所述p型阱区位于所述p型隔离层上方且与所述n型漂移层在水平方向邻接;所述p型阱区通过接触孔与外部连接。

18、可选地,所述半导体衬底还包括n型埋层,所述n型埋层位于所述半导体衬底和所述p型隔离层之间。

19、本发明的技术方案中,平面高压器件设置包括半导体衬底、p型隔离层、n型漂移层、栅区、源区、漏区和体区,其中,p型隔离层位于半导体衬底上方,n型漂移层位于p型隔离层的上方,栅区、源区、漏区和体区位于n型漂移层上方,体区、栅区和漏区在水平方向排列,且栅区位于体区和漏区之间,源区位于体区上方且与栅区邻接;栅区包括栅极深槽以及位于栅极深槽中的第一栅氧化层和第一多晶硅栅,第一栅氧化层包裹第一多晶硅栅;栅区和漏区之间设置有浅槽隔离区,栅极深槽的深度大于体区和浅槽隔离区的深度。本发明实施例解决了现有平面高压器件无法较好地解决提升耐压的同时降低导通电阻的问题,能够利用深槽栅结构配合p型隔离层调控n型漂移层中的导电通道,从而显著地降低平面高压dmos器件的导通电阻,同时显著地增加器件耐压值。

技术特征:1.一种平面高压器件,其特征在于,包括:

2.根据权利要求1所述的平面高压器件,其特征在于,所述浅槽隔离区上方依次设置有第二栅氧化层和第二多晶硅栅,所述第一多晶硅栅通过纵向硅栅接触孔、所述第二多晶硅栅通过平面硅栅接触孔与栅极金属层连接。

3.根据权利要求1所述的平面高压器件,其特征在于,所述栅极深槽的深度范围为0.3~3um,和/或,所述第一栅氧化层的厚度范围为20nm~1000nm。

4.根据权利要求1所述的平面高压器件,其特征在于,所述源区和所述漏区均包括n型重掺区,所述源区中的所述n型重掺区通过接触孔连接至源极金属层;所述漏区中的所述n型重掺区通过接触孔连接至漏极金属层。

5.根据权利要求4所述的平面高压器件,其特征在于,所述体区包括体极深槽以及位于所述体极深槽中的p型重掺区,所述体极深槽中的所述p型重掺区通过接触孔连接体极金属层;所述体极深槽的深度小于所述体区的深度。

6.根据权利要求5所述的平面高压器件,其特征在于,所述体区中的所述p型重掺区的上表面低于所述源区的所述n型重掺区的上表面。

7.根据权利要求6所述的平面高压器件,其特征在于,所述体区的深度范围为0.3~3um,和/或,所述体区中的所述p型重掺区的上表面与所述源区的所述n型重掺区的上表面的深度差范围为0.3~3um。

8.根据权利要求5所述的平面高压器件,其特征在于,所述体区中的所述p型重掺区与所述源区的所述n型重掺区上表面平齐且深度相同。

9.根据权利要求1所述的平面高压器件,其特征在于,还包括p型阱区,所述p型阱区位于所述p型隔离层上方且与所述n型漂移层在水平方向邻接;所述p型阱区通过接触孔与外部连接。

10.根据权利要求1所述的平面高压器件,其特征在于,所述半导体衬底还包括n型埋层,所述n型埋层位于所述半导体衬底和所述p型隔离层之间。

技术总结本发明实施例公开了一种平面高压器件。该平面高压器件包括半导体衬底、P型隔离层、N型漂移层、栅区、源区、漏区和体区,其中,P型隔离层位于半导体衬底上方,N型漂移层位于P型隔离层的上方,栅区、源区、漏区和体区位于N型漂移层上方,体区、栅区和漏区在水平方向排列,且栅区位于体区和漏区之间,源区位于体区上方且与栅区邻接;栅区包括栅极深槽以及位于栅极深槽中的第一栅氧化层和第一多晶硅栅,第一栅氧化层包裹第一多晶硅栅;栅区和漏区之间设置有浅槽隔离区,栅极深槽的深度大于体区和浅槽隔离区的深度。本发明实施例能够显著地降低平面高压DMOS器件的导通电阻,同时显著地增加器件耐压值。技术研发人员:沈忱受保护的技术使用者:苏州珂晶达电子有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/321226.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

封装结构和封装方法与流程

下一篇

返回列表