电子器件用基板及其制造方法与流程

- 国知局

- 2024-11-06 15:09:26

本发明涉及一种电子器件用基板及其制造方法,尤其涉及一种在硅基板上形成有氮化物半导体的电子器件用基板及其制造方法。

背景技术:

1、以gan和aln为首的氮化物半导体能够用于使用了二维电子气体的高电子迁移率晶体管(hemt)和高耐压电子器件的制作。

2、难以制作在基板上生长这些氮化物半导体而成的氮化物半导体晶圆,以往,作为生长用基板,使用蓝宝石基板和sic基板。但是为了基板的大直径化(大口径化)和抑制基板的成本,也进行基于对单晶硅基板上的气相生长的氮化物半导体的外延生长。对于基于对单晶硅基板上的气相生长的氮化物半导体的外延生长膜的制作,与蓝宝石基板和sic基板相比,能够使用大直径基板,因此在器件的生产性高并且容易加工方面是有利的。但是,在对单晶硅基板上的氮化物半导体的气相生长中,由于因晶格常数差和热膨胀系数差产生的应力,容易发生翘曲的增加和滑移、破裂等,而进行基于生长条件和缓和层的应力降低。

3、特别地,要使功率器件用的外延基板变得高耐压,需要制作gan的外延层的厚度增厚的gan on si(单晶硅上的gan)。要使外延层的厚度增厚,只要使生长用基板即单晶硅基板增厚而进行外延生长即可。并且,作为使单晶硅基板增厚的方法,进行将2片单晶硅基板进行贴合的步骤。专利文献1中公开了将经贴合的基板的厚度设为2mm以上。此外,在专利文献2中,作为要贴合的2片基板的组合,公开了:接合晶圆为面取向{111},且基底基圆为面取向{100},且电阻率为0.1ωcm以下。

4、现有技术文献

5、专利文献

6、专利文献1:日本特开2021-014376号公报

7、专利文献2:日本特开2021-027186号公报

技术实现思路

1、(一)要解决的技术问题

2、如上所述,已知如专利文献1、专利文献2所公开那样的将贴合基板用作生长用基板的技术。然而,即使使用这些贴合基板,仍无法完全地抑制翘曲的增加和滑移、破裂等的发生。此外,滑移、破裂等大多主要发生在基板的缺口部。一般而言,在{111}单晶硅基板中,在<110>方向上形成有缺口,在{100}单晶硅基板中,在<110>方向或<100>方向上形成。

3、本发明为了解决上述问题而做出,其目的在于提供一种滑移、破裂等的发生得到抑制、破坏强度高的电子器件用基板及其制造方法,该电子器件用基板在单晶硅上形成有氮化物半导体。

4、(二)技术方案

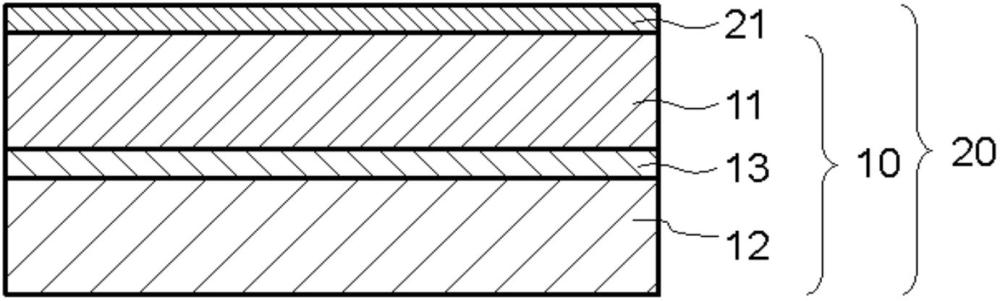

5、为了解决上述问题,本发明提供一种电子器件用基板,其在单晶硅的结合基板上形成有氮化物半导体膜,其特征在于,

6、所述结合基板是隔着氧化膜将第一单晶硅基板与第二单晶硅基板结合而成的基板,其中,所述第一单晶硅基板的晶面取向是{111},所述第二单晶硅基板的主面相对于晶面取向{100}具有偏角,

7、在所述结合基板的所述第一单晶硅基板的表面上,形成有所述氮化物半导体膜。

8、关于晶面取向,并非如通常的第二单晶硅基板那样是不具偏角的just基板,通过设为如本发明的第二单晶硅基板那样具有偏角,解理面相对于主面(与第一单晶硅基板的结合面)会呈非垂直(解理面呈倾斜)。这样,即使只有1片第二单晶硅基板,解理面也会倾斜,由此,与第二单晶硅基板的解理面相对于结合面也呈垂直的现有产品的情况相比,能够制作翘曲的增加和滑移、破裂(以下也称为破裂等)的发生得到抑制的、破坏强度高的电子器件用基板。

9、在这种情况下,可以是,所述第二单晶硅基板是氮掺杂的基板。

10、如果是这样的结构,则成为破坏强度更高的电子器件用基板。

11、此外,可以是,

12、所述第一单晶硅基板是在<110>方向形成有缺口的基板,

13、所述第二单晶硅基板是在<110>方向形成有缺口的基板,

14、所述结合基板是以使所述第一单晶硅基板的缺口的位置与所述第二单晶硅基板的缺口的位置一致的方式结合而成的基板。

15、如果是这样的结构,则通过要进行贴合的第一单晶硅基板与第二单晶硅基板的解理面的位置关系,成为破裂等的发生得到进一步抑制的、破坏强度高的电子器件用基板。

16、此外,可以是,所述结合基板的直径是300mm以上。

17、这样,本发明的破坏强度高的基板对于直径为300mm以上这样的大直径的电子器件用基板特别有效。

18、此外,本发明提供一种电子器件用基板的制造方法,所述电子器件用基板在单晶硅的结合基板上形成氮化物半导体膜,其特征在于,具有以下工序:

19、准备第一单晶硅基板及第二单晶硅基板,其中,所述第一单晶硅基板的晶面取向是{111},所述第二单晶硅基板的主面相对于晶面取向{100}具有偏角;

20、将所述第一单晶硅基板及所述第二单晶硅基板中的至少一个基板进行热氧化,而在表面形成氧化膜;

21、隔着所述氧化膜将所述第一单晶硅基板与所述第二单晶硅基板重合,并进行热处理,从而将所述第一单晶硅基板与所述第二单晶硅基板结合,制作所述结合基板;以及

22、在所述结合基板的所述第一硅单晶单晶硅基板的表面上外延生长所述氮化物半导体膜。

23、如果是这样的本发明的电子器件用基板的制造方法,则包含解理面相对于结合面倾斜的第二单晶硅基板,而能够制造破裂等的发生得到抑制的、破坏强度高的电子器件用基板。

24、在这种情况下,可以是,将准备的所述第二单晶硅基板设为氮掺杂的基板。

25、如果这样操作,则能够制造破坏强度更高的电子器件用基板。

26、此外,可以是,将准备的所述第一单晶硅基板设为在<110>方向形成有缺口的基板,

27、将准备的所述第二单晶硅基板设为在<110>方向形成有缺口的基板,

28、以所述第一单晶硅基板的缺口的位置与所述第二单晶硅基板的缺口的位置一致的方式进行重合并结合。

29、如果这样操作,则通过要进行贴合的第一单晶硅基板与第二单晶硅基板的解理面的位置关系,能够制造破裂等的发生得到更进一步的抑制的、破坏强度高的电子器件用基板。

30、此外,可以是,将准备的所述第一单晶硅基板及所述第二单晶硅基板的直径设为300mm以上。

31、通过本发明的制造方法制造出的电子器件用基板这样的、破坏强度高的基板,对于制造直径为300mm以上这样的大直径的电子器件用基板特别有效。

32、(三)有益效果

33、如果是如本发明的电子器件用基板及其制造方法,则具备解理面相对于结合面倾斜并具有偏角的第二单晶硅基板,因此能够提供一种破裂等的发生得到抑制的、破坏强度高的电子器件用基板。

技术特征:1.一种电子器件用基板,其在单晶硅的结合基板上形成有氮化物半导体膜,其特征在于,

2.根据权利要求1所述的电子器件用基板,其特征在于,

3.根据权利要求1所述的电子器件用基板,其特征在于,

4.根据权利要求2所述的电子器件用基板,其特征在于,

5.根据权利要求1-4中任一项所述的电子器件用基板,其特征在于,

6.一种电子器件用基板的制造方法,所述电子器件用基板在单晶硅的结合基板上形成氮化物半导体膜,其特征在于,具有以下工序:

7.根据权利要求6所述的电子器件用基板的制造方法,其特征在于,

8.根据权利要求6所述的电子器件用基板的制造方法,其特征在于,

9.根据权利要求7所述的电子器件用基板的制造方法,其特征在于,

10.根据权利要求6-9中任一项所述的电子器件用基板的制造方法,其特征在于,

技术总结本发明是一种电子器件用基板,其在单晶硅的结合基板上形成有氮化物半导体膜,所述结合基板是隔着氧化膜将第一单晶硅基板与第二单晶硅基板结合而成的基板,其中,所述第一单晶硅基板的晶面取向是{111},所述第二单晶硅基板的主面相对于晶面取向{100}具有偏角,在所述结合基板的所述第一单晶硅基板的表面上,形成有所述氮化物半导体膜。由此,提供一种滑移、破裂等的发生得到抑制、破坏强度高的电子器件用基板及其制造方法,该电子器件用基板在单晶硅上形成有氮化物半导体。技术研发人员:萩本和德,菅原孝世,田中佑宜,阿贺浩司受保护的技术使用者:信越半导体株式会社技术研发日:技术公布日:2024/11/4本文地址:https://www.jishuxx.com/zhuanli/20241106/325579.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。