半导体器件及其制备方法与流程

- 国知局

- 2024-11-18 18:20:05

本发明属于半导体,尤其涉及一种半导体器件及其制备方法。

背景技术:

1、gan材料的禁带宽度更宽,在相同击穿电压的要求下,器件尺寸可以更小而越来越多的被应用到半导体器件中。现在主流的氮化镓器件生产中依然使用平面结构器件,即栅极和漏极在半导体器件的厚度方向上大致位于同一高度,严重浪费了器件面积。

技术实现思路

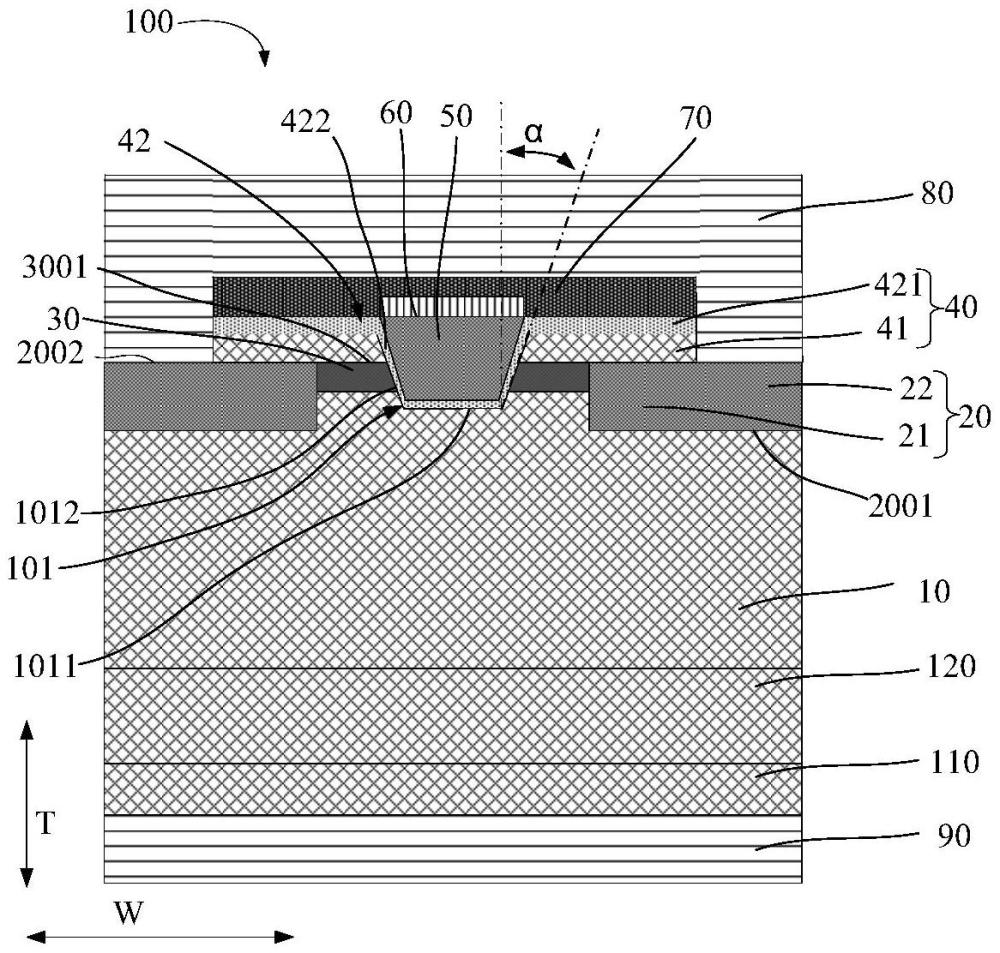

1、根据本发明实施例的第一方面,提供一种半导体器件,包括:

2、漂移层;

3、p型调制层,设于所述漂移层在所述半导体器件的厚度方向上的一侧表面的中部区域上;

4、电流阻挡层,与所述p型调制层设于所述漂移层的同一侧表面上,并位于所述p型调制层的外围;

5、沟道层,位于所述p型调制层和所述电流阻挡层背离所述漂移层的一侧,且所述沟道层覆盖所述p型调制层以及靠近所述p型调制层的部分宽度的电流阻挡层;所述电流阻挡层包括与所述沟道层重叠的第一阻挡部,及位于所述第一阻挡部外围而与所述沟道层不重叠的第二阻挡部;

6、第一沟槽,在所述半导体器件的厚度方向上贯穿所述沟道层和所述p型调制层;所述第一沟槽具有底壁和侧壁,所述侧壁呈倾斜状,且在所述第一沟槽背离所述漂移层一侧的开口尺寸大于所述底壁的尺寸;

7、势垒层,位于所述沟道层背离所述漂移层的一侧以及所述第一沟槽中且与所述势垒层接触,位于所述沟道层背离所述漂移层的一侧的势垒层与所述沟道层形成异质结结构;

8、pgan有源层,位于所述第一沟槽中;

9、栅极,位于所述pgan有源层背离所述漂移层的一侧;

10、源极,至少位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧,并与所述异质结结构接触;

11、漏极,位于所述漂移层背离所述异质结结构的一侧。

12、所述第一沟槽在垂直于所述半导体器件的厚度方向上的截面呈圆形;和/或,

13、所述第一沟槽的侧壁在平行于所述半导体器件的厚度方向的平面上的正投影,与所述半导体器件的厚度方向之间的夹角为30°-45°。

14、在一些实施例中,在所述半导体器件的厚度方向上,所述第一沟槽的底壁高于所述电流阻挡层朝向所述漂移层一侧的底表面。

15、在一些实施例中,所述电流阻挡层背离所述漂移层一侧的顶表面与所述p型调制层背离所述漂移层一侧的顶表面的高度齐平,或者,所述电流阻挡层背离所述漂移层一侧的顶表面高于所述p型调制层背离所述漂移层一侧的顶表面。

16、在一些实施例中,所述半导体器件为pgan结构gan功率器件,所述栅极为肖特基金属;和/或,

17、所述电流阻挡层的材质为p型氮化镓。

18、在一些实施例中,所述半导体器件还包括:

19、钝化层,所述钝化层位于所述栅极以及所述势垒层背离所述漂移层的一侧;

20、所述源极位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧以及所述钝化层背离所述漂移层的一侧。

21、根据本发明实施例的第二方面,提供一种半导体器件,所述半导体器件包括:

22、漂移层;

23、电流阻挡层,设于所述漂移层在所述半导体器件的厚度方向上一侧的表面的外围区域,所述漂移层中设有所述电流阻挡层的表面中部区域自所述电流阻挡层中部外露;

24、沟道层,位于所述漂移层和所述电流阻挡层的同一侧,且所述沟道层包覆自所述电流阻挡层中部外露的漂移层以及部分宽度的电流阻挡层;所述电流阻挡层包括与所述沟道层重叠的第一阻挡部,及位于所述第一阻挡部外围而与所述沟道层不重叠的第二阻挡部;

25、第二沟槽,在所述半导体器件的厚度方向上贯穿所述沟道层;所述第二沟槽具有底壁和侧壁,所述侧壁呈倾斜状,且在所述第二沟槽背离所述漂移层一侧的开口尺寸大于所述底壁的尺寸;

26、势垒层,位于所述沟道层背离所述漂移层的一侧以及所述第二沟槽中,位于所述沟道层背离所述漂移层的一侧的势垒层与所述沟道层形成异质结结构;

27、pgan有源层,位于所述第二沟槽中且与所述势垒层接触;

28、栅极,位于所述pgan有源层背离所述漂移层的一侧

29、栅极,位于所述pgan有源层背离所述漂移层的一侧;

30、源极,至少位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧,并与所述异质结结构接触;

31、漏极,位于所述漂移层背离所述异质结结构的一侧。

32、在一些实施例中,所述第二沟槽在垂直于所述半导体器件的厚度方向上的截面呈圆形;和/或,

33、所述第二沟槽的侧壁在平行于所述半导体器件的厚度方向的平面上的正投影,与所述半导体器件的厚度方向之间的夹角为30°-45°;和/或,

34、在所述半导体器件的厚度方向上,所述第二沟槽的底壁高于所述电流阻挡层朝向所述漂移层一侧的底表面;和/或,

35、所述半导体器件为pgan结构gan功率器件,所述栅极为肖特基金属;和/或,

36、所述电流阻挡层的材质为p型氮化镓;和/或,

37、所述半导体器件还包括钝化层,所述钝化层位于所述栅极以及所述势垒层背离所述漂移层的一侧;

38、所述源极位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧以及所述钝化层背离所述漂移层的一侧。

39、根据本发明实施例的第三方面,提供一种半导体器件的制备方法,其包括:

40、提供衬底,并在所述衬底的一侧形成漂移层;

41、在所述漂移层背离所述衬底一侧的表面中部区域形成p型调制层;

42、在所述漂移层背离所述衬底一侧的表面形成位于所述p型调制层外围的电流阻挡层;

43、在所述p型调制层和所述电流阻挡层背离所述漂移层的一侧形成沟道层、第一沟槽、势垒层、pgan有源层以及栅极;所述沟道层覆盖所述p型调制层以及靠近所述p型调制层的部分宽度的电流阻挡层;所述电流阻挡层包括与所述沟道层重叠的第一阻挡部,及位于所述第一阻挡部外围而与所述沟道层不重叠的第二阻挡部;所述第一沟槽在所述半导体器件的厚度方向上贯穿所述沟道层和所述p型调制层;所述第一沟槽具有底壁和侧壁,所述侧壁呈倾斜状,且在所述第一沟槽背离所述漂移层一侧的开口尺寸大于所述底壁的尺寸;势垒层位于所述沟道层背离所述漂移层的一侧以及所述第一沟槽中,并且位于所述沟道层背离所述漂移层的一侧的势垒层与所述沟道层形成异质结结构;pgan有源层位于所述第一沟槽中且与所述势垒层接触;栅极位于所述pgan有源层背离所述漂移层的一侧;

44、形成源极,所述源极至少位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧,并与所述异质结结构接触;

45、去除所述衬底并形成漏极,所述漏极位于所述漂移层背离所述异质结结构的一侧。

46、在一些实施例中,在提供衬底之后,在所述衬底的一侧形成漂移层之前,所述方法包括:

47、在所述衬底的一侧形成成核层及缓冲层,所述成核层为aln层,所述缓冲层包括依序层叠于所述成核层上的algan层、交错堆叠的多层aln/gan层、低温gan层以及高温gan层;

48、所述在所述衬底的一侧形成漂移层包括:

49、在所述缓冲层背离所述衬底的一侧形成漂移层。

50、在一些实施例中,在去除衬底之时或去除衬底之后,在形成漏极之前,所述方法还包括:

51、去除所述成核层;或者,

52、去除所述成核层和至少部分所述缓冲层。

53、在一些实施例中,在形成源极之前,所述方法还包括:

54、形成钝化层,所述钝化层位于所述栅极以及所述势垒层背离所述漂移层的一侧;

55、在形成源极之后,所述源极位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧以及所述钝化层背离所述漂移层的一侧。

56、根据本发明实施例的第四方面,提供一种半导体器件的制备方法,其包括:

57、提供衬底,并在所述衬底的一侧形成漂移层;

58、在所述漂移层在所述半导体器件的厚度方向上一侧的表面的外围区域形成电流阻挡层;所述漂移层中设有所述电流阻挡层的表面中部区域自所述电流阻挡层中部外露;

59、在所述漂移层和所述电流阻挡层的同一侧形成沟道层、第二沟槽、势垒层、pgan有源层以及栅极,所述沟道层包覆自所述电流阻挡层中部外露的漂移层以及部分宽度的电流阻挡层;所述电流阻挡层包括与所述沟道层重叠的第一阻挡部,及位于所述第一阻挡部外围而与所述沟道层不重叠的第二阻挡部;所述第二沟槽在所述半导体器件的厚度方向上贯穿所述沟道层;所述第二沟槽具有底壁和侧壁,所述侧壁呈倾斜状,且在所述第二沟槽背离所述漂移层一侧的开口尺寸大于所述底壁的尺寸;势垒层位于所述沟道层背离所述漂移层的一侧以及所述第二沟槽中,并且位于所述沟道层背离所述漂移层的一侧的势垒层与所述沟道层形成异质结结构;pgan有源层位于所述第二沟槽中;栅极位于所述pgan有源层背离所述漂移层的一侧;

60、形成源极,所述源极至少位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧,并与所述异质结结构接触;

61、去除所述衬底并形成漏极,所述漏极位于所述漂移层背离所述异质结结构的一侧。

62、在一些实施例中,在提供衬底之后,在所述衬底的一侧形成漂移层之前,所述方法包括:

63、在所述衬底的一侧形成成核层及缓冲层,所述成核层为aln层,所述缓冲层包括依序层叠于所述成核层上的algan层、交错堆叠的多层aln/gan层、低温gan层以及高温gan层;

64、所述在所述衬底的一侧形成漂移层包括:

65、在所述缓冲层背离所述衬底的一侧形成漂移层;

66、在去除衬底之时或去除衬底之后,在形成漏极之前,所述方法还包括:

67、去除所述成核层;或者,

68、去除所述成核层和至少部分所述缓冲层。

69、在一些实施例中,在形成源极之前,所述方法还包括:

70、形成钝化层,所述钝化层位于所述栅极以及所述势垒层背离所述漂移层的一侧;

71、在形成源极之后,所述源极位于所述电流阻挡层的第二阻挡部背离所述漂移层一侧以及所述钝化层背离所述漂移层的一侧。

72、本技术实施例所达到的主要技术效果是:

73、本技术实施例提供的半导体器件及其制备方法,将半导体器件设置为垂直结构,有利于控制半导体器件所在器件的体积,并且通过在源极下方的电流阻挡层的阻挡作用,可以降低关断漏电,从而达到更好的可靠性和更低的功耗。在栅极下方pgan有源层的设置,可以将势垒层高度提高,将栅极下方沟槽处的势能抬高到费米能级之上,漂移层与势垒层界面处会形成高的电子势垒,将电子更好地被约束在2deg沟道内提升了电子迁移率。并且,栅极下方的沟槽的侧壁设置呈倾斜状,有利于提高异质结结构的二维电子气浓度,有利于降低或避免电路通路阻值较大的风险。

本文地址:https://www.jishuxx.com/zhuanli/20241118/328256.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表