一种适用于DDRPHY的时钟电路的制作方法

- 国知局

- 2024-11-21 12:18:03

本发明涉及电子电路,具体涉及一种适用于ddrphy的时钟电路。

背景技术:

1、随着对存储带宽速度的要求,ddr的速率不断攀升,存储器信号接口的内部的时钟频率也同步提升,目前lpddr5x颗粒的信息传输率一般在8533mbps,最高可以达到9600mbps。业内对于ddrphy的内部高速时钟,一般有两种方式,即full mode和half mode。如果采用full mode结构,存储器信号接口的内部高速时钟周期等于1ui,那么存储器信号接口的内部高速时钟频率在8.5g。速度太高,一方面数字时序收敛很困难,另一方面内部功耗都会增加不少,时钟质量也不容易保证。所以对于ddrphy,在这么高的速率下,采用halfmode结构,让外部信号接口的芯片内部的高速时钟频率等于信息传输率的一半,即lpddr5x外部信号接口的芯片内部高速时钟在4.2g,相对于full mode,降低时钟频率,也可以提升ppa等指标。

2、对于half mode,需要内部时钟两路时钟分别打出上升沿和下降沿,进行并串转换后,合成8533mbps信息传输率与动态随机存储器颗粒进行匹配。目前有通过探头时间偏差校准的锁相环,让锁相环出两路4.2g的时钟,一路作为打出上升沿的时钟,另一路作为打出下降沿的时钟,这种方式时钟分叉比较早,时钟路径偏移要求比较严格,时钟的偏差对于后期数字送往模拟的上升沿和下降沿的电路工作量会有比较大的影响,从而造成传输路径上的数据时序裕量不够。也有通过数字来实现时钟架构,最终在数字部分把上升沿和下降沿并转串送往io打出去。这种方式数字难以把握最后一级上升沿和下降沿合并之后送往io数据的占空比,从而导致最终io打出去的时序裕量有偏差,甚至不满足动态随机存储器的规格。时钟分叉较早会导致开路电压比较大,不同时钟的延迟影响后面送往io的时序裕量。如果分叉在最后一级,靠数字部分把上升沿和下降沿并转串送往io,经过选择器反相器,会影响高速信号占空比,甚至打出去的数据信号不满足动态随机存储器的规范。

技术实现思路

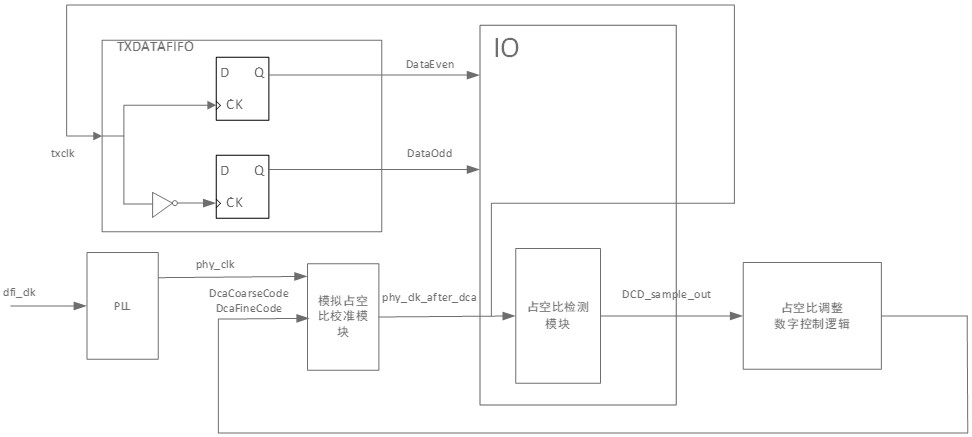

1、本发明的目的是提供一种适用于ddrphy的时钟电路,该电路能够让时钟在最后一级分叉,打出偶数数据和奇数数据给模拟io,同时通过占空比检测模块,搭配数字控制逻辑,保证时钟的电路工作量,同时让数据的时序裕量达到最好。

2、一种适用于ddrphy的时钟电路,包括:占空比检测模块和模拟占空比校准模块;

3、所述占空比检测模块位于模拟io模块中,用于检测高速信号的占空比;

4、所述模拟占空比校准模块位于模拟io模块外并与所述占空比检测模块连接,用于校准模拟比较器的正负端。

5、优选地,还包括:数字逻辑控制模块;

6、所述数字逻辑控制模块的输入端与所述占空比检测模块的输出端相连;

7、所述数字逻辑控制模块的输出端与所述模拟占空比校准模块的输入端连接;

8、所述数字逻辑控制模块用于根据所述占空比检测模块的输出产生调节代码,并将调节代码发送到所述占空比校准模块。

9、优选地,还包括: 锁相环、第一触发器、第二触发器、第一非门和模拟io模块;

10、所述锁相环的输出端与所述模拟占空比校准模块的输入端相连;

11、第一触发器的q端与所述模拟io模块相连;

12、第二触发器的q端与所述模拟io模块相连;

13、第一触发器的ck端与第一非门的输入端相连;

14、第一非门的输出端与第二触发器的ck端相连;

15、所述占空比检测模块的输入端与所述第一触发器的ck端和所述第一非门的输入端相连。

16、优选地,所述占空比检测模块包括:滤波模块和检测模块;

17、所述滤波模块与所述检测模块连接,包括:第一电容、第一电感、第一电阻和第二电容;

18、所述第一电容的上极板和第一电感的第一端均连接到浪涌保护模块,所述第一电容的第二端接地;

19、所述第一电感的第二端通过第三电容接地,第一电感的第二端连接到衬底选通模块;

20、所述第二电容的上极板与第一电感相连,下极板接地;

21、所述第一电阻的第一端与所述第二电容的上极板连接,所述第一电阻的第二端与所述第一电感连接。

22、优选地,所述检测模块包括:第一检测支路和第二检测支路;

23、所述第一检测支路由经过滤波模块的时钟信号的低电平控制,用于检测时钟信号的高电平;

24、所述第二检测支路由经过滤波模块的时钟信号的反信号控制,用于检测时钟信号的低电平。

25、优选地,所述模拟占空比校准模块包括:第二电阻、第三电阻、第四电阻、第五电阻、第三电容、第四电容、第二非门、第三非门和第一比较器;

26、所述第二电阻与第三电容并联,并与第三电阻连接;

27、所述第三电阻与第二非门并联;

28、所述第三电容的第一端连接ckp,第二端连接第二非门的输入端;

29、所述第四电容的第一端连接ckn,第二端连接第三非门的输入端;

30、所述第四电阻与第四电容并联,并与第五电阻连接;

31、所述第五电阻与第三非门连接;

32、所述第二非门的输出端与所述第一比较器的正输入端连接;

33、所述第三非门的输出端与所述第一比较器的负输入端连接。

34、一种适用于ddrphy的时钟电路控制方法,包括:

35、将锁相环起振到信息传输率的一半;

36、数字逻辑控制模块根据占空比检测模块的输出产生调整代码;

37、占空比校准模块根据所述调整代码进行占空比校准。

38、优选地,所述将锁相环起振到信息传输率的一半之后,还包括:

39、占空比检测模块进行自校准,校准比较器的正负端;

40、数字逻辑控制模块根据占空比检测模块的输出,判断占空比检测模块的输出是否达到校准目标。

41、一种电子设备,包括:芯片、处理器和存储器,所述存储器用于存储计算机程序代码,所述计算机程序代码包括计算机指令,在所述芯片执行所述计算机指令的情况下,所述电子设备执行一种适用于ddrphy的时钟电路控制方法。

42、本发明的有益效果在于:1.本发明采样half mode,使存储器信号接口的内部的时钟频率降为信号传输率的一半,解决了存储器信号接口在内部高速时钟频率收敛困难的技术问题,还能够降低内部功耗;2.本发明使得时钟在最后一级分叉,ocv效应小,保证上升沿和下降沿打出去的偏差较小;3.本发明增加了占空比检测模块和占空比校准模块,能够上升沿和下降沿打出去的数据信号时序裕量充足。

技术特征:1.一种适用于ddrphy的时钟电路,其特征在于,包括:占空比检测模块和模拟占空比校准模块;

2.根据权利要求1所述的一种适用于ddrphy的时钟电路,其特征在于,还包括:数字逻辑控制模块;

3.根据权利要求1所述的一种适用于ddrphy的时钟电路,其特征在于,还包括: 锁相环、第一触发器、第二触发器、第一非门和模拟io模块;

4.根据权利要求1所述的一种适用于ddrphy的时钟电路,其特征在于,所述检测模块包括:第一检测支路和第二检测支路;

5.一种适用于ddrphy的时钟电路控制方法,应用于权利要求1-4任一项所述的一种适用于ddrphy的时钟电路,其特征在于,包括:

6.根据权利要求5所述的一种适用于ddrphy的时钟电路控制方法,其特征在于,将锁相环起振到信息传输率的一半之后,还包括:

7.一种电子设备,其特征在于,包括:芯片、处理器和存储器,所述存储器用于存储计算机程序代码,所述计算机程序代码包括计算机指令,在所述芯片执行所述计算机指令的情况下,电子设备执行如权利要求5至6中任一项所述的一种适用于ddrphy的时钟电路控制方法。

技术总结本发明的目的是提供一种适用于DDRPHY的时钟电路,该电路包括:占空比检测模块和模拟占空比校准模块;所述占空比检测模块位于模拟IO模块中,用于检测高速信号的占空比;所述模拟占空比校准模块位于模拟IO模块外并与所述占空比检测模块连接,用于校准模拟比较器的正负端。本发明能够让时钟在最后一级分叉,打出偶数数据和奇数数据给模拟IO,同时通过占空比检测模块,搭配数字控制逻辑,保证时钟的电路工作量,同时让数据的时序裕量达到最好。技术研发人员:鲍杰,刘德启受保护的技术使用者:博越微电子(江苏)有限公司技术研发日:技术公布日:2024/11/18本文地址:https://www.jishuxx.com/zhuanli/20241120/335106.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表