封装件的制作方法

- 国知局

- 2024-07-17 13:18:15

本申请涉及半导体,更具体地,涉及一种封装件。

背景技术:

1、先进的封装件一直在寻求更低的成本与更高的产量。因此,扇出器件或扇出封装件需要新的封装技术,以充分满足hpc(high performance computing,高性能计算)、ai(artificial intelligence,人工智能)、5g/6g、自动驾驶汽车等应用越来越高密度的i/o要求。

2、参考图1a所示,在现有的一种封装件10中,所有芯片12都接合在中介层14上,中介层14设置在基板16上,中介层14中设置穿过中介层14的tsv(through silicon via,穿硅通孔)(未示出),芯片12分别通过对应的重布线层13与中介层14互连。然而,tsv工艺的成本非常高,并且制程周期时间很长,并且成本和制程周期时间都很难降低。

3、参考图1b所示,在现有的另外封装件20中,在基板26上扇出芯片22。其中,图1b所示的封装件20是通过后芯片(chip last)制程制造的。如图1b所示,后芯片制程是首先在载板(未示出)上构建重布线层23,然后在重布线层23上接合芯片22以经由重布线层23扇出芯片22,然后用模塑料29进行模封(molding),再将模封后的重布线层23和芯片22接合在基板26上。并且在该封装件20中,还会将第一底部填充物51形成在芯片22与重布线层23之间,第二底部填充物52形成在重布线层23与基板26之间。

4、参考图1c所示,在现有的另外封装件30中,在基板36上扇出芯片32。封装件30是通过先芯片(chip first)制程制造的。先芯片制程是在被模塑料39模封的芯片32上构建重布线层33,然后将模封的芯片32和重布线层33接合在基板36上。在该封装件30中,只需形成围绕重布线层33的底部填充物53。通常,上述图1b的后芯片制程和图1c的先芯片制程中,形成模塑料29、39的模封过程是晶圆级模封制程,然而晶圆级模封制程的成本比条带模封(strip molding)的成本高得多。

5、另外,习知的后芯片制程是将重布线层(如图1b中的重布线层23)构建在载板上,例如2.1d ic或图1b所示的基板上扇出芯片(focos,fan-out chip on substrate)结构;或者,如图1a所示的2.5d ic结构,是将重布线层13构建在中介层14上。然而,这些重布线层都是在同一平面上铺设的,因此同一封装件中的重布线层只能够有一种规格(如层数或线宽/线距),这使得要在重布线层上并排设置的芯片的i/o(输入/输出)部件受到了限制。

技术实现思路

1、针对以上问题,本申请提出一种封装件。

2、本申请的技术方案是这样实现的:

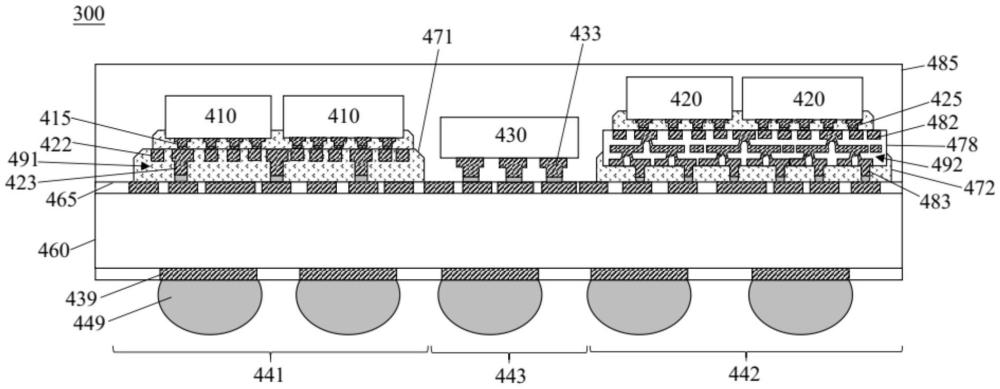

3、根据本申请的一个方面,提供了一种封装件,该封装件包括:基板,包括上表面,上表面包括第一区和第二区;第一重布线层,凸设于基板的上表面的第一区;第二重布线层,凸设于基板的上表面的第二区,并且与第一重布线层相互隔开,其中,第一重布线层和第二重布线层在厚度和线宽线距之中的至少一个方面不同。该封装件还包括:第一管芯,位于第一重布线层上方,第一输入/输出部件连接第一重布线层的上表面与第一管芯的下表面;第二管芯,位于第二重布线层上方,第二输入/输出部件连接第二重布线层的上表面与第二管芯的下表面,第一管芯的顶面与第二管芯的顶面不齐平。

4、在一些实施例中,第一重布线层的朝向基板的表面处具有内埋于第一重布线层的第一金属凸柱。

5、在一些实施例中,第二重布线层的朝向基板的表面处具有突出于第二重布线层的第二金属凸柱。

6、在一些实施例中,第一重布线层与第二重布线层具有不同的层数。

7、在一些实施例中,第一重布线层具有一层第一绝缘材料及一层第一导电线。

8、在一些实施例中,第一重布线层的一层第一导电线透过第一金属凸柱连接至基板的上表面,一层第一导电线与第一金属凸柱均由一层第一绝缘材料包覆。

9、在一些实施例中,第一重布线层和第二重布线层的线宽线距不第一重布线层和第二重布线层的线宽线距不同。

10、在一些实施例中,封装件还包括:第一管芯,具有连接于第一重布线层的上表面的第一输入/输出部件;第二管芯,具有连接于第二重布线层的上表面的第二输入/输出部件;其中,第一管芯的第一输入/输出部件的节距与第二管芯的第二输入/输出部件的节距至少相差1微米。

11、在一些实施例中,基板的上表面还包括没有设置重布线层的第三区。

12、在一些实施例中,封装件还包括第三管芯,第三管芯以倒装接合方式设置于第三区上,并且跨接于第一重布线层和第二重布线层上。

13、根据本申请的一个方面,提供了一种封装件,该封装件包括:基板,包括上表面,上表面包括第一区和第二区;第一重布线层,凸设于基板的上表面的第一区;第二重布线层,凸设于基板的上表面的第二区,并且与第一重布线层相互隔开,其中,第一重布线层和第二重布线层的线宽线距不同;第一管芯,位于第一重布线层上方,第一输入/输出部件连接第一重布线层的上表面与第一管芯的下表面;第二管芯,位于第二重布线层上方,第二输入/输出部件连接第二重布线层的上表面与第二管芯的下表面;第三管芯,跨接于第一重布线层和第二重布线层上。

14、上述技术方案的有益效果包括:可以将不同规格(如厚度和/或线宽线距)的第一重布线层和第二重布线层整合在同一表面(基板的上表面)上,并可以将不同i/o节距的第一管芯和第二管芯整合在一起,可以避免现有技术中重布线层及管芯的i/o部件受到限制的问题。

技术特征:1.一种封装件,其特征在于,包括:

2.根据权利要求1所述的封装件,其特征在于,

3.根据权利要求2所述的封装件,其特征在于,

4.根据权利要求3所述的封装件,其特征在于,

5.根据权利要求1所述的封装件,其特征在于,

6.根据权利要求5所述的封装件,其特征在于,

7.根据权利要求1所述的封装件,其特征在于,

8.根据权利要求7所述的封装件,其特征在于,还包括:

9.一种封装件,其特征在于,包括:

10.根据权利要求9所述的封装件,其特征在于,还包括:

技术总结本申请公开了一种封装件,该封装件包括:基板,基板包括上表面,上表面包括第一区和第二区;第一重布线层,设置于基板的上表面的第一区;第二重布线层,设置于基板的上表面的第二区。其中,第一重布线层和第二重布线层在厚度和线宽线距之中的至少一个方面不同。上述技术方案,可以将不同规格(如厚度和/或线宽线距)的第一重布线层和第二重布线层整合在基板的上表面上,并可以将不同I/O节距的第一管芯和第二管芯整合在一起,可以避免现有技术中重布线层及管芯的I/O部件受到限制的问题。技术研发人员:颜尤龙,博恩·卡尔·艾皮特,凯·史提芬·艾斯格受保护的技术使用者:日月光半导体制造股份有限公司技术研发日:20230707技术公布日:2024/7/9本文地址:https://www.jishuxx.com/zhuanli/20240711/108880.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表