半导体装置的制作方法

- 国知局

- 2024-07-17 12:34:19

本发明涉及端子通过接合材料与基板接合的半导体装置。

背景技术:

1、半导体装置包含功率器件,例如被用作电力转换装置。功率器件是包含igbt(insulated gate bipolar transistor:绝缘栅双极型晶体管)、功率mosfet(metal oxidesemiconductor field effect transistor:金属氧化物半导体场效应晶体管)等的半导体芯片。

2、包含半导体芯片等的电子部件介由焊料配置于陶瓷电路基板。另外,陶瓷电路基板具备绝缘板、以及形成在绝缘板上的多个导电板。在这样的半导体装置中,通过使焊料熔融并固化,从而使电子部件或者引线框架等的端子固定于导电板。但是,熔融的焊料有时会流到端子的接合区域外,因此,进行用于防止焊料流出的对策变得很重要。

3、作为相关技术,例如提出了对电路板上的镀覆膜进行激光照射而生成作为氧化膜的抗蚀剂部来排斥焊料的技术(专利文献1)。另外,提出了在铜电路图案的表面形成阻止熔融焊料流出的焊料坝的技术(专利文献2)。此外,提出了在铜板表面的焊接用区域与引线键合用区域之间形成阻止焊料流出的突条部的技术(专利文献3)。

4、另外,提出了通过热扩散板的周边的成形加工来形成薄壁部而实现施加于焊料层的应力的平衡的技术(专利文献4)。此外,提出了使接合层从金属部件的端部伸出金属部件的厚度的0.1~1.0倍而提高耐热循环性的技术(专利文献5)。此外,还提出了如下技术:在陶瓷基板的主面介由钎料层接合金属板,钎料层形成为比形成于金属板的金属电路图案的侧面更向外侧伸出(专利文献6)。

5、现有技术文献

6、专利文献

7、专利文献1:日本特开2021-118350号公报

8、专利文献2:日本特开2004-363216号公报

9、专利文献3:日本特开2000-286289号公报

10、专利文献4:日本特开平7-221265号公报

11、专利文献5:日本特开平10-190176号公报

12、专利文献6:日本特开平11-340598号公报

技术实现思路

1、技术问题

2、如果熔融的焊料向端子的接合区域外流出而焊料润湿扩展到导电板的端部,则有可能例如在进行了热循环试验的情况下等,在陶瓷电路基板产生裂纹(破裂)。这是因为陶瓷电路基板受到端子下的焊料的膨胀收缩的影响,应力集中在焊料周边的陶瓷电路基板从而产生裂纹。

3、以往,通过在陶瓷电路基板的可能产生裂纹的焊料周边的导电板的端部设置r形状,使焊料的膨胀收缩所产生的应力缓和,从而防止陶瓷电路基板产生裂纹。

4、但是,如果陶瓷电路基板的可能产生裂纹的周边部的半导体芯片搭载布局没有富余,则存在难以实施在导电板的端部设置r形状这样的对策的问题。

5、图15、图16是示出在导电板的端部设置r形状的结构的一例的图。陶瓷电路基板100在金属板(未图示)上形成有绝缘板110,在绝缘板110上形成有导电板120。端子(未图示)通过焊料130a~130d接合于导电板120。另外,焊料130b、130d被隔离槽m0包围。导电板120上的部件区域121~124是供半导体芯片搭载的区域。

6、在此,在端子下的焊料130a为熔融状态时,焊料130a有可能润湿扩展到导电板120的端部eg0。因此,考虑对陶瓷电路基板100的可能产生裂纹的可能性高的导电板120的端部eg0进行设置r形状的对策。

7、但是,如果以保持绝缘板端部至导电板端部的距离(边框尺寸)并满足绝缘基准的方式如图15所示那样在包含端部eg0在内的导电板120的整个边设置r形状sp1,则端部eg0的区域被削去。而且,导电板120上的部件区域121、122的部分也被进一步削去,难以针对部件区域121、122搭载半导体芯片。

8、另外,如图16所示,考虑在导电板120的端部eg0局部地设置r形状sp2的对策。图17的(a)示出在导电板的端部设置r形状的结构的对策之前的一例,图17的(b)示出在导电板的端部设置r形状的结构的对策之后的一例。在图17的(a)的对策之前的结构中,焊料130a到达导电板120的端部eg0。如果针对这样的结构在导电板120的端部eg0设置局部的r形状sp2,则如图17的(b)的对策后的结构所示,设置于导电板120的r形状sp2向外侧伸出。在该情况下,无法确保导电板120的r形状sp2的端部与绝缘基板110的端部之间的距离即边框尺寸sz,难以满足绝缘基准。

9、如上所述,在将导电板的边加工成r形状来缓和陶瓷电路基板的应力集中的以往的对策中,有时难以通过半导体芯片搭载布局来实施。因此,期望在不依赖于半导体芯片搭载布局的情况下有效地缓和因焊料的润湿扩展所引起的陶瓷电路基板的应力集中,从而防止陶瓷电路基板产生裂纹的技术。

10、在一个方面,本发明的目的在于提供一种半导体装置,其通过抑制焊料的润湿扩展范围来缓和陶瓷电路基板的应力集中,从而防止陶瓷电路基板产生裂纹。

11、技术方案

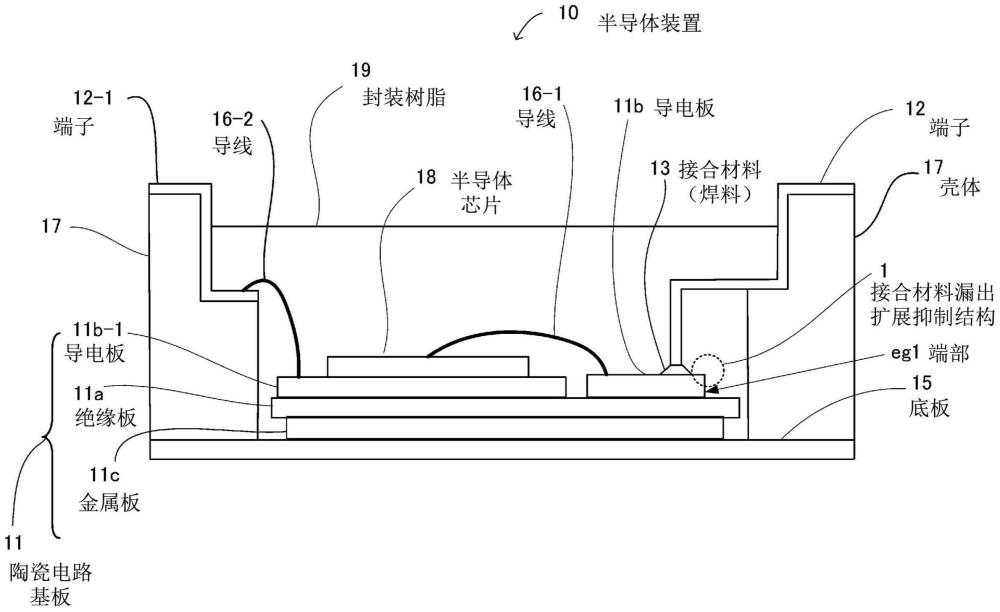

12、为了解决上述课题,提供一种半导体装置。半导体装置具备绝缘板、设置在绝缘板上的导电板、以及通过接合材料与导电板接合的端子,在导电板的端部具备抑制接合材料扩展到端部的结构。另外,该结构设置于应该使接合材料不附着的该端部的附近的预定区域。

13、另外,为了解决上述课题,提供另一半导体装置。半导体装置具备绝缘板、设置在绝缘板上的导电板、以及通过接合材料与导电板接合的端子,在导电板的端部具备抑制接合材料扩展到端部的结构。另外,作为该结构,在导电板的端部设置有导电板的厚度薄的部分,接合材料附着至导电板的厚度薄的部分的边界为止,导电板的厚度薄的部分不附着接合材料。

14、技术效果

15、根据一个方面,能够缓和陶瓷电路基板的应力集中而防止陶瓷电路基板产生裂纹。

16、通过表示作为本发明的例子而优选的实施方式的附图以及相关的下述说明,本发明的上述和其他目的、特征以及优点将变得明确。

技术特征:1.一种半导体装置,其特征在于,具备:

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求2所述的半导体装置,其特征在于,

4.根据权利要求2所述的半导体装置,其特征在于,

5.根据权利要求1所述的半导体装置,其特征在于,

6.根据权利要求5所述的半导体装置,其特征在于,

7.根据权利要求1所述的半导体装置,其特征在于,

8.根据权利要求7所述的半导体装置,其特征在于,

9.一种半导体装置,其特征在于,具备:

10.根据权利要求9所述的半导体装置,其特征在于,

11.根据权利要求9所述的半导体装置,其特征在于,

技术总结本发明通过缓和陶瓷电路基板的应力集中来防止陶瓷电路基板产生裂纹。半导体装置(10)具有陶瓷电路基板(11)、与陶瓷电路基板(11)的正面接合的端子(12、12‑1)以及半导体芯片(18)。陶瓷电路基板(11)具有绝缘板(11a)、导电板(11b、11b‑1)以及金属板(11c)。在底板(15)的表面搭载有绝缘板(11a)。在绝缘板(11a)上搭载有导电板(11b、11b‑1),在导电板(11b)上介由接合材料(13)而接合有设置于壳体(17)的端子(12)。在导电板(11b)的端部(eg1)的附近设置有用于抑制熔融的接合材料(13)的漏出扩展的接合材料漏出扩展抑制结构(1)。技术研发人员:金子悟史受保护的技术使用者:富士电机株式会社技术研发日:技术公布日:2024/7/11本文地址:https://www.jishuxx.com/zhuanli/20240716/105021.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。