SRAM物理不可克隆函数电路及设备

- 国知局

- 2024-07-31 22:39:34

本发明涉及电数字数据处理和信息安全领域,特别是涉及一种sram物理不可克隆函数电路及设备。

背景技术:

1、物理不可克隆功能 (puf) 是一种硬件安全技术,其广泛应用于芯片安全领域。由于硅基集成电路加工技术存在一定的工艺起伏,所生产的每一块集成电路在物理上都是不同的。在不同的集成电路之间,这些工艺起伏表现为相同版图区域的电路单元具备不同的路径延迟、晶体管阈值电压、电压增益等。此外,虽然这些变化在不同的集成电路之间可能是随机的,一旦集成电路被制造出来后,每块集成电路上的物理差异是确定的,由这些物理差异所导致的随机输出值同样是确定且可重复的,因此可作为每块集成电路的身份识别码。物理不可克隆技术正是利用集成电路制造过程中的这种内在差异,为每个集成电路生成一个唯一的可用于加密的随机输出值。

2、基于sram的puf技术是一种利用集成电路中的sram存储体构建puf的硬件安全技术。该技术将sram单元的上电初始值作为集成电路唯一的随机输出值。原理上,每个sram单元格具有分别表示1或0的两个稳定状态。当一个单元通电时,最终的上电状态是不可预测的。然而由于集成电路在制造过程中存在工艺起伏,单元中的晶体管之间的随机差异使每个单元都倾向于以0或1出现。对于一块sram单元来说,这会产生一个随机阵列,并且可以作为每个集成电路唯一的、不可克隆的输出值。

3、然而,现有的sram物理不可克隆函数电路存在随机输出值不稳定的技术问题。

技术实现思路

1、基于此,有必要提供一种sram物理不可克隆函数电路和一种数据处理设备。

2、为了实现上述目的,本发明实施例采用以下技术方案:

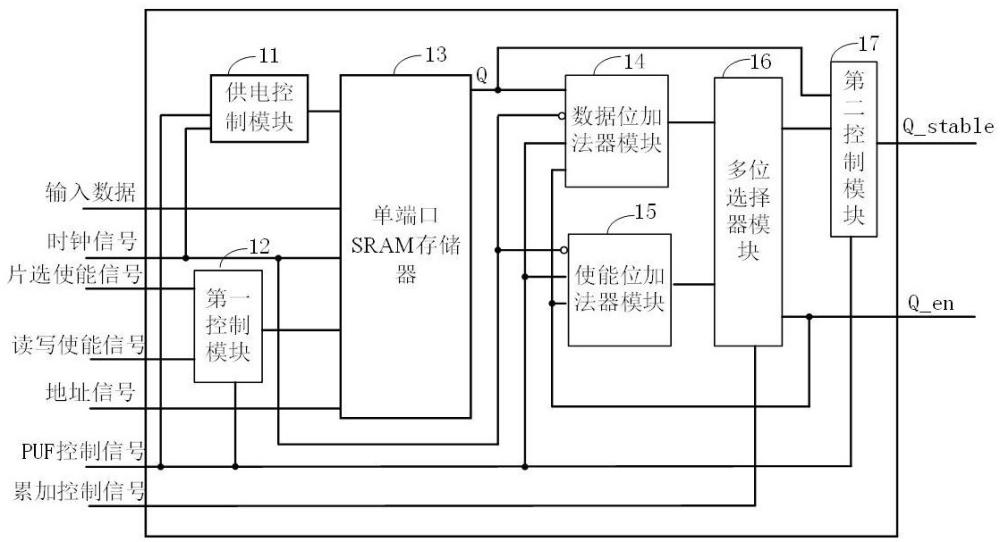

3、一方面,提供一种sram物理不可克隆函数电路,包括:供电控制模块、第一控制模块、单端口sram存储器、数据位加法器模块、使能位加法器模块、多位选择器模块和第二控制模块;

4、供电控制模块用于根据puf控制信号和时钟信号,输出供电信号,第一控制模块用于根据片选使能信号、读写使能信号和puf控制信号,输出片选信号和读写信号,单端口sram存储器用于根据输入数据、供电信号、片选信号、读写信号、时钟信号和地址信号输出特定轮各初始随机值,数据位加法器模块用于根据数据输出使能信号、时钟信号、puf控制信号,分别对每轮的各初始随机值进行累加并输出各累加随机值,使能位加法器模块用于根据数据输出使能信号、时钟信号和puf控制信号,输出累加次数信号,多位选择器模块用于根据各累加随机值、累加次数信号、累加控制信号分别输出物理不可克隆随机值和数据输出使能信号,第二控制模块用于根据puf控制信号选择输出各初始随机值或物理不可克隆随机值。

5、另一方面,还提供一种数据处理设备,数据处理设备上设置有上述的sram物理不可克隆函数电路。

6、本申请实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

7、上述sram物理不可克隆函数电路及设备,在puf控制信号无效时,sram物理不可克隆函数电路为一个常规的sram存储器,增加了电路的普适性和灵活性。在puf控制信号有效时,通过供电控制模块使单端口sram存储器能够自动化的进行多轮上/断电操作,数据位加法器模块对单端口sram存储器的输出值进行累加,使能位加法器模块产生累加次数信号,多位选择器模块根据累加次数信号、单端口sram存储器的输出及使能位加法器模块的输出物理不可克隆随机值。当puf控制信号有效后可以完成多次“随机值输出-随机值累加-sram断电-sram上电”操作,根据多次操作的计算形成最终的随机输出值,自动化的多次累加sram 物理不可克隆函数电路的随机输出值,抑制了噪声对sram 物理不可克隆函数电路的影响,大大提高了随机输出数据的稳定性。

技术特征:1.一种sram物理不可克隆函数电路,其特征在于,包括供电控制模块、第一控制模块、单端口sram存储器、数据位加法器模块、使能位加法器模块、多位选择器模块和第二控制模块;

2.根据权利要求1所述的sram物理不可克隆函数电路,其特征在于,所述供电控制模块包括与门单元、第一延时单元、第二延时单元、非门单元和触发器;

3.根据权利要求1所述的sram物理不可克隆函数电路,其特征在于,所述第一控制模块包括第一二选一单元和第二二选一单元;

4.根据权利要求3所述的sram物理不可克隆函数电路,其特征在于,所述数据位加法器模块包括m个二选一单元和m个数据位加法器;m等于所述单端口sram存储器的位宽;

5.根据权利要求4所述的sram物理不可克隆函数电路,其特征在于,所述使能位加法器模块包括一个二选一单元和一个使能位加法器;

6.根据权利要求5所述的sram物理不可克隆函数电路,其特征在于,所述多位选择器模块包括(m+1)个多选一单元;

7.根据权利要求6所述的sram物理不可克隆函数电路,其特征在于,所述第二控制模块包括m个二选一单元;

8.一种数据处理设备,其特征在于,包括根据权利要求1-7中任一项所述的sram物理不可克隆函数电路。

9.根据权利要求8所述的数据处理设备,其特征在于,所述数据处理设备为安全芯片。

10.根据权利要求8所述的数据处理设备,其特征在于,所述数据处理设备为身份验证设备。

技术总结本申请涉及一种SRAM物理不可克隆函数电路及设备。包括供电控制模块、第一控制模块、单端口SRAM存储器、数据位加法器模块、使能位加法器模块、多位选择器模块和第二控制模块。在PUF控制信号有效时,通过供电控制模块使单端口SRAM存储器能够自动化的进行多轮上/断电操作,数据位加法器模块对单端口SRAM存储器的输出值进行累加,使能位加法器模块产生累加次数信号,多位选择器模块根据累加次数信号、单端口SRAM存储器的输出及使能位加法器模块的输出物理不可克隆随机值。自动化的多次累加SRAM物理不可克隆函数电路的随机输出值,大大提高了随机输出数据的稳定性。技术研发人员:王耀华,邵津津,宋睿强,郭阳,李少青,陈吉华,王俊辉,张洋受保护的技术使用者:中国人民解放军国防科技大学技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240730/194043.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表