灵敏放大器电路的制作方法

- 国知局

- 2024-07-31 19:17:52

本发明涉及一种半导体集成电路,特别是涉及一种灵敏放大器电路(senseamplifier,sa)电路。

背景技术:

1、如图1所示,是现有灵敏放大器电路的电路图;现有灵敏放大器电路包括:连接在位线节点a和数据线节点c之间的位线调整单元101。

2、所述位线调整单元101包括第一nmos管mn101。

3、所述第一nmos管mn101的漏极连接所述数据线节点c,所述第一nmos管mn101的源极连接所述位线节点a。

4、所述第一nmos管mn101的栅极和所述位线节点a之间具有反馈电路,所述反馈电路由反相器103组成。所述反相器103为cmos反相器,包括nmos管mn102和pmos管mp101,所述nmos管mn102作为下拉管,所述pmos管mp101作为上拉管。

5、反相器103的输入端连接所述位线节点a,所述反相器103的输出端作为反馈节点b连接到所述第一nmos管mn101的栅极。

6、所述反馈节点b的电压为所述位线节点a的反相信号。节点a的电压较小时,节点b的电压较大;节点a的电压较大时,节点b的电压较小。但是节点b的高低电平转换不是突变的,而是有一个翻转区域,翻转区域位于钳位电压vclamp附近。当节点a的电压大于电压vclamp时,节点b的电压会翻转到低电平;而节点a的电压小于vclamp时则节点b的电压会翻转到高电平。图1中,在预充电后,节点a的电压会钳位在钳位电压vclamp。所述第一nmos管mn101也称为钳位(clamp)晶体管(transistor)。

7、在读取时,所述位线节点a连接到选定的存储单元(cell)104,所述位线节点a的电压由所述存储单元104的存储状态确定,

8、在所述数据线节点c和电源电压vdd之间连接有电流源iref,所述电流源iref的电流作为和所述存储单元104的单元电流比较的参考电流;读取时,通过比较所述电流源iref的电流和所述单元电流在所述数据线节点c形成第一输出电压。

9、所述灵敏放大器电路还包括输出单元102;所述第一输出电压输入到所述输出单元102的输入端并在所述输出单元102的输出端输出第二输出信号soutb。图1中,所述输出单元102包括比较器。

10、所述第一输出电压连接到所述比较器的第一输入端即+端。

11、所述比较器的第二输入端即-端连接参考电压vref。

12、所述比较器的输出端输出所述第二输出信号soutb。

13、多个所述存储单元104组成存储阵列。在所述第一nmos管mn101的源极和所述位线节点a之间还连接有译码电路105;读取时,通过所述译码电路105选择对应的所述存储单元104的列,通过字线电压vwl选择对应的所述存储单元104的行,从而实现所述存储单元104的选定。译码电路105由多个开关加译码信号组成,图1中仅显示了一个nmos管mn103以及两个译码信号ya和yb。

14、所述存储单元104为非挥发性存储单元,所述非挥发性存储单元的栅极结构中包括浮栅;所述非挥发性存储单元的存储状态包括擦除状态和编程状态。

15、所述非挥发性存储单元为n型器件时,包括n+掺杂的源区和漏区,所述编程状态下,所述浮栅中存储有电子;所述擦除状态下,所述浮栅中存储的电子被去除。

16、在编程状态下所述非挥发性存储单元具有第一阈值电压,所述单元电流为读‘0’单元电流。

17、在擦除状态下所述非挥发性存储单元具有第二阈值电压,所述单元电流为读‘1’单元电流。

18、所述第一阈值电压大于所述第二阈值电压,所述读‘0’单元电流小于所述读‘1’单元电流。所述单元电流越大,所述位线节点a的电压越低。

19、具有编程状态的所述存储单元104所存储的信息为‘0’,读‘0’时,所述单元电流为读‘0’单元电流,所述位线节点a的电压较高;经过所述反相器103反相后得到的所述反馈节点b的电压会较低,这样所述第一nmos管mn101会关闭。如图2所示,是图1所示的现有灵敏放大器电路中的反馈节点和数据线节点的电压在电源电压产生波动时的波形曲线;但是,由于所述反馈节点b直接通过所述反相器103的上拉管即pmos管mp101连接电源电压vdd。当电源电压vdd具有波动时,如产生较大的上冲(overshoot)时,pmos管mp101会导通,从而使所述反馈节点b的电压也跟随所述电源电压vdd上冲,从而会所述第一nmos管mn101的电流会增加,所述数据线节点c的电压下降。图2中,曲线vdd表示所述电源电压vdd的波形曲线,曲线vb表示所述反馈节点b的电压的波形曲线,曲线vc表示所述数据线节点c的电压的波形曲线,虚线vref表示所述参考电压vref的曲线。可以看出,当曲线vc下降到虚线vref之下时,表示所述数据线节点c的电压即所述第一输出电压会低于所述参考电压vref,经过所述输出单元102的比较器的比较之后,所述第二输出信号soutb产生翻转,导致读‘0’失败(fail)。所以,图1所示的现有灵敏放大器电路中,vdd的电压波动如噪声会传递到节点b的电压中,节点b的电压中的波动又会传递到节点c的电压中,严重时会导致数据误翻,从而发生读取失败。

技术实现思路

1、本发明是提供一种灵敏放大器电路,能降低读取过程中的电源电压波动的影响,从而增强抗干扰能力。

2、本发明提供的灵敏放大器电路包括:第一灵敏放大主体电路、参考电压产生电路和比较器。

3、所述第一灵敏放大主体电路和存储阵列中的选定存储单元连接并形成对所述选定存储单元的读取路径,所述第一灵敏放大主体电路的输出端输出第一输出电压,电源电压的波动会使所述第一输出电压产生波动。

4、所述参考电压产生电路包括第二灵敏放大模拟电路、第二存储单元和源极跟随器;所述第二存储单元和所述存储阵列中的各存储单元的结构相同,所述第二存储单元为编程状态,所述第二灵敏放大模拟电路采用和所述第一灵敏放大主体电路相同的结构,所述第二灵敏放大模拟电路和所述第二存储单元相连接并形成读‘0’路径,所述第二灵敏放大模拟电路的输出端输出模拟输出电压,所述电源电压的波动也会使所述模拟输出电压产生波动。

5、所述模拟输出电压连接到所述源极跟随器的栅极,所述源极跟随器的源极和地之间连接分压电路,所述分压电路输出所述参考电压,所述参考电压为所述源极跟随器的源极的分压,所述参考电压跟随所述模拟输出电压变化且所述参考电压小于所述模拟输出电压。

6、所述比较器的第一输入端连接所述第一输出电压。

7、所述比较器的第二输入端连接所述参考电压。

8、所述比较器的输出端输出第二输出信号。

9、在所述选定存储单元为编程状态且所述电源电压具有波动时,所述模拟输出电压随所述电源电压变化的波形等同于所述第一输出电压随所述电源电压变化的波形,使得所述参考电压保持为小于所述第一输出电压并从而使所述第二输出信号保持不变。

10、进一步的改进是,所述第一灵敏放大主体电路包括:第一电流源、第一位线调整单元和第一反相器。

11、所述第一位线调整单元包括第一nmos管,所述第一nmos管的漏极连接第一数据线节点,所述第一nmos管的源极连接第一位线节点。

12、所述第一反相器的输入端连接所述第一位线节点,所述第一反相器的输出端连接到所述第一nmos管的栅极,所述第一nmos管的栅极为第一反馈节点。

13、读取时,所述第一位线节点和所述选定存储单元连接。

14、所述第一电流源连接在所述第一数据线节点和所述电源电压之间,所述第一电流源的电流作为和所述选定存储单元的第一单元电流比较的第一参考电流;读取时,通过比较所述第一参考电流和所述第一单元电流在所述第一数据线节点形成所述第一输出电压。

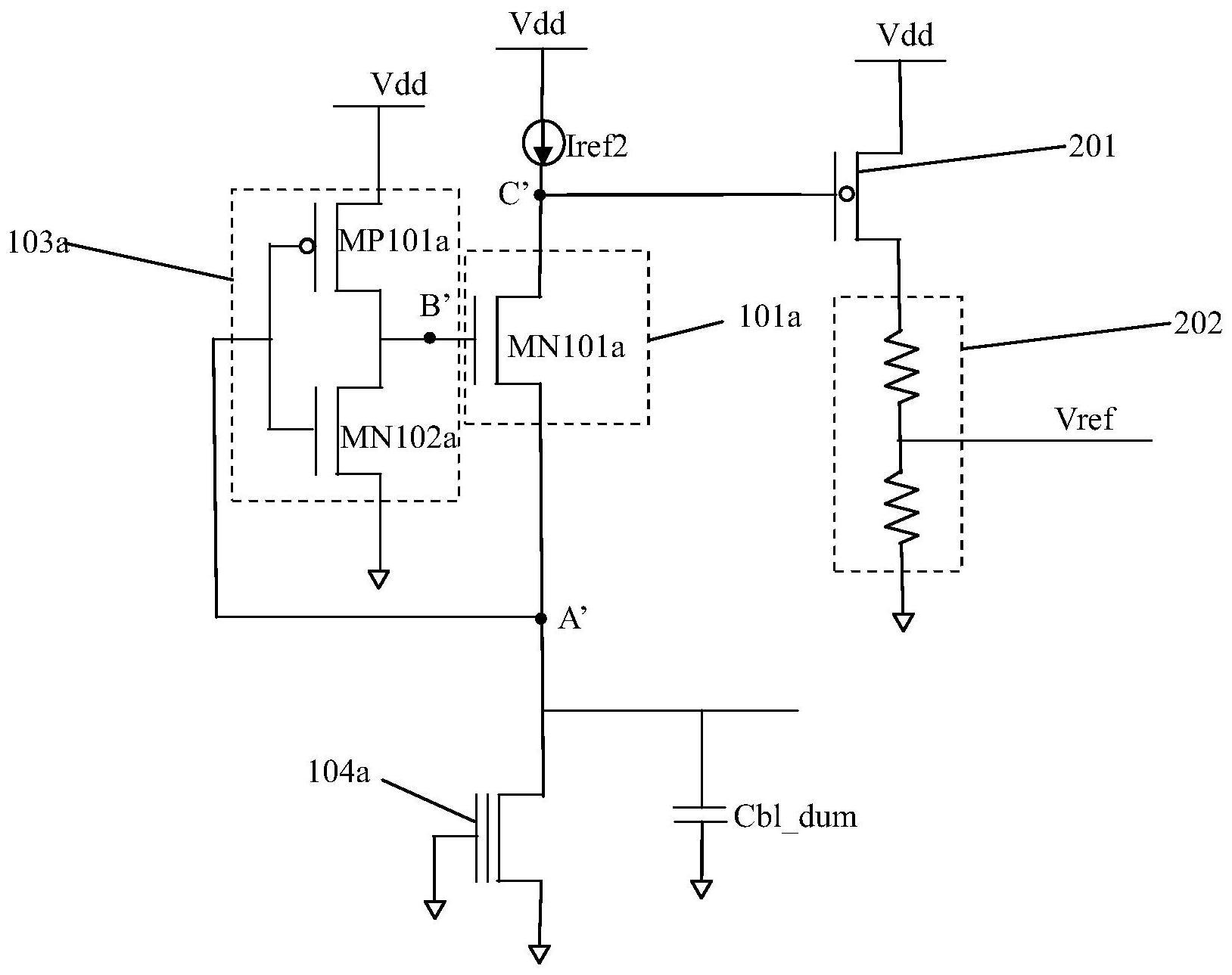

15、进一步的改进是,所述第二灵敏放大模拟电路包括第二电流源、第二位线调整单元和第二反相器。

16、所述第二位线调整单元包括第二nmos管,所述第二nmos管的漏极连接第二数据线节点,所述第二nmos管的源极连接第二位线节点。

17、所述第二反相器的输入端连接所述第二位线节点,所述第二反相器的输出端连接到所述第二nmos管的栅极,所述第二nmos管的栅极为第二反馈节点。

18、所述第二位线节点和所述第二存储单元连接。

19、所述第二电流源连接在所述第二数据线节点和所述电源电压之间,所述第二电流源的电流作为和所述第二存储单元的第二单元电流比较的第二参考电流,所述第二参考电流和所述第二单元电流相比较并在所述第二数据线节点形成所述模拟输出电压。

20、进一步的改进是,所述第一反相器采用第一cmos反相器。

21、读取时,当所述选定存储单元为编程状态时,在所述第一灵敏放大主体电路中,所述电源电压的波动通过所述第一反相器的上拉管传递到所述第一反馈节点并形成所述第一反馈节点的电压波动,所述第一反馈节点的电压波动通过所述第一nmos管传递给所述第一输出电压并形成所述第一输出电压的的电压波动。

22、进一步的改进是,所述第二反相器采用第二cmos反相器。

23、在所述第二灵敏放大模拟电路中,所述电源电压的波动通过所述第二反相器的上拉管传递到所述第二反馈节点并形成所述第二反馈节点的电压波动,所述第二反馈节点的电压波动通过所述第二nmos管传递给所述模拟输出电压并形成所述模拟输出电压的的电压波动。

24、进一步的改进是,所述参考电压产生电路中还设置有第一电容,所述第一电容连接在所述第二位线节点和地之间;所述第一电容的大小等于对所述选定存储单元进行读取时所述选定存储单元所连接的位线形成的位线寄生电容。

25、进一步的改进是,所述存储单元为非挥发性存储单元。

26、进一步的改进是,在所述第一nmos管的源极和所述位线节点之间还连接有译码电路;读取时,通过所述译码电路在所述存储阵列中选择对应的所述存储单元作为所述选定存储单元。

27、进一步的改进是,所述非挥发性存储单元的栅极结构中包括浮栅;所述非挥发性存储单元的存储状态包括擦除状态和编程状态。

28、所述非挥发性存储单元在编程状态下具有第一阈值电压以及在擦除状态下所述非挥发性存储单元具有第二阈值电压;所述第一阈值电压大于所述第二阈值电压。

29、进一步的改进是,所述非挥发性存储单元为n型器件,包括n+掺杂的源区和漏区,所述编程状态下,所述浮栅中存储有电子;所述擦除状态下,所述浮栅中存储的电子被去除。

30、进一步的改进是,所述电源电压的波动包括由噪声产生的波动。

31、进一步的改进是,所述分压电路由电阻串组成。

32、进一步的改进是,所述源极跟随器采用原生nmos管。

33、和现有技术中参考电压产生电路形成的参考电压具有不随电源电压变化的固定值不同,本发明对参考电压产生电路做了特别的设置,采用了结构和第一灵敏放大主体电路相同的第二灵敏放大模拟电路,通过第二灵敏放大模拟电路对处于编程状态即‘0’状态的第二存储单元进行读取形成模拟输出电压,参考电压则是通过源极跟随器对模拟输出电压进行跟随并进行分压后得到,这样就能保证参考电压会跟随模拟输出电压的变化且小于模拟输出电压;而由于第一灵敏放大主体电路和第二灵敏放大模拟电路,故通过第一灵敏放大主体电路对存储阵列中状态为编程状态的选定存储单元进行读取输出的第一输出电压和模拟输出电压随电源电压变化的波形相同,这样,即使电源电压变化使得第一输出电压变化时,也能保证第一输出电压大于参考电压,故能保证第二输出信号的不变,也即能保证读取结果不变,故能降低读取过程中的电源电压波动的影响,从而增强抗干扰能力。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182240.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表