内存模组和电子设备的制作方法

- 国知局

- 2024-07-31 19:28:12

本技术涉及计算机,特别涉及一种内存模组和电子设备。

背景技术:

1、内存又称主存,是现代计算机系统中的核心部件之一。目前内存在硬件系统中的典型形态是包括多个内存芯片的内存模组(又称为内存条),例如包括多个动态随机存储器(dynamic random access memory,dram)颗粒的内存模组。由于dram颗粒在使用过程中会因为电路故障、存储单元故障等导致数据错误,为确保数据完整性,在对数据稳定性要求较高的场景中,例如服务器、云存储等应用场景中,会使用错误检查和纠正(error checkingand correcting,ecc)内存模组。ecc内存模组通过增加冗余的dram颗粒来存储纠错码,例如,参考图1,采用第四代双倍数据率同步动态随机存取存储器(double-data-rate fourthgeneration synchronous dynamic random access memory,ddr4)规范的ecc内存模组在和处理器进行数据交换时,一个采样周期交换72位数据,其中,64位为数据,8位为纠错码。处理器在访问ecc内存模组中的数据时,可以通过该纠错码来确定访问的数据是否有错误,并在确定出访问的数据有错误的情况下,通过ecc算法来纠正错误。

2、目前,处理器对应的可纠正错误的数据位宽通常为4位,即是在处理器单次对ecc内存模组的数据访问过程中,在出现错误的数据位数不超过4位的情况下,可以通过处理器或存储器控制器进行纠正。在采用数据位宽为4位的dram颗粒的内存模组中,由于dram颗粒的数据位与处理器的数据位是一一对应关系,若一个dram颗粒发生故障,则只会有4位数据可能发生错误,处理器可以通过ecc算法对该dram颗粒的数据错误进行纠正。

3、为满足用户对计算机的内存性能的需求,例如提高内存容量、访问速度等,ecc内存模组中可以采用数据位宽更大的dram颗粒。但是,在ecc内存模组采用的dram颗粒的数据位宽超过4位时,例如dram颗粒的位宽为8位或16位时,由于dram颗粒的数据位与处理器的数据位是一一对应关系,单个dram颗粒故障时会导致出现错误的数据位数超过4位,从而导致处理器无法进行纠错,进而使得采用数据位宽为8位或16位的dram颗粒的ecc内存模组的稳定性,低于采用数据位宽为4位的dram颗粒的ecc内存模组,限制了采用数据位宽为8位或16位的dram颗粒的ecc内存模组在对数据稳定性要求较高的场景中的应用。

技术实现思路

1、有鉴于此,本技术提供了一种内存模组和电子设备,有利于提高内存模组的稳定性。

2、第一方面,本技术实施例提供了一种内存模组,该内存模组的rank位宽为4n,并且内存模组包括:存储模块,存储模块包括至少一个rank,每个rank包括n个内存颗粒,其中,16个内存颗粒用于存储数据,n-16个内存颗粒用于存储纠错码;控制电路,用于根据接收到的第一读取指令从每个内存颗粒中读取(2n-32)×8位数据并且每个采样周期输出4n位数据,或者根据接收到的第一存储指令向每个内存颗粒中存储(2n-32)×8位数据,其中,每个采样周期输出的4n位数据中至多有4位是从同一个内存颗粒中读取。

3、也即是说,在本技术实施例中,通过增加一个rank中的内存颗粒(例如dram颗粒)的数量来减少每次访问过程中处理器从单个内存颗粒访问的数据的位数。内存模组的一个rank中内存颗粒的位宽总和为内存模组的rank位宽的两倍,对于采用ddr4规范的内存模组,rank位宽为72(即n=18),从而处理器在通过bl8访问指令(第一存储指令或第一读取指令)访问一个rank时,从一个内存颗粒只读取32位数据,并且每个采样周期向处理器发送的数据中,只有4位是来自于同一个内存颗粒,进而在一个内存颗粒故障时,每个采样周期的数据至多只有4位出错,未超出处理器的纠错能力,提高了内存模组的稳定性。

4、类似地,对于采用ddr5规范的内存模组,rank位宽为80(即n=20),从而处理器在通过bl16访问指令(第一存储指令或第一读取指令)访问一个rank时,从一个内存颗粒只读取64位数据,并且每个采样周期向处理器发送的数据中,只有4位是来自于同一个内存颗粒,进而在一个内存颗粒故障时,每个采样周期的数据至多只有4位出错,未超出处理器的纠错能力,提高了内存模组的稳定性。

5、在上述第一方面的一种可能实现中,n=18或20,并且各内存颗粒的颗粒位宽为8位。

6、对于采用ddr4规范的内存模组,rank位宽为72,n=18;对于采用ddr5规范的内存模组,rank位宽为80,n=20。

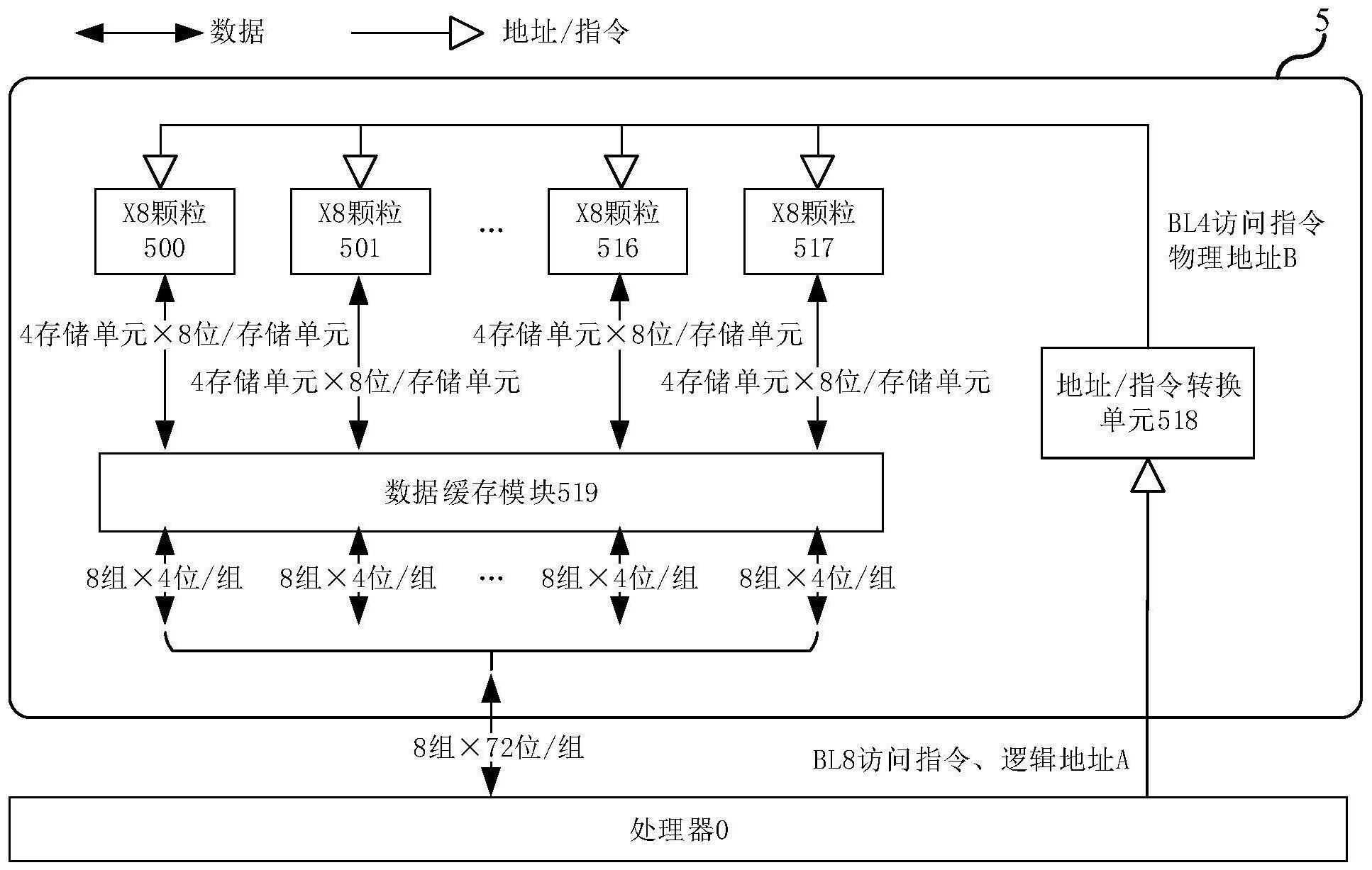

7、在上述第一方面的一种可能实现中,上述控制电路包括指令/地址转换模块和数据缓存模块;并且,控制电路通过以下方式根据接收到的第一存储指令向每个内存颗粒中存储(2n-32)×8位数据:指令/地址转换模块将第一存储指令转换为第二存储指令,第二存储指令用于向每个内存颗粒中的2n-32个存储单元中写入数据;数据缓存模块将接收到的(2n-32)×8n位数据分为数据位数相同的n个数据组,并向每个内存颗粒发送一个数据组的数据;存储模块响应第二存储指令,将接收到的各数据组的数据存储在相对应的内存颗粒中的2n-32个存储单元中。

8、在本技术实施例中,增加了一个rank中的内存颗粒的数量,对于采用ddr4规范的内存模组,可以将bl8访问指令转换为bl4访问指令来从一个内存颗粒访问32位数据;而对于采用ddr5规范的内存模组,可以将bl16访问指令转换为bl8访问指令来从一个内存颗粒访问64位数据。

9、在上述第一方面的一种可能实现中,上述控制电路通过以下方式根据接收到的第一读取指令从每个内存颗粒中读取(2n-32)×8位数据并且每个采样周期输出4n位数据:指令/地址转换模块将第一读取指令转换为第二读取指令,第二读取指令用于读取每个内存颗粒的2n-32个存储单元中数据;存储模块响应第二读取指令,将每个内存颗粒中的2n-32个存储单元中的数据发送给数据缓存模块;数据缓存模块每个采样周期将从存储模块接收的数据中选择4n位数据输出。

10、在上述第一方面的一种可能实现中,在n=18的情况下,第一读取指令或第一存储指令为bl8访问指令,第二读取指令或第二存储指令为bl4访问指令;在n=20的情况下,第一读取指令或第一存储指令为bl16访问指令,第二读取指令或第二存储指令为bl8访问指令。

11、在上述第一方面的一种可能实现中,上述每个内存颗粒包括至少一个记忆体晶片(bank),每个记忆体晶片的行数为p1、列数为q1,第一存储指令包括第一逻辑地址,第一逻辑地址包括第一行标识r1和第一列标识c1,r1的取值范围为0至2p1-1,第二存储指令中包括第一物理地址;并且,指令/地址转换模块将第一存储指令转换为第二存储指令,包括:指令/地址转换模块在r1<p1的情况下,将第一物理地址的行标识设置r1、列标识设置为c1/2,并且,2n-32个存储单元包括第一物理地址指示的存储单元所在的行中,列标识为c1/2至c1/2+2n-33的存储单元;指令/地址转换模块在r1≥p1的情况下,将第一物理地址的行标识设置为r1-p1、列标识设置为c1/2+q1/2,并且,2n-32个存储单元包括第一物理地址指示的存储单元所在的行中,列标识为c1/2+q1/2至c1/2+q1/2+2n-33的存储单元。

12、在本技术实施例中,处理器访问内存模组的逻辑地址(第一逻辑地址)中,行标识的取值范围为内存颗粒的每个bank行数p1据的两倍,从而内存模组可以在逻辑地址中的行标识r1≥p1时,访问每个bank的后一半的列。

13、在上述第一方面的一种可能实现中,上述第一读取指令包括第二逻辑地址,第二逻辑地址包括第二行标识r2和第二列标识c2,r2取值范围为0至2p1-1,第二读取指令中包括第二物理地址;并且,指令/地址转换模块将第一读取指令转换为第二读取指令,包括:指令/地址转换模块在r2<p1的情况下,将第二物理地址的行标识设置为r2、列标识设置为c2/2,并且,2n-32个存储单元包括第二物理地址指示的存储单元所在的行中,列标识为c2/2至c2/2+2n-33的存储单元;指令/地址转换模块在r2≥p1的情况下,将第二物理地址的行标识设置为r2-p1、列标识设置为c2/2+q1/2,并且,2n-32个存储单元包括第二物理地址指示的存储单元所在的行中,列标识为c2/2+q1/2至c2/2+q1/2+2n-33的存储单元。

14、在上述第一方面的一种可能实现中,上述内存颗粒为以下内存颗粒中的任意一种:dram颗粒、rram颗粒、mram颗粒、pcram颗粒。

15、第二方面,本技术实施例提供了一种内存模组,该内存模组的rank位宽为8x,并且内存模组包括:存储模块,存储模块包括至少一个rank,每个rank包括x个内存颗粒,每个内存颗粒包括多个记忆体晶片(bank),其中,8个内存颗粒用于存储数据,x-8个内存颗粒用于存储纠错码;控制电路,用于根据接收到的第三读取指令从每个内存颗粒的第一bank和第二bank各读取(4x-32)×8位数据并且每个采样周期输出8x位数据,或者根据接收到的第三存储指令向每个内存颗粒的第三bank或第四bank各存储(4x-32)×8位数据,其中,每个采样周期输出的8x位数据中至多有4位是从同一个内存颗粒的同一个bank中读取。

16、也即是说,在本技术实施例中,通过将对一个内存颗粒(例如dram颗粒)同一bank的访问转换为对该内存颗粒的两个bank的访问,来减少一次访问过程中从一个bank中访问的数据的位数。

17、对于采用ddr4规范的内存模组,rank位宽为72(即x=9),从而处理器在通过bl8指令访问一个rank时,从该rank中的每一个内存颗粒的两个bank中各读32位数据,并且每个采样周期向处理器发送的数据中,只有4位是来自于同一个内存颗粒的同一个bank,进而在一个bank发生故障时,每个采样周期的数据至多只有4位出错,未超出处理器的纠错能力,由于内存颗粒中两个bank同时发生故障的概率较低,可以提高内存模组的稳定性。

18、类似地,对于采用ddr4规范的内存模组,rank位宽为80(即x=10),从而处理器在通过bl16指令访问一个rank时,从该rank中的每一个内存颗粒的两个bank中各读64位数据,并且每个采样周期向处理器发送的数据中,只有4位是来自于同一个内存颗粒的同一个bank,进而在一个bank发生故障时,每个采样周期的数据至多只有4位出错,未超出处理器的纠错能力,由于内存颗粒中两个bank同时发生故障的概率较低,可以提高内存模组的稳定性。

19、在上述第二方面的一种可能实现中,x=9或10,并且各内存颗粒的颗粒位宽为8位。

20、对于采用ddr4规范的内存模组,rank位宽为72,x=8;对于采用ddr5规范的内存模组,rank位宽为80,x=10。

21、在上述第二方面的一种可能实现中,上述控制电路包括指令/地址转换模块和数据缓存模块;并且,控制电路通过以下方式根据接收到的第三存储指令向每个内存颗粒的第三bank或第四bank各存储(4x-32)×8位数据:指令/地址转换模块将第三存储指令转换为第四存储指令和第五存储指令,第四存储指令用于向每个内存颗粒中第一bank的4x-32个存储单元中写入数据、第五存储指令用于向每个内存颗粒中第二bank的4x-32个存储单元中写入数据;数据缓存模块将接收到的(4x-32)×16x位数据分为数据位数相同的x个数据组,并向每个内存颗粒发送一个数据组的数据;存储模块响应第四存储指令和第五存储指令,将接收到的各数据组中的(4x-32)×8位数存储到对应的内存颗粒的第一bank中的4x-32个存储单元中,将另外(4x-32)×8位数存储到第二bank中的4x-32个存储单元中。

22、在上述第二方面的一种可能实现中,上述控制电路通过以下方式根据接收到的第三读取指令从每个内存颗粒的第一bank和第二bank各读取(4x-32)×8位数据并且每个采样周期输出8x位数据:指令/地址转换模块将第三读取指令转换为第四读取指令和第五读取指令,第四读取指令用于从每个内存颗粒中第一bank的4x-32个存储单元中读取数据、第五读取指令用于从每个内存颗粒中第二bank的4x-32个存储单元中读取数据;存储模块响应第四读取指令,从各内存颗粒的第一bank中的4x-32个存储单元中读取数据并发并给数据缓存模块,以及响应第五读取指令,从各内存颗粒的第二bank中的4x-32个存储单元中读取数据并发并给数据缓存模块;数据缓存模块每个采样周期将从存储模块接收的数据中选择8x位数据输出。

23、在上述第二方面的一种可能实现中,在x=9的情况下,第三读取指令和第三存储指令为bl8访问指令,第四读取指令、第五读取指令、第四存储指令和第五存储指令为bl4访问指令;在x=10的情况下,第三读取指令或第三存储指令为bl16访问指令,第四读取指令、第五读取指令、第四存储指令和第五存储指令为bl8访问指令。

24、在上述第二方面的一种可能实现中,每个内存颗粒中每个记忆体晶片的行数为p2、列数为q2、bank数为t,第三存储指令包括第三逻辑地址,第三逻辑地址包括第三行标识r3、第三列标识c3和第一bank标识b1,b1的取值范围为0至t-1,第四存储指令中包括第三物理地址、第五存储指令中包括第四物理地址;并且,指令/地址转换模块将第三存储指令转换为第四存储指令和第五存储指令,包括:指令/地址转换模块在b1<t/2的情况下,将第一bank的bank标识设置为b1、将第二bank的bank标识设置为b1+t/2、将第三物理地址和第四物理地址的行标识设置为r3,列标识设置为c3/2,并且,第一bank的4x-32个存储单元包括第三物理地址指示的存储单元所在的行中,列标识为c3/2至c3/2+4x-33的存储单元,第二bank的13-x个存储单元包括第四物理地址指示的存储单元所在的行中,列标识为c3/2至c3/2+4x-33的存储单元;指令/地址转换模块在b1>t/2的情况下,将第一bank的bank标识设置为b1、将第二bank的bank标识设置为b1-t/2、将第三物理地址和第四物理地址的行标识设置为r3,列标识设置为c3/2+q2/2,并且,第一bank的4x-32个存储单元包括第三物理地址指示的存储单元所在的行中,列标识为c3/2+q2/2至c3/2+q2/2+4x-33的存储单元,第二bank的4x-32个存储单元包括第四物理地址指示的存储单元所在的行中,列标识为c3/2+q2/2至c3/2+q2/2+4x-33的存储单元。

25、在上述第二方面的一种可能实现中,上述第三读取指令包括第四逻辑地址,第四逻辑地址包括第四行标识r4、第四列标识c4和第二bank标识b2,b2的取值范围为0至t-1,第四读取指令中包括第五物理地址、第五读取指令中包括第六物理地址;并且,指令/地址转换模块将第三存储指令转换为第四存储指令和第五存储指令,包括:指令/地址转换模块在b2<t/2的情况下,将第一bank的bank标识设置为b2、将第二bank的bank标识设置为b2+t/2、将第五物理地址和第六物理地址的行标识设置为r4、列标识设置为c4/2,并且,第一bank的4x-32个存储单元包括第五物理地址指示的存储单元所在的行中,列标识为c4/2至c4/2+4x-33的存储单元,第二bank的4x-32个存储单元包括第六物理地址指示的存储单元所在的行中,列标识为c4/2至c4/2+4x-33的存储单元;指令/地址转换模块在b2>t/2的情况下,将第一bank的bank标识设置为b2、将第二bank的bank标识设置为b2-t/2、将第五物理地址和第六物理地址的行标识设置为r4,列标识设置为c4/2+q2/2,并且,第一bank的4x-32个存储单元包括第五物理地址指示的存储单元所在的行中,列标识为c4/2+q2/2至c4/2+q2/2+4x-33的存储单元,第二bank的4x-32个存储单元包括第六物理地址指示的存储单元所在的行中,列标识为c4/2+q2/2至c4/2+q2/2+4x-33的存储单元。

26、在上述第二方面的一种可能实现中,上述内存颗粒为以下内存颗粒中的任意一种:dram颗粒、rram颗粒、mram颗粒、pcram颗粒。

27、第三方面,本技术实施例提供了一种电子设备,该电子设备包括至少一个上述第一方面、上述第一方面的各种可能实现、上述第二方面及上述第二方面的各种可能实现提供的任意一种内存模组。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182623.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表