一种采用BGA96封装的多存储信号复用式SMCP芯片的制作方法

- 国知局

- 2024-07-31 19:28:00

本发明涉及芯片,特别涉及一种采用bga96封装的多存储信号复用式smcp芯片。

背景技术:

1、为了适应设备小型化的需要,现有的一些存储芯片采用nor+psram的mcp(multi-chip package)结构形式,用nor flash(非易失闪存)存储代码和数据,psram(伪静态随机存储器)存储mcu和dsp运算的缓存数据,但该结构形式苦于无法直接利用现有电路板的bga96球设计,以致无法大力推动量产。本发明提出一种可以向上兼容bga96球设计的smcp芯片。

技术实现思路

1、本发明的主要目的是提出一种采用bga96封装的多存储信号复用式smcp芯片,旨在减少引脚数量、实现芯片的合二为一。

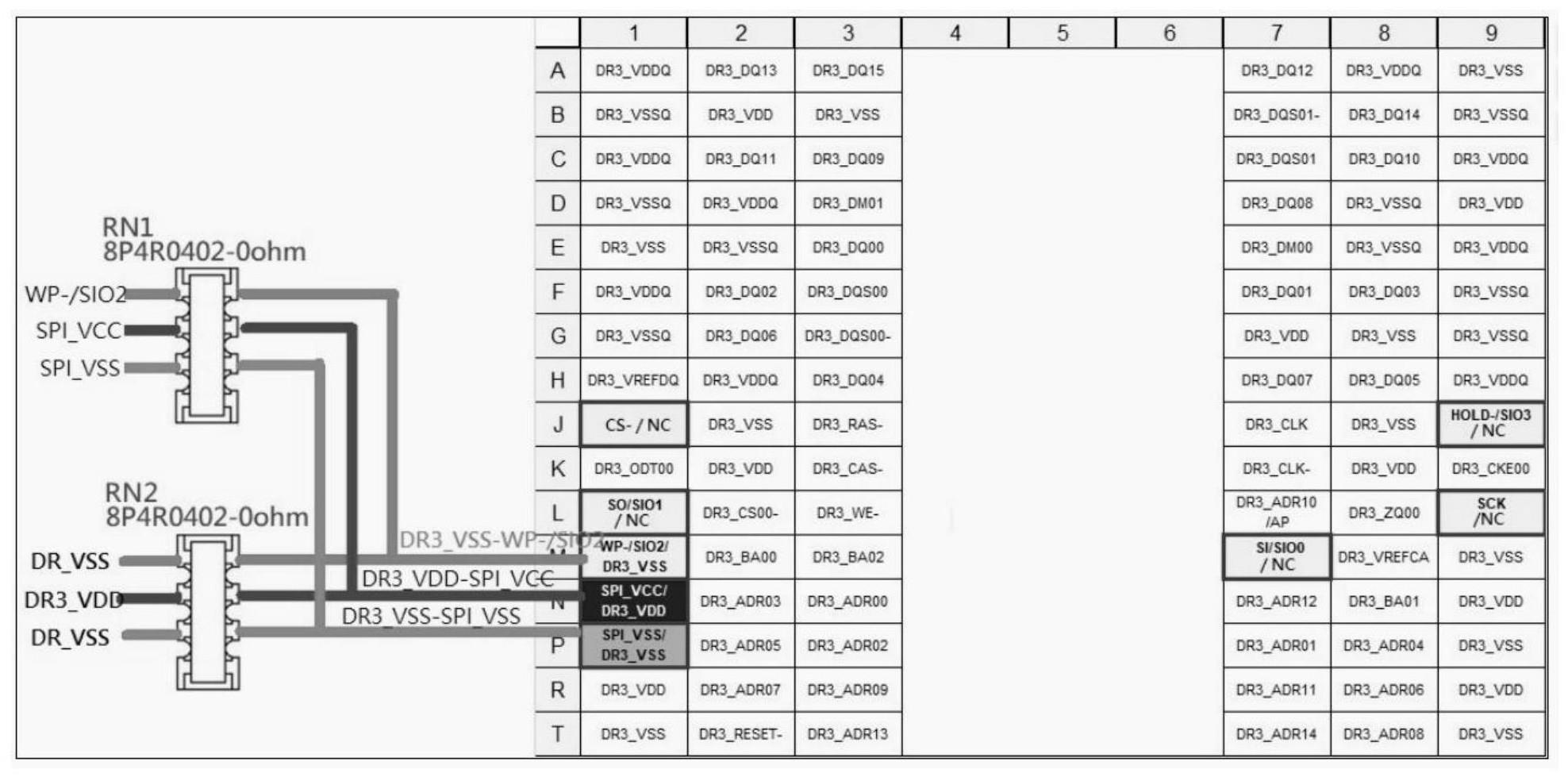

2、一种采用bga96封装的多存储信号复用式smcp芯片,其特征在于,包括:96球设计的pcb基板、设于所述pcb基板上的ddr3sdram、spi nand flash、第一电阻阵列及第二电阻阵列,所述spi nand flash借助所述第一电阻阵列和第二电阻阵列与ddr3sdram建立引脚共用,以完成封装。

3、可选地,所述spi nand flash和所述ddr3sdram垂直堆叠封装;

4、可选地,所述ddr3sdram与spi nand flash共用的引脚包括j1、j9、l1、l9、m1、m7、n1、p1;

5、可选地,所述ddr3sdram位于j1引脚为nc,与所述spi nand flash位于j1的引脚cs-共用;

6、可选地,所述ddr3sdram位于m1引脚为dr3_vss,与所述spi nand flash位于m1的引脚wp-/sio2共用;

7、可选地,所述ddr3sdram位于n1引脚为dr3_vdd,与所述spi nand flash位于n1的引脚spi_vcc共用。

8、可选地,所述ddr3sdram位于p1引脚为dr3_vss,与所述spi nand flash位于p1的引脚spi_vss共用。

9、本发明技术方案通过采用一种采用bga96封装的多存储信号复用式smcp芯片,包括96球设计的pcb基板、设于所述pcb基板上的ddr3sdram、spi nand flash、第一电阻阵列及第二电阻阵列,所述spi nand flash借助所述第一电阻阵列和第二电阻阵列与ddr3sdram建立引脚共用,以完成封装,利用现有的bga96封装,可以向上兼容现有的电路板设计,做到引脚最少,芯片合二为一,有效节省了空间,降低了成本,提高了emi性能效果。

技术特征:1.一种采用bga96封装的多存储信号复用式smcp芯片,其特征在于,包括:96球设计的pcb基板、设于所述pcb基板上的ddr3sdram、spi nand flash、第一电阻阵列及第二电阻阵列,所述spi nand flash借助所述第一电阻阵列和第二电阻阵列与ddr3sdram建立引脚共用,以完成封装。

2.如权利要求1所述的smcp芯片,其特征在于,所述spi nand flash和所述ddr3sdram垂直堆叠封装。

3.如权利要求2所述的smcp芯片,其特征在于,所述ddr3sdram与spi nand flash共用的引脚包括j1、j9、l1、l9、m1、m7、n1、p1。

4.如权利要求3所述的smcp芯片,其特征在于,所述ddr3sdram位于j1引脚为nc,与所述spi nand flash位于j1的引脚cs-共用。

5.如权利要求3所述的smcp芯片,其特征在于,所述ddr3sdram位于m1引脚为dr3_vss,与所述spi nand flash位于m1的引脚wp-/sio2共用。

6.如权利要求3所述的smcp芯片,其特征在于,所述ddr3sdram位于n1引脚为dr3_vdd,与所述spi nand flash位于n1的引脚spi_vcc共用。

7.如权利要求1所述的smcp芯片,其特征在于,所述ddr3sdram位于p1引脚为dr3_vss,与所述spinand flash位于p1的引脚spi_vss共用。

技术总结本发明公开一种采用BGA96封装的多存储信号复用式SMCP芯片,包括:96球设计的PCB基板、设于所述PCB基板上的DDR3SDRAM、SPI NAND FLASH、第一电阻阵列及第二电阻阵列,所述SPI NAND FLASH借助所述第一电阻阵列和第二电阻阵列与DDR3SDRAM建立引脚共用,以完成封装。本发明的SMCP芯片利用现有的BGA96封装,可以向上兼容现有的电路板设计,做到引脚最少,芯片合二为一,有效节省了空间,降低了成本,提高了EMI性能效果。技术研发人员:张波受保护的技术使用者:深圳市芯存科技有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182613.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。