半导体存储装置及其控制方法与流程

- 国知局

- 2024-07-31 19:29:56

本发明关于半导体存储装置及其控制方法。

背景技术:

1、在既有的半导体存储装置,从外部输入的外部时钟信号中不同步操作的半导体存储装置来说,有虚拟静态随机存取存储体(pseudo-static random access memory,psram)(例如,专利文献1),其具有与sram(static random access memory,静态随机存取存储体)间存在互换性的接口。

2、图1中的(1)~图1中的(4)为时序图,说明这样的psram的读取操作。图1中的(1)为一时序图,说明读取操作整体;图1中的(2)~图1中的(4)为时序图,详细说明读取操作的结束。此psram中,采用ddr(double data rate,双重数据速率)方式作为数据传送方式,在芯片选择信号cs#被设为有效(低准位)时进行读取操作。数据信号dq具有既定的长度(例如,16位元),包含指令、地址(列地址、行地址)以及读取数据。数据信号dq对应外部时钟信号ck而进行输入或输出。

3、图1所示的范例中,在时刻t01,当芯片选择信号cs#从无效(negate)(高准位)变为有效(assert)时,对应于外部时钟信号ck的第1时钟至第3时钟,输入包含指令、列地址以及行地址的数据信号dq。另外,延迟计数(latency count)从时刻t01之后的时刻t02开始,在延迟计数后的下一个外部时钟(图例中,第7时钟)的上升边缘,开始读取输出的数据。然后,对应于外部时钟信号ck的上升边缘以及下降边缘,输出读取数据(图例中,(dn,a)、(dn,b)、(dn+1,a)、(dn+1,b))。

4、此处,芯片选择信号cs#设为有效的期间内,最后的外部时钟信号ck(图例中,第8时钟)的下降边缘算起,至最后的读取数据(dn+1,b)的输出开始为止的期间,设为第1期间tckd。另外,从最后的外部时钟信号(第8时钟)算起,至芯片选择信号cs#设为无效的期间,设为既定期间tcsh。另外,芯片选择信号cs#从有效变为无效的时间点算起,至数据信号dq的输出结束为止的期间,设为第2期间toz。另外,既定期间tcsh、第1期间tckd、以及第2期间toz,一般以psram的规格来设定。

5、此处,第1期间tckd设定最大值5ns,最小值0ns;而第2期间toz只有设定最大值5ns,但没有设定最小值。另外,既定的期间tcsh只有设定最小值0ns,但没有设定最大值。因此,举例来说,若将既定的期间tcsh设为最小值(0ns),当第1期间tckd与第2期间toz的大小关系为tckd>toz时,就有可能如图1中的(2)所示,在数据信号dq的最后读取数据输出之前,读取操作就结束了,因此无法输出最后的读取数据。

6、为了防止上述情况,并且结束最后读取数据的输出,因此,考虑如图1中的(3)所示,将既定的期间tcsh设定为远大于0ns;或是如图1中的(4)所示,于第8时钟之后的第9时钟,输出虚拟数据(图例中,为(dn+2,a)),并于第9时钟的下降边缘使芯片选择信号cs#变为无效。然而,图1中的(3)、图1中的(4)的情况下,读取周期时间将变长,芯片选择信号cs#延迟使得待机时间也跟着变长,对下一个读取操作将带来影响。另外,图1中的(4)的情况下,由于在最后的读取数据之后将输出不必要的数据(虚拟数据),造成输出不必要数据所造成主动消耗电流增加的问题。

技术实现思路

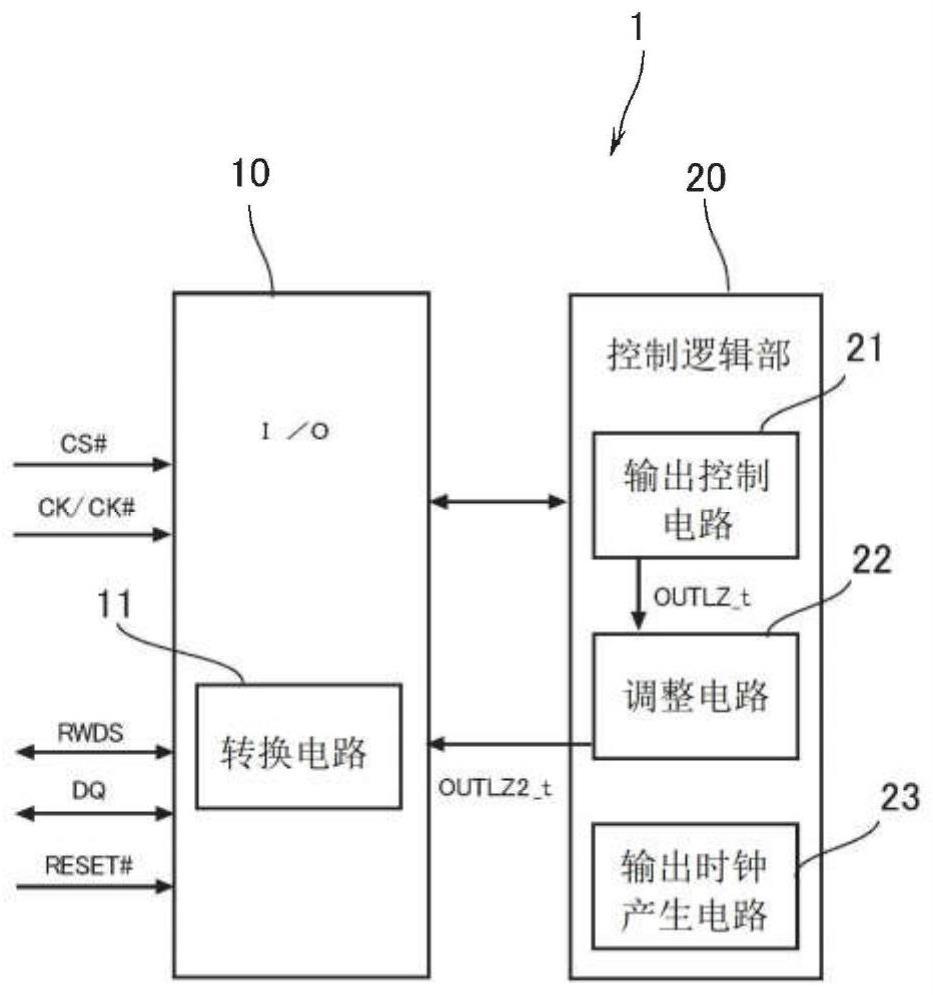

1、为了解决上述课题,本发明提供一种半导体存储装置,包含:调整电路,用以设定一第2期间长于一第1期间,调整最后读取数据的输出时间点;当芯片选择信号设为有效时,半导体存储装置根据一外部时钟信号进行数据的读取操作;第1期间是外部时钟信号以上升或下降的形式变化的时间点算起,至最后读取数据的输出开始为止的期间;第2期间是芯片选择信号从有效变为无效的时间点算起,至最后读取数据的输出结束为止的期间;外部时钟信号,是用来对读取操作中的最后读取数据进行读取。

2、另外,本发明提供一种半导体存储装置的控制方法,包含:由设置于半导体存储装置的调整电路,设定一第2期间长于一第1期间,调整最后读取数据的输出时间点;当芯片选择信号设为有效时,半导体存储装置根据一外部时钟信号进行数据的读取操作;第1期间是外部时钟信号以上升或下降的形式变化的时间点算起,至最后读取数据的输出开始为止的期间;第2期间是芯片选择信号从有效变为无效的时间点算起,至最后读取数据的输出结束为止的期间;外部时钟信号,是用来对读取操作中的最后读取数据进行读取。

技术特征:1.一种半导体存储装置,其特征在于,包含:

2.如权利要求1所述的半导体存储装置,

3.如权利要求1所述的半导体存储装置,

4.如权利要求1所述的半导体存储装置,

5.如权利要求4所述的半导体存储装置,

6.如权利要求4所述的半导体存储装置,

7.如权利要求6所述的半导体存储装置,

8.如权利要求7所述的半导体存储装置,

9.一种半导体存储装置,其特征在于,包含:

10.一种半导体存储装置的控制方法,其特征在于,包含:

11.如权利要求10所述的半导体存储装置的控制方法,

12.如权利要求10所述的半导体存储装置的控制方法,

13.如权利要求12所述的半导体存储装置的控制方法,

14.如权利要求12所述的半导体存储装置的控制方法,

15.如权利要求12所述的半导体存储装置的控制方法,

技术总结一种半导体存储装置及其控制方法,当芯片选择(chip select)信号设为有效时,响应于外部时钟信号进行数据的读取操作,其中半导体存储装置包含:调整电路,调整最后读取数据的输出时间点,使第2期间变得比第1期间还要长;其中第1期间是外部时钟信号以上升或下降形式变化的时间点算起,至最后读取数据的输出开始为止的期间;第2期间是芯片选择信号从有效(assert)变为无效(negate)的时间点算起,至最后读取数据的输出结束为止的期间。外部时钟信号是用来对读取操作中的最后读取数据进行读取。技术研发人员:森郁受保护的技术使用者:华邦电子股份有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182786.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表