读取等待时间延时反馈电路、反馈方法与流程

- 国知局

- 2024-07-31 19:30:34

本发明涉及及存储器芯片设计,具体地说,涉及半导体存储存储器中为实现固定读取等待时间而设计的存储结构读取等待时间延时反馈电路,以及本发明还涉及基于读取等待延时反馈方法设计的延时反馈方法。

背景技术:

1、以动态随机存取存储器为例,数据的一次读取过程,可以大致地概括为需要经历如下的步骤:

2、step1:控制器向动态随机存取存储器(dram)发出读取数据的指令;

3、step2:随机存取存储器对数据存储阵列中的数据进行读取;

4、step3:读取后的数据被发送并出现在数据输入输出(dq)引脚上。

5、而实际读取过程中,控制器向dram发送的,多为连续的读取指令,这些连续读取指令会被指令缓存器(cmd-fifo)暂存,再按照发出的顺次逐个执行,同时在存储阵列中,伴随读取指令的执行不断地从存储器中读取出数据。考虑到在每次读取操作中,读取指令的传输和/或处理时间,以及读取数据的长度、数据发送的时间等参数可能各不相同,自然就有必要让读取指令和其所需读取的数据实现一一对应,以期保证数据读取的准确性。

6、继续参看上述过程,事实上,由于内存需要耗时对存储阵列进行访问,因此自控制器发出读取指令,至数据最终出现在输入输出引脚上,这之间本就存在一个很短的物理时间间隔。换句话,存储阵列中的数据的读取,需要经历一个等待时间。现有技术在此基础上,通过延长前述的物理时间间隔,以实现了数据读取指令的固定等待时间,也即读取等待时间(cas latency)。

7、具体情形可参照图1,图1为示意图,示出了读取等待时间的时序关系,图中包含了两条时钟信号,分别为外部时钟信号(vclk),和数据时钟信号(dqs),以及两条总线,分别指令总线(cmd)和数据总线(data)。如图,指令read是控制器向随机存取存储器发送的连续读取指令中的一条,其期望是从存储阵列中读取一条由{d0至d7}构成的连续数据。在dram收到read指令(也即外部时钟信号的第二个上升沿信号到来时),至数据d0出现在数据总线上(也即数据时钟信号的第八个上升沿信号到来时),这之间存在一个如图中曲线所示时间间隔。

8、现有技术对该时间间隔按照时钟周期的整数倍进行延长,也即是latency延时。具体是例如,若读取等待时间设置为是五个时钟周期时,则在获得与外部时钟同步的任意读指令之后,所期望读取数据中的第一个数据(d0),会在五个时钟周期后与外部时钟同步地输出。也即,对于任何一个读取指令,都延迟五个时钟脉冲后输出数据。或者换言之,读取等待时间latency的时长设置,也即可以被视为是时钟周期的整数倍。例如回看图1,在dram收到read指令至数据d0出现在数据总线上,从两个时钟的第二到第八个上升沿信号之间,经历了时长为整数个时钟周期的读取等待时间。而对这个等待时间进行计数的设备就被称为读取等待时间计数器(latency counter)。在读取等待时间计数器的基础上,为实现前述固定的读取等待时间,命令缓存器会将接受到的读取指令进行暂存,并按照固定的读取等待时间(换句话说,是计数器的固定计数)后将其送出。

9、现有技术利用等待时间计数器采用的具体做法是,为介于输出指针和输入指针之间的一个指针地址配置一条延迟线,该条延迟线的延迟由读取等待时间计数器来控制。继而,可以设想,基于现有的上述配置方式,当输入和输出指针之间包含多个指针地址时,则需要为每一组输入和输出指针分别配置延迟线,且这些延迟线之间都必须满足固定的读取等待延时,才能实现数据传输的及时和准确。不难看出,该方式存在如下的技术问题:

10、1)随着输入和输出指针内指针地址数量的扩充,则相应地需要配置更多的延迟线来实现指针之间的延迟,而这势必导致芯片版图的臃肿;

11、2)随着延迟线的增加,保持各延迟线间固定的读取等待时间又极容易导致某两组或者某几组指针地址间的延迟配置出现失配,这种对延迟失配的敏感性,无疑增大了芯片版图设计复杂度和难度。

12、因此,应当对现有技术进行改进,以解决读取等待时间计数器实现中存在的上述技术问题。

技术实现思路

1、针对现有技术的不足,本发明提供了一种能够进一步减少读取等待时间反馈电路中延迟线数量的读取等待时间延时反馈电路、反馈方法,以解决上述的中至少一个技术问题。

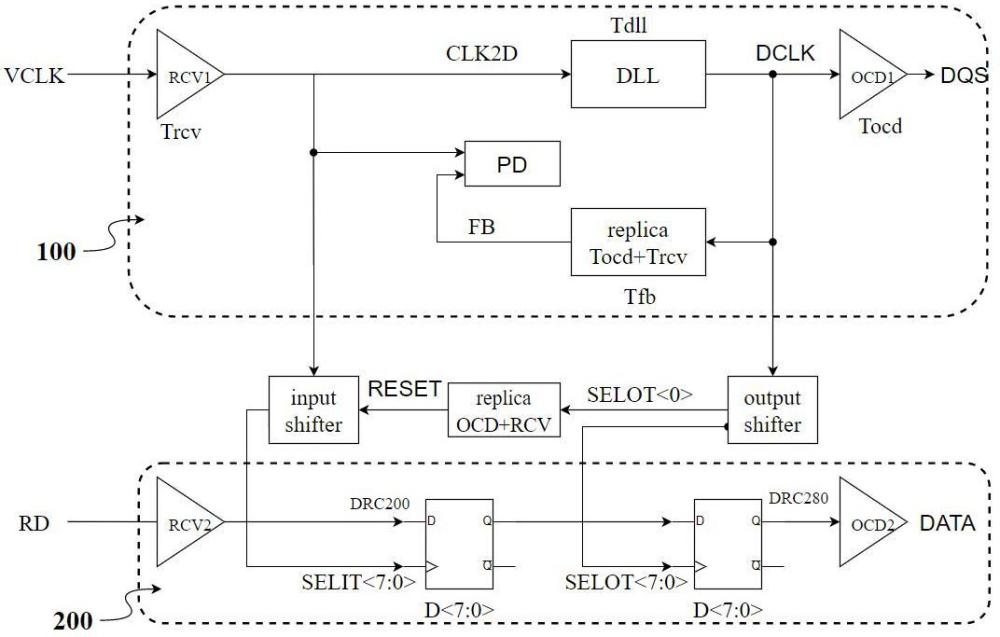

2、为解决以上技术问题,本发明的第一方面,是采取了一种读取等待时间反馈结构,其中,该结构包括:延时锁相回路,该延时锁相回路接收外部信号以放大得到第一时钟信号,再经由延时链输出第二时钟信号后通过第一离线驱动器输出数据时钟信号;指令缓存器,该指令缓存器接收指令数据,并由其第一时钟指针暂存后,经固定的第一时间间隔后由第二时钟指针输出,所述指令缓存器中指令信号由输入至输出的过程,与所述延时锁相回路接收所述外部信号至输出的过程同步;以及,还包括第一移位寄存单元和第二移位寄存单元,所述第一时钟信号经过所述第一移位寄存单元生成所述第一时钟指针,所述第二时钟信号经过所述第二移位寄存单元生成所述第二时钟指针,其中,所述第一时钟指针作为所述指令缓存器的输入指针,第二时钟指针作为所述指令缓存器的输出指针,所述第一移位寄存单元与第二移位寄存单元通过第一延时复制电路反馈延迟,所述第二时钟指针的首位输出通过所述第一延时复制电路得到重置信号,所述重置信号对所述第一移位寄存单元进行重置,以于所述第一时钟指针与第二时钟指针之间,按照所述第一时间间隔实现固定的等待时间。

3、作为本方案第一方面的一种优选地,所述延时锁相回路包括,所述第一移位寄存单元、第二移位寄存单元的级数,与第一时钟指针、第二时钟指针的位数、以及所述指令缓存器的深度之间构成对应。

4、作为本方案该方面进一步优选地,所述延时锁相回路包括:第一接收器,该第一接收器接收所述外部信号,并将外部信号放大以得到所述第一时钟信号;延时链,该锁相回路接收所述第一时钟信号,并锁相后输出一个延时链输出时钟信号;第一离线驱动器,该第一离线驱动器接收所述延时链输出时钟信号,并离线驱动后输出所述数据时钟信号;第二延时复制电路,该第二延时复制电路复制所述延时链输出时钟信号的延时,并将生成反馈信号反馈至鉴相器,鉴相器将所述反馈信号和所述第一时钟信号的鉴相结果反馈至所述延时链,以调整所述延时链的输出时钟信号;所述反馈结构还包括:第二接收器,该第二接收器接收所述指令数据并放大得到放大数据信号;第二离线驱动器,第二离线驱动器接收所述输出指针地址输出的数据,离线驱动后输出。

5、作为本方案的更进一步优选地,所述第一时钟指针作为所述指令缓存器的输入指针,第二时钟指针作为所述指令缓存器的输出指针,具体为:所述指令缓存器包括第一触发器和第二触发器,所述第一触发器以所述第二接收器的输出为输入,由所述第一时钟指针为触发,并向所述第二触发器输出数据;所述第二触发器以所述第一触发器的输出为输入,以所述第二时钟指针为触发,并向所述第二离线驱动器输出数据。

6、作为本方案的再进一步优选地,所述第一移位寄存单元和第二移位寄存单元为由多个触发器串联构成的寄存结构,所述第二移位寄存单元的首位输出被接至所述第一延时复制电路。

7、本发明的第二方面,是提供一种读取等待时间反馈方法,其中,该方法包括如下步骤:在延时锁相回路和指令缓存器之间配置第一移位寄存单元和第二移位寄存单元的步骤,第一移位寄存单元被配置为根据所述延时锁相回路中接收器的输出生成第一时钟指针,第二移位寄存单元被配置为根据所述延时锁相回路中延时链的输出生成第二时钟指针;将所述第一时钟指针作为所述指令缓存器的输入指针地址,将所述第二时钟指针作为指令缓存器的输出指针地址的步骤;将所述第一移位寄存单元和第二移位寄存单元通过延时复制电路连接的步骤,并且,将所述第二移位寄存单元的首位输出接至延时复制电路,以输出重置信号;当所述第二移位寄存单元的首位存在输出时,通过重置信号对所述第一移位寄存单元进行重置,从而实现所述指令缓存器输入和输出指针之间的延迟反馈。

8、作为本发明第二方面的一种优选地,还包括,令所述移位寄存单元移位寄存单元的级数,与时钟指针的位数、以及指令缓存器的深度构成一一对应。

9、由于以上技术方案的采用,本发明相较于现有技术具有如下的有益技术效果:

10、现有技术下,通常需要根据指针地址的位数配置相应数量的延迟线,而采用编码的方式虽然一定程度上能解决延迟线失配,但由于该方式下仍需要一定数量的延迟线实现输出指针地址转码再译码,仍存在编码延迟线间的失配可能。在本发明的较佳实施例中,增设了一组延时复制电路以及两个移位寄存器,将对应输出指针地址的移位寄存器的首位输出通过该延时复制电路进行反馈,生成一个信号对另一个移位寄存器进行重置,以实现两移位寄存器生成的输入和输出指针间的延迟与延时锁相回路中的时钟延迟保持一致,另一方面,两个移位寄存器生成的指针地址分别对应指令寄存器的输入和输出,这样,实现了时钟信号和数据信号保持相同的延迟,在输入和输出上保持同步。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182827.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表