一种适用于相变存储的自加载存储结构的制作方法

- 国知局

- 2024-07-31 19:45:06

本发明涉及集成电路,特别涉及一种适用于相变存储的自加载存储结构。

背景技术:

1、随着我国武器装备、航空航天、核工业领域的发展,对高可靠、抗辐射的可编程逻辑器件(programmable logic device,pld)的需求越为突出。在新一代航天工程中,侦察卫星、导航系统等整机系统需要高抗辐射特性、高可靠产品。如何发展下一代高性能、高可靠、低功耗非易失fpga核心配置单元,已成为集成电路领域的热门研究课题之一。

2、按照编程方式的区别,fpga技术可以分为三类:基于反熔丝工艺的fpga、基于sram工艺的fpga和基于flash型的fpga。基于反熔丝工艺的fpga,不需要外部专业的存储器来存储配置文件,掉电后配置信息不丢失,使用方便,开发成本低,并且反熔丝在配置完成后,内部的配置信息无法读出,因此反熔丝fpga具有很好的保密性。并且,优越的抗辐射特性也是基于反熔丝工艺的一大特点。但是,反熔丝fpga灵活性差,只能一次性编程,无法重复编程,如果更改了设计,必须编程新器件来替代旧器件。因此,对于fpga设计人员来说,使用上有较大难度。其次,反熔丝fpga容量较小,最大门数为400万门(microsemi公司的axcelerator系列的ax4000),如果航天探测任务复杂,反熔丝fpga无法满足任务的需求。

3、基于sram工艺的fpga通过内部的sram单元来配置存储信息,能够无限次的进行配置和擦除,是目前主流的fpga配置技术,但是配置完成后掉电重启配置信息会全部丢失,需要外接非易失性存储器来存储配置信息,如flash或eeprom等,而外部存储器的配置信息很有可能被窃取,导致其安全性降低,并且外部存储器的抗辐照性能也需要进行考虑。

4、基于flash工艺的fpga不需要外部非易失存储器,配置信息保存在内部flash开关中,断电重启后,配置信息不会丢失。flash型fpga同时具备sram型fpga可重复编程和反熔丝型fpag非易失性的特点,并且flash开关结构使得flash fpga晶体管数量大大减少,静态功耗也降低。但是,flash型fpga存在一定的局限性,flash型fpga的存储单元擦写次数是有限的,只有几百次左右;其次,与sram型fpga相比,flash型fpga的工艺较为落后,器件规模和密度也远低于sram型的fpga。

技术实现思路

1、本发明的目的在于提供一种适用于相变存储的自加载存储结构,以解决背景技术中的问题。

2、为解决上述技术问题,本发明提供了一种适用于相变存储的自加载存储结构,包括sram单元结构、相变存储结构、相变存储单元编程通路、sram单元自加载时序;

3、所述相变存储单元编程通路用于将配置数据通过编程通路存储到所述相变存储结构中的相变存储单元中;

4、所述相变存储结构用来存储配置的数据;

5、所述sram单元自加载时序将所述相变存储结构中存储的配置数据加载到所述sram单元结构中;

6、所述sram单元结构用于加载所述相变存储结构中存储的配置数据。

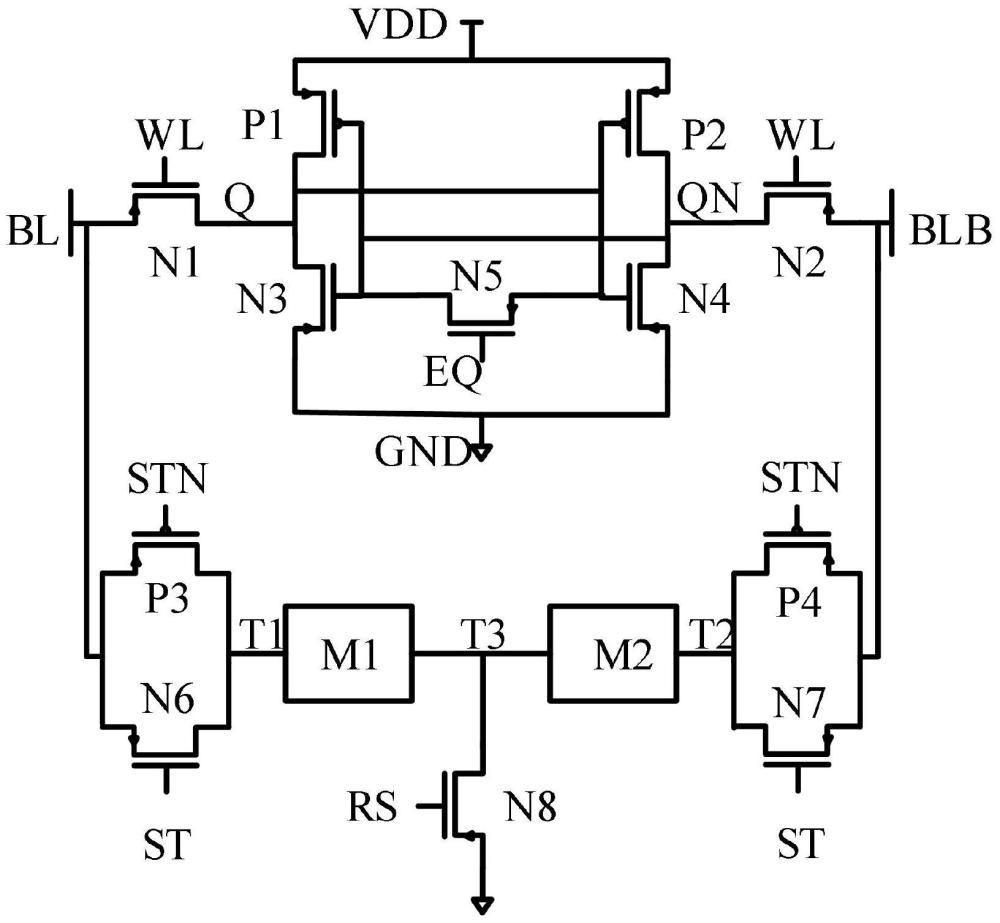

7、在一种实施方式中,所述sram单元结构包括第一传输mos管、第二传输mos管、第一负载mos管、第二负载mos管、第一驱动mos管、第二驱动mos管、第一平衡mos管;所述第一负载mos管、所述第一驱动mos管、所述第二负载mos管、所述第二驱动mos管组成交叉耦合反向器结构,形成第一存储节点和第二存储节点;所述第一传输mos管的源端连接第一输入节点,所述第二传输mos管的源端连接第二输入节点,所述第一传输mos管的栅端和所述第二传输mos管的栅端连接第五输入节点,所述第一平衡mos管的栅端连接第六输入节点。

8、在一种实施方式中,所述相变存储结构包括第三传输mos管、第四传输mos管、第五传输mos管、第六传输mos管、第一相变存储单元、第二相变存储单元、第一开关mos管;所述第三传输mos管的源端和所述第五传输mos管的源端连接所述第一输入节点,所述第四传输mos管的源端和所述第六传输mos管的源端连接所述第二输入节点,所述第三传输mos管的栅端和所述第四传输mos管的栅端连接第七输入节点,所述第五传输mos管的栅端和所述第六传输mos管的栅端连接第四输入节点,所述第一开关mos管的栅端连接第三输入节点。

9、在一种实施方式中,所述第一相变存储单元的一端连接第一传输节点,另一端连接第三传输节点,所述第二相变存储单元的一端连接第二传输节点,另一端连接所述第三传输节点;所述第三传输节点经过所述第一开关mos管与地连接。

10、在一种实施方式中,所述相变存储单元编程通路包括第一相变存储单元编程通路和第二相变存储单元编程通路;

11、所述第一输入节点、所述第三传输mos管、所述第五传输mos管、所述第一开关mos管共同构成所述第一相变存储单元编程通路;

12、所述第二输入节点、所述第四传输mos管、所述第六传输mos管、所述第一开关mos管共同构成所述第二相变存储单元编程通路。

13、在一种实施方式中,所述适用于相变存储的自加载存储结构的编程时序是通过所述相变存储单元编程通路对第一相变存储单元和第二相变存储单元进行编程,将数据存储在非易失的第一相变存储单元和第二相变存储单元中,编程时序包括上电、编“1”、保持、编“0”共计4个状态;

14、上电时,所述第一输入节点和所述第二输入节点均为低电平;

15、编“1”时,所述第一输入节点=“0”,所述第二输入节点=“1”,当所述第二输入节点的编程电压大于所述第二相变存储单元的阈值电压时,所述第二相变存储单元由“高”阻态变为“低”阻态;同时,由于所述第一输入节点=“0”,所述第一相变存储单元保持“高”阻态不变;

16、保持时,所述第一输入节点和所述第二输入节点保持为高电平,同时,所述第三输入节点为低电平,所述第四输入节点为高电平,所述第五输入节点保持为低电平,所述第七输入节点为低电平,所述相变存储结构通路关断,所述sram单元结构处于保持状态;

17、编“0”时,所述第一输入节点=“1”,所述第二输入节点=“0”,当所述第一输入节点的编程电压大于所述第一相变存储单元的阈值电压时,所述第一相变存储单元由“高”阻态转变为“低”阻态;同时,由于所述第二输入节点=“0”,所述第二相变存储单元保持“高”阻态不变。

18、在一种实施方式中,所述适用于相变存储的自加载存储结构的加载时序将相变存储单元中的数据加载到所述第一存储节点和所述第二存储节点中,加载时序包括上电、预充和进行加载三个状态;

19、上电时,所述第一输入节点和所述第二输入节点均为低电平;

20、预充时,所述第一输入节点和所述第二输入节点均为vdd/2电平,此时所述第六输入节点为高电平,使所述第一存储节点和所述第二存储节点同电位;

21、进行加载时,所述第三输入节点变为高电平,所述第四输入节点变为高电平,所述第七输入节点变为低电平,所述第六输入节点变为低电平,将两个相变存储单元之间的第三传输节点接地,两个相变存储单元阻值不同,对所述第一输入节点和所述第二输入节点电压的下拉能力也不同,阻值较低的一侧将比另一侧电压下降的更快;当所述第一输入节点和所述第二输入节点产生足够的电压差时,所述第五输入节点拉高,将已经平衡的存储节点连接到所述第一输入节点和所述第二输入节点;由于sram单元结构中的交叉耦合反相器结构,阻值较低一侧的存储节点会被下拉为0,阻值较高的另一侧会被驱动至高电平,相变存储单元中的数据加载到sram单元结构中的存储节点中。

22、在一种实施方式中,所述相变存储单元是一种非易失存储单元,利用材料的可逆转的相变来存储信息。

23、本发明提供的一种适用于相变存储的自加载存储结构,具有以下有益效果:

24、(1)采用相变存储单元组作为编程器件,可实现fpga掉电后配置在相变存储单元组中的数据不会丢失;

25、(2)相比较传统的sram型fpga,无需再上电时从外部的配置存储器读取数据运行,启动速度快,并且数据可靠性和保密性更高;

26、(3)与flash型fpga相比较,基于相变存储单元特性,拥有更高的擦写次数,并且器件规模和密度可以做到更高;

27、(4)与反熔丝型fpga相比较,拥有更高的灵活性,器件规模可以做到更高,并且可以定时刷新。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183846.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。