移位寄存器及其驱动方法、显示面板与流程

- 国知局

- 2024-07-31 19:48:00

本公开涉及显示,具体而言,涉及一种移位寄存器及其驱动方法、显示面板。

背景技术:

1、目前为了降低成本,面板中都会采用栅极驱动电路设计(gate driver on array,简称goa)。氧化物oled技术是目前panel设计的主流技术,随机sense功能可以消除扫描线所以是氧化物oled goa必备技术之一,但是通常电路结构会比较复杂。相关技术中,goa电路因为下拉结点需要长时间的保持高压使得下拉节点控制的晶体管都是处于正偏压状态,导致下拉晶体管的正偏压太大而引起goa电路失效。

技术实现思路

1、本公开的目的在于克服上述现有技术的不足,提供一种移位寄存器及其驱动方法、显示面板。

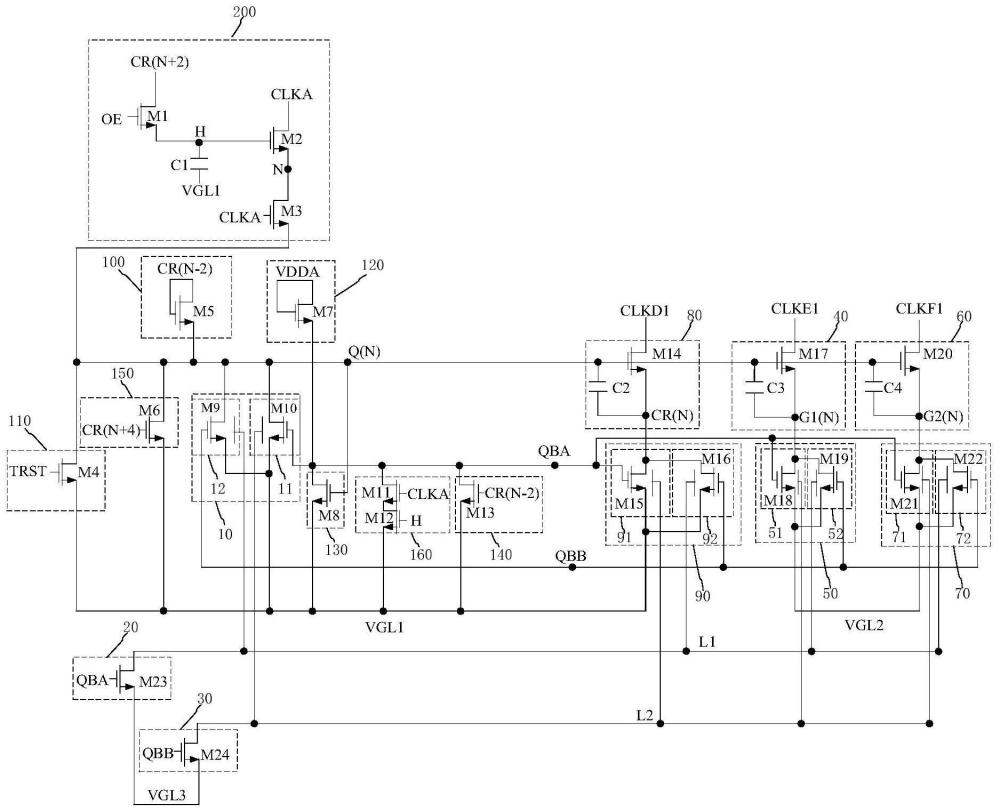

2、根据本公开的一个方面,提供一种移位寄存器,包括多个移位寄存器单元,所述移位寄存器单元包括:补偿电路,连接第一控制信号端、补偿节点并接收所述第三电平信号,所述补偿电路用于响应所述第一控制信号端的信号将所述第三电平信号传输至所述补偿节点;第一节点控制电路,包括晶体管,所述第一节点控制电路连接第二控制节点、第一控制节点和所述补偿节点并接收第一电平信号,所述第一节点控制电路用于响应所述第一控制节点的信号利用所述第一电平信号复位所述第二控制节点或者响应所述补偿节点的信号控制位于其内的晶体管反向偏置;其中,所述晶体管的导通电平与所述第一电平信号和所述第三电平信号的极性相反,且所述第三电平信号的信号幅值大于所述第一电平信号的信号幅值。

3、在本公开的示例性实施例中,所述补偿电路包括:补偿晶体管,第一极连接所述补偿节点,第二极接收所述第三电平信号,栅极连接所述第一控制信号端,所述补偿晶体管用于响应所述第一控制信号端的信号将所述第三电平信号传输至所述补偿节点。

4、在本公开的示例性实施例中,所述第一控制节点包括第一子控制节点和第二子控制节点,所述补偿节点包括第一补偿节点和第二补偿节点;所述补偿电路包括:第一补偿电路,连接所述第一子控制节点、所述第一补偿节点并接收所述第三电平信号,所述第一补偿电路用于响应所述第一子控制节点的信号将所述第三电平信号传输至所述第一补偿节点;第二补偿电路,连接所述第二子控制节点、所述第二补偿节点并接收所述第三电平信号,所述第二补偿电路用于响应所述第二子控制节点的信号将所述第三电平信号传输至所述第二补偿节点;所述第一节点控制电路包括第一子节点控制电路和第二子节点控制电路,所述第一子节点控制电路和所述第二子节点控制电路均包括晶体管,所述第一节点控制电路连接所述第二控制节点、所述第一子控制节点、所述第二子控制节点、所述第一补偿节点和所述第二补偿节点并接收第一电平信号,所述第一节点控制电路用于响应所述第一子控制节点的信号利用所述第一子节点控制电路接收所述第一电平信号复位所述第二控制节点并响应所述第一补偿节点的信号控制所述第二子节点控制电路反向偏置,或者用于响应所述第二子控制节点的信号利用所述第二子节点控制电路接收所述第一电平信号复位所述第二控制节点并响应所述第二补偿节点的信号控制所述第一子节点控制电路反向偏置;其中,在显示阶段,所述第一子控制节点的信号与所述第二子控制节点的信号反相;所述第一子节点控制电路和所述第二子节点控制电路中晶体管的导通电平均与所述第一电平信号和所述第三电平信号的极性相反。

5、在本公开的示例性实施例中,所述第一补偿电路、所述第二补偿电路、所述第一子节点控制电路和所述第二子节点控制电路中的晶体管类型相同。

6、在本公开的示例性实施例中,所述第三电平信号的信号幅值与所述第一电平信号的信号幅值的差值大于所述第一子节点控制电路和所述第二子节点控制电路中晶体管的阈值电压。

7、在本公开的示例性实施例中,所述第一子节点控制电路连接所述第二控制节点、所述第一子控制节点、所述第二补偿节点并接收所述第一电平信号,所述第一子节点控制电路用于响应所述第一子控制节点的信号利用所述第一电平信号复位所述第二控制节点,或者用于响应所述第二补偿节点的信号控制位于其内的晶体管进行反向偏置;所述第二子节点控制电路连接所述第二控制节点、所述第二子控制节点、所述第一补偿节点并接收所述第一电平信号,所述第二子节点控制电路用于响应所述第二子控制节点的信号利用所述第一电平信号复位所述第二控制节点,或者用于响应所述第一补偿节点的信号控制位于其内的晶体管进行反向偏置。

8、在本公开的示例性实施例中,多个所述移位寄存器单元包括第一移位寄存器单元和第二移位寄存器单元,所述第一移位寄存器单元与所述第二移位寄存器单元构成一重复单元;其中,同一重复单元中,所述第一移位寄存器单元和所述第二移位寄存器单元复用同一所述第一补偿电路和同一所述第二补偿电路。

9、在本公开的示例性实施例中,同一重复单元中,所述第一移位寄存器单元的第一子控制节点、第二子控制节点与所述第二移位寄存器单元中的第一子控制节点、第二子控制节点对应连接。

10、在本公开的示例性实施例中,所述第一补偿电路包括:第二十三晶体管,第一极连接所述第一补偿节点,第二极接收所述第三电平信号,栅极连接所述第一子控制节点,所述第二十三晶体管用于响应所述第一子控制节点的信号将所述第三电平信号传输至所述第一补偿节点;所述第二补偿电路包括:第二十四晶体管,第一极连接所述第二补偿节点,第二极接收所述第三电平信号,栅极连接所述第二子控制节点,所述第二十四晶体管用于响应所述第二子控制节点的信号将所述第三电平信号传输至所述第二补偿节点。

11、在本公开的示例性实施例中,所述第二十三晶体管和所述第二十四晶体管均为n型晶体管;所述第一电平信号、所述第三电平信号均为低电平信号。

12、在本公开的示例性实施例中,所述移位寄存器单元还包括:第一输出电路,连接所述第二控制节点、第一输出端并接收第三时钟信号,所述第一输出电路用于响应所述第二控制节点的信号将所述第三时钟信号传输至所述第一输出端以输出第一输出信号;第二节点控制电路,包括第三子节点控制电路和第四子节点控制电路,所述第三下电路连接所述第一子控制节点、所述第二子控制节点、所述第一输出端、所述第一补偿节点和所述第二补偿节点并接收所述第二电平信号,所述第二节点控制电路用于响应所述第一子控制节点的信号利用所述第三子节点控制电路将所述第二电平信号传输至所述第一输出端以复位所述第一输出端并响应所述第一补偿节点的信号控制所述第四子节点控制电路反向偏置,或者用于响应所述第二子控制节点的信号利用所述第四子节点控制电路将所述第二电平信号传输至所述第一输出端以复位所述第一输出端并响应所述第二补偿节点的信号控制所述第三子节点控制电路反向偏置;第二输出电路,连接所述第二控制节点、第二输出端并接收第四时钟信号,所述第二输出电路用于响应所述第二控制节点的信号将所述第四时钟信号传输至所述第二输出端以输出第二输出信号;第三节点控制电路,包括第五子节点控制电路和第六子节点控制电路,所述第三节点控制电路连接所述第一子控制节点、所述第二子控制节点、所述第二输出端、所述第一补偿节点和所述第二补偿节点并接收所述第二电平信号,所述第三节点控制电路用于响应所述第一子控制节点的信号利用所述第五子节点控制电路将所述第二电平信号传输至所述第二输出端以复位所述第二输出端并响应所述第一补偿节点的信号控制所述第六子节点控制电路反向偏置,或者响应所述第二子控制节点的信号利用所述第六子节点控制电路将所述第二电平信号传输至所述第二输出端以复位所述第二输出端并响应所述第二补偿节点的信号控制所述第五子节点控制电路反向偏置;其中,所述第三子节点控制电路、所述第四子节点控制电路、所述第五子节点控制电路和所述第六子节点控制电路均包括晶体管,且晶体管的导通电平与所述第二电平信号的极性相反,所述第二电平信号与所述第三电平信号极性相同且所述第二电平信号的信号幅值小于所述第三电平信号的信号幅值。

13、在本公开的示例性实施例中,所述第三电平信号的信号幅值与所述第二电平信号的信号幅值的差值大于所述第三子节点控制电路、所述第四子节点控制电路、所述第五子节点控制电路和所述第六子节点控制电路中晶体管的阈值电压。

14、在本公开的示例性实施例中,多个所述移位寄存器单元包括第一移位寄存器单元和第二移位寄存器单元,所述第一移位寄存器单元与所述第二移位寄存器单元构成一重复单元;所述第一移位寄存器单元还包括:级联输出电路,连接所述第二控制节点、级联输出端并接收第二时钟信号,所述级联输出电路用于响应所述第二控制节点的信号将所述第二时钟信号传输至所述级联输出端以输出级联控制信号;第四节点控制电路,包括第七子节点控制电路和第八子节点控制电路,所述第四节点控制电路连接所述第一子控制节点、所述级联输出端、所述第二子控制节点、所述第一补偿节点和所述第二补偿节点并接收所述第一电平信号,所述第四节点控制电路用于响应所述第一子控制节点的信号利用所述第七子节点控制电路将所述第一电平信号传输至所述级联输出端以初始化所述级联输出端并响应所述第一补偿节点的信号控制所述第八子节点控制电路反向偏置,或者用于响应所述第二子控制节点的信号利用所述第八子节点控制电路将所述第一电平信号传输至所述级联输出端以初始化所述级联输出端并响应所述第二补偿节点的信号控制所述第七子节点控制电路反向偏置。

15、在本公开的示例性实施例中,所述第一输出电路还连接所述第一补偿节点或所述第二补偿节点,所述第一输出电路还用于响应所述第一补偿节点的信号或所述第二补偿节点的信号进行反向偏置;所述第二输出电路还连接所述第一补偿节点或所述第二补偿节点,所述第二输出电路还用于响应所述第一补偿节点的信号或所述第二补偿节点的信号进行反向偏置。

16、在本公开的示例性实施例中,所述第一子节点控制电路包括:第十晶体管,第一极连接所述第二控制节点,第二极接收所述第一电平信号,第一栅极连接所述第一子控制节点,第二栅极连接所述第二补偿节点,所述第十晶体管用于响应所述第一子控制节点的信号将所述第一电平信号传输至所述第二控制节点复位所述第二控制节点或者响应所述第二补偿节点的信号进行反向偏置;所述第二子节点控制电路包括:第九晶体管,第一极连接所述第二控制节点,第二极接收所述第一电平信号,第一栅极连接所述第二子控制节点,第二栅极连接所述第一补偿节点,所述第九晶体管用于响应所述第二子控制节点的信号将所述第一电平信号传输至所述第二控制节点复位所述第二控制节点或响应所述第一补偿节点的信号进行反向偏置;所述第一输出电路包括:第十七晶体管,第一极接收所述第三时钟信号,第二极连接所述第一输出端,第一栅极连接所述第二控制节点,第二栅极连接所述第一补偿节点或所述第二补偿节点,所述第十七晶体管用于响应所述第二控制节点的信号将所述第三时钟信号传输至所述第一输出端以输出第一输出信号或者用于响应所述第一补偿节点的信号进行反向偏置;第三电容,第一极连接所述第二控制节点,第二极连接所述第一输出端;所述第三子节点控制电路包括:第十八晶体管,第一极连接所述第一输出端,第二极接收所述第二电平信号,第一栅极连接所述第一子控制节点,第二栅极连接所述第二补偿节点,所述第十八晶体管用于响应所述第一子控制节点的信号将所述第二电平信号传输至所述第一输出端以复位所述第一输出端,或者用于响应所述第二补偿节点的信号进行反向偏置;所述第四子节点控制电路包括:第十九晶体管,第一极连接所述第一输出端,第二极接收所述第二电平信号,第一栅极连接所述第二子控制节点,第二栅极连接所述第一补偿节点,所述第十九晶体管用于响应所述第二子控制节点的信号将所述第二电平信号传输至所述第一输出端以复位所述第一复位端,或者用于响应所述第一补偿节点的信号进行反向偏置;所述第二输出电路包括:第二十晶体管,第一极接收所述第四时钟信号,第二极连接所述第二输出端,第一栅极连接所述第二控制节点,第二栅极连接所述第一补偿节点或所述第二补偿节点,所述第二十晶体管用于响应所述第二控制节点的信号将所述第四时钟信号传输至所述第二输出端以输出第二输出信号或者用于响应所述第一补偿节点的信号或所述第二补偿节点的信号进行反向偏置;第四电容,第一极连接所述第二控制节点,第二极连接所述第二输出端;所述第五子节点控制电路包括:第二十一晶体管,第一极连接所述第二输出端,第二极接收所述第二电平信号,第一栅极连接所述第一子控制节点,第二栅极连接所述第二补偿节点,所述第二十一晶体管用于响应所述第一子控制节点的信号将所述第二电平信号传输至所述第二输出端以复位所述第二输出端,或者用于响应所述第二补偿节点的信号进行反向偏置;所述第六子节点控制电路包括:第二十二晶体管,第一极连接所述第二输出端,第二极接收所述第二电平信号,第一栅极连接所述第二子控制节点,第二栅极连接所述第一补偿节点,所述第二十二晶体管用于响应所述第二子控制节点的信号将所述第二电平信号传输至所述第二输出端以复位所述第二输出端,或者用于响应所述第一补偿节点的信号进行反向偏置;所述级联输出电路包括:第十四晶体管,第一极接收所述第二时钟信号,第二极连接所述级联输出端,栅极连接所述第二控制节点,所述第十四晶体管用于响应所述第二控制节点的信号将所述第二时钟信号传输至所述级联输出端以输出级联控制信号;第二电容,一端连接所述第二控制节点,另一端连接所述级联输出端;所述第七子节点控制电路包括:第十五晶体管,第一极连接所述级联输出端,第二极接收所述第一电平信号,第一栅极连接所述第一子控制节点,第二栅极连接所述第二补偿节点,所述第十五晶体管用于响应所述第一子控制节点的信号将所述第一电平信号传输至所述级联输出端以复位所述级联输出端,或者响应所述第二补偿节点的信号进行反向偏置;所述第八子节点控制电路包括:第十六晶体管,第一极连接所述级联输出端,第二极接收所述第一电平信号,第一栅极连接所述第二子控制节点,第二栅极连接所述第一补偿节点,所述第十六晶体管用于响应所述第二子控制节点的信号将所述第一电平信号传输至所述级联输出端以对复位所述级联输出端,或者用于响应所述第二补偿节点的信号进行反向偏置。

17、在本公开的示例性实施例中,所述第九晶体管、所述第十晶体管以及所述第十四晶体管~所述第二十二晶体管、均为n型晶体管。

18、在本公开的示例性实施例中,所述移位寄存器单元还包括:第一控制电路,包括第一子控制电路和第二子控制电路,所述第一子控制电路连接第一电源端和所述第一子控制节点,所述第二子控制电路连接第二电源端和所述第二子控制节点,所述第一子控制电路用于响应所述第一电源端提供的第一电压信号将所第一电压信号传输至所述第一子控制节点,所述第二子控制电路用于响应所述第二电源端提供的第二电压信号将所述第二电压信号传输至所述第二子控制节点;输入电路,连接输入控制端和所述第二控制节点,所述输入电路用于响应所述输入控制端提供的输入控制信号将所述输入控制信号传输至所述第二控制节点;第一重置电路,连接第一重置控制端、所述第二控制节点并接收所述第一电平信号,所述第一重置电路用于响应所述第一重置控制端的信号将所述第一电平信号传输至所述第二控制节点重置所述第二控制节点;第二重置电路,连接所述第二控制节点和第二重置控制端并接收所述第一电平信号,所述第二重置电路用于响应所述第二重置控制端的信号将所述第一电平信号传输至所述第二控制节点以重置所述第二控制节点;第三重置电路,包括第一子重置电路和第二子重置电路,所述第一子重置电路连接所述第二控制节点、所述第一子控制节点并接收所述第一电平信号,用于响应所述第二控制节点的信号将所述第一电平信号传输至所述第一子控制节点以重置所述第一子控制节点;所述第二子节点控制电路连接所述第二控制节点、所述第二子控制节点并接收所述第一电平信号,用于响应所述第二控制节点的信号将所述第一电平信号传输至所述第二子控制节点以重置所述第二子控制节点;第四重置电路,包括第三子重置电路和第四子重置电路,所述第三子重置电路连接所述输入信号端、所述第一子控制节点并接收所述第一电平信号,用于响应所述输入信号端的信号将所述第一电平信号传输至所述第一子控制节点以重置所述第一子控制节点;所述第四子重置电路连接所述输入信号端、所述第二子控制节点并接收所述第一电平信号,用于响应所述输入信号端的信号将所述第一电平信号传输至所述第二子控制节点以重置所述第二子控制节点;感测电路,连接第一感测控制端、第二感测控制端、预存节点和公共节点并接收第一时钟信号,所述感测电路用于响应所述第一感测控制端的信号将所述第二感测控制端的信号写入所述预存节点进行保存并利用所述预存节点的信号将所述第一时钟信号传输至所述公共节点;隔离电路,连接所述预存节点和所述第二控制节点并接收所述第一时钟信号,用于响应所述第一时钟信号将所述公共节点的信号传输至所述第二控制节点;感测复位电路,包括第一子复位电路和第二子复位电路,第一子复位电路连接所述第一子控制节点和所述预存节点并接收所述第一时钟信号和所述第一电平信号,用于响应所述第一时钟信号和所述预存节点的信号将所述第一电平信号传输至所述第一子控制节点以在感测阶段复位所述第一子控制节点;所述第二子复位电路连接所述第二子控制节点和所述预存节点并接收所述第一时钟信号和所述第一电平信号,用于响应所述第一时钟信号和所述预存节点的信号将所述第一电平信号传输至所述第二子控制节点以在感测阶段复位所述第二子控制节点;其中,所述第一电压信号与所述第二电压信号反相。

19、在本公开的示例性实施例中,多个所述移位寄存器单元包括第一移位寄存器单元和第二移位寄存器单元,所述第一移位寄存器单元与所述第二移位寄存器单元构成一重复单元;其中,同一重复单元中,所述第一移位寄存器单元与所述第二移位寄存器单元复用同一所述感测电路;所述第一子控制电路、所述第一子重置电路和所述第三子重置电路位于所述第一移位寄存器单元中,所述第二子控制电路、所述第二子重置电路和所述第四子重置电路位于所述第二移位寄存器单元中。

20、在本公开的示例性实施例中,所述第一子控制电路和所述第二子控制电路均包括第七晶体管,所述第一子控制电路中的所述第七晶体管的第一极和栅极均连接第一电源端、第二极连接所述第一子控制节点,用于响应所述第一电压信号将所述第一电源信号传输至所述第一子控制节点;所述第二子控制电路中的所述第七晶体管的第一极和栅极均连接所述第二电源端、第二极连接所述第二子控制节点,用于响应所述第二电压信号将所述第二电压信号传输至所述第二子控制节点;所述输入电路包括第五晶体管,所述第五晶体管的第一极和栅极均连接所述输入控制端、第二极连接所述第二控制节点,所述第五晶体管用于响应所述输入控制端提供的输入控制信号将所述输入控制信号传输至所述第二控制节点;所述第一重置电路包括第四晶体管,所述第四晶体管的第一极连接所述第二控制节点、第二极接收所述第一电平信号、栅极连接所述第一重置控制端,用于响应所述第一重置控制端的信号将所述第一电平信号传输至所述第二控制节点重置所述第二控制节点;所述第二重置电路包括第六晶体管,所述第六晶体管的第一极连接所述第二控制节点、第二极接收所述第一电平信号、栅极连接所述第二重置控制端,用于响应所述第二重置控制端的信号将所述第一电平信号传输至所述第二控制节点以重置所述第二控制节点;所述第一子重置电路和所述第二子重置电路均包括第八晶体管,所述第一子重置电路中的第八晶体管的第一极连接所述第一子控制节点、第二极接收所述第一电平信号、栅极连接所述第二控制节点,用于响应第二控制节点的信号利用所述第一电平信号重置所述第一子控制节点;所述第二子重置电路中的第八晶体管连接的第一极连接所述第二子控制节点、第二极接收所述第一电平信号、栅极连接所述第二控制节点,用于响应所述第二控制节点的信号利用所述第一电平信号重置所述第二子控制节点;所述第三子重置电路和所述第四子重置电路均包括第十三晶体管,所述第三子重置电路中的第十三晶体管的第一极连接所述第二控制节点、第二极接收所述第一电平信号、栅极连接所述输入信号端,用于响应所述输入信号端的信号利用所述第一电平信号重置所述第一子控制节点;所述第四子重置电路中的第十三晶体管的第一极连接第二子控制节点、第二极接收所述第一电平信号、栅极连接所述输入信号端,用于响应所述输入信号端的信号利用所述第一电平信号重置所述第二子控制节点;所述感测电路包括第一晶体管、第二晶体管和第一电容,所述第一晶体管的第一极连接所述第二感测控制端、第二极连接所述预存节点、栅极连接所述第一感测控制端,所述第一晶体管用于响应所述第一感测控制端的信号将所述第二感测信号端的信号传输至所述预存节点;所述第一电容用于存储所述预存节点的电压信号;所述第二晶体管的第一极接收所述第一时钟信号、第二极连接所述公共节点、栅极连接所述预存节点,所述第二晶体管用于响应所述预存节点的信号将所述第一时钟信号传输至所述公共节点;所述隔离电路包括第三晶体管,所述第三晶体管的第一极连接所述公共节点、第二极连接所述第二控制节点、栅极接收所述第一时钟信号,所述第三晶体管用于响应所述第一时钟信号将所述公共节点的信号传输至所述第二控制节点;所述第一子复位电路和所述第二子复位电路均包括第十一晶体管和第十二晶体管,所述第一子复位电路中的所述第十一晶体管的第一极连接所述第一子控制节点、第二极连接对应所述第十二晶体管的第一极、栅极接收所述第一时钟信号,用于响应所述第一时钟信号导通第一极和第二极;所述第一子复位电路中的所述第十二晶体管的第二极接收所述第一电平信号、栅极连接所述预存节点,用于响应所述预存节点的信号将所述第一电平信号传输至与其连接所述第十一晶体管的第二极,所述第一子复位电路中的所述第十一晶体管还用于利用所述第一电平信号复位所述第一子控制节点;所述第二子复位电路中的所述第十一晶体管的第一极连接所述第二子控制节点、第二极连接对应所述第十二晶体管的第一极、栅极接收所述第一时钟信号,用于响应所述第一时钟信号导通第一极和第二极;所述第二子复位电路中的所述第十二晶体管的第二极接收所述第一电平信号、栅极连接所述预存节点,用于响应所述预存节点的信号将所述第一电平信号传输至与其连接所述第十一晶体管的第二极,所述第二子复位电路中的所述第十一晶体管还用于利用所述第一电平信号复位所述第二子控制节点。

21、在本公开的示例性实施例中,所述第一晶体管~所述第八晶体管、所述第十三晶体管、所述第十一晶体管和所述第十二晶体管均为n型晶体管。

22、根据本公开的第二方面,还提供一种移位寄存器的驱动方法,用于驱动本公开任意实施例所述的移位寄存器,所述方法包括:在显示阶段,控制所述第一节点控制电路利用所述第一电平信号复位所述第二控制节点;在非显示阶段,利用所述第一控制信号端提供的控制信号控制所述补偿电路将所述第三电平信号传输至补偿节点,并利用所述补偿节点的第三电平信号控制所述第一节点控制电路中的晶体管反向偏置。

23、在本公开的示例性实施例中,所述方法包括:在所述第一子节点控制电路导通阶段利用所述第一子控制节点的信号控制所述第一补偿电路导通以向所述第一补偿节点提供第三电平信号,并利用所述第一补偿节点的第三电平信号控制所述第二子节点控制电路中的晶体管反向偏置;在所述第二子节点控制电路导通阶段利用所述第二子控制节点的信号控制所述第二补偿电路导通以向所述第二补偿节点提供所述第三电平信号,并利用所述第二补偿节点的第三电平信号控制所述第一子节点控制电路中的晶体管反向偏置。

24、根据本公开的第三方面,还提供一种显示面板,包括栅极驱动电路,所述栅极驱动电路包括本公开任意实施例所述的移位寄存器。本公开提供的移位寄存器单元,包括了补偿电路,补偿电路可以向补偿节点写入第三电平信号,补偿节点的第三电平信号可以控制第一节点控制电路中的晶体管反向偏置,使得第一节点控制电路中晶体管的阈值电压得以反向漂移,从而可以减小第一节点控制电路中晶体管的阈值电压漂移速度,解决移位寄存器单元因为节点控制电路中晶体管的阈值电压正偏太大而导致电路失效的问题。

25、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184094.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表