用于检测电子存储器中的错误的方法与流程

- 国知局

- 2024-07-31 19:54:32

本发明涉及电子存储器中的读取和写入故障的检测,更具体地,涉及非易失性半导体存储器中的读取和写入故障的检测。

背景技术:

1、经常将临时故障注入集成电路用于攻击集成电路和安全系统。通过借助光电效应在pn结或晶体管沟道中产生瞬态电流,脉冲激光器提供了一种方便且易于控制的注入此类故障的方式。

2、文献中已经报道了许多类型的对抗这些激光攻击的对策,即物理屏障(例如,金属屏蔽)、具有小敏感体积的器件架构(例如,绝缘体上的硅完全耗尽:fd-soi)、用于检测损坏电路故障的硬件冗余、以及加扰和加密技术。

3、这些方法有缺点和/或弱点。

4、屏蔽方法可能与集成电路制造限制(如金属密度规则)不兼容,或者可能限制性能。具有固有低光子灵敏度的器件通常会损害器件性能的其他方面,并且在任何情况下都可能由于增加入射光强度被击败。硬件冗余虽然有效,但需要重复的电路功能,在硅占用空间方面成本高昂,并且可能会通过使用以相同方式影响冗余路径的攻击而被绕过。加扰和加密可以通过逆向工程来阻止。

5、colombier等人的出版物“laser-induced single bit faults in flashmemory:instructions corruption on a 32-bit microcontroller”,garb等人的出版物“temporary laser fault injection into flash memory:calibration,enhancedattacks,and countermeasures”,menu等人的出版物“single-bit laser fault model innor flash memories:analysis and exploitation”,sakamoto等人的出版物“laser-induced controllable instruction replacement fault attack”和viera等人的出版物“permanent laser fault injection into the flash memory of a microcontroller”公开了基于将故障注入存储器的攻击和某些对抗它们的技术。

技术实现思路

1、仍然需要进一步改进用于检测存储器中的故障的方法,特别是在有效性、实用性、可靠性和成本方面。

2、本发明旨在满足这一目的,并根据其一个方面,本发明涉及一种用于检测非易失性半导体存储器中由光电或辐射效应引起的至少一个故障的方法,该存储器特别是nor闪存、eeprom或rom,该存储器包括多个存储单元,多个存储单元包含mos晶体管、可能地包含浮动栅极mos晶体管,每个存储单元位于基本位线和相关联字线的交叉点处,

3、在通过相关联的基本位线和字线选择了存储单元之后,通过检测在读取期间流过该存储单元的读取电流来读取该存储单元的二进制内容,

4、在该方法中,为了在一个或多个存储单元的读取期间检测至少一个故障的可能存在,在流过所述一个或多个相关联的基本位线的总电流与表示在这一个或多个存储单元中存在至少一个故障的预定阈值之间进行比较。

5、特别地,根据本发明的一个方面,本发明涉及一种用于检测由非易失性半导体存储器中的光电或辐射效应引起的至少一个故障的方法,该存储器特别是nor闪存、eeprom或rom,该存储器包括多个存储单元,多个存储单元包含mos晶体管、可能地包含浮动栅极mos晶体管,每个存储单元位于基本位线和字线的交叉点处,

6、在该方法中:

7、-为了在存储单元的读取期间检测至少一个故障的可能存在,在通过基本位线和字线选择了存储单元之后,通过检测在读取期间流过该存储单元的读取电流来读取该存储单元的二进制内容,

8、在流过被读取的存储单元所属的基本位线的总电流或者流过除了被读取的存储单元所属的基本位线之外的至少一条基本位线的总电流与表示在除了被读取的存储单元之外的一个或多个存储单元中存在至少一个故障的预定阈值之间进行比较,和/或

9、-为了在至少一个存储单元的编程期间检测至少一个故障的可能存在,特别是当该至少一个存储单元是nor闪存或eeprom时,在流过除了被编程的存储单元所属的基本位线之外的至少一条基本位线的电流与表示该线中存在至少一个故障的预定阈值之间进行比较。

10、编程,也称为写入,包括将电子存储在闪存的浮动栅极晶体管或eeprom存储单元的浮动栅极状态晶体管的浮动栅极中。

11、本发明使得能够获得一种用于检测读取或写入故障的方法,该方法是可靠的并且实现起来相对简单。

12、根据本发明的方法允许将程序写入存储器或写入数据的过程得到保护。

13、读取或写入故障

14、读取或写入故障会影响程序指令的字或程序使用的数据的字,该指令或数据存储在存储器中。

15、这种故障可能是由于将集成电路暴露于用于攻击目的的激光脉冲而产生的。激光脉冲的参数被选择为通过光电效应电离半导体材料,并导致在mos晶体管(可能地是浮动栅极mos晶体管)的漏极和衬底之间出现瞬态光电电流。在读取操作的情况下,该电流导致读取字的一个或多个位被错误地读取。在写入操作的情况下,该电流导致写入字的一个或多个位被错误地编程。

16、故障也可能是由于暴露于电离辐射而产生,无论是出于攻击目的故意的,还是出于偶然,例如当存储器暴露于发射电离粒子(重离子或质子、中子、x射线和伽马射线)的辐射源时。

17、干扰电流,无论是通过电离粒子还是通过光电效应产生的,都将在下面表示为iph。

18、在读取故障的情况下,该故障通常是暂时的,并且在排出感应电荷后停止。

19、该故障可能同时影响一个或多个存储单元。

20、将注意到,该故障不会改变存储在受读取故障影响的存储单元中的二进制值,而是导致读取的二进制值的暂时损坏。在写入故障的情况下,损坏的值存储在受写入故障影响的存储单元中。这种损坏是暂时的,并且可以通过在下一次对存储单元编程时写入正确的值来校正。

21、根据本发明的检测方法优选在存储单元的读取或编程期间被激活。根据本发明的检测方法也可以在所述存储单元的读取或编程之前和/或之后被激活。

22、预定阈值

23、预定阈值当其是电流时,也称为警报电流。

24、预定阈值是根据检测电路的架构来选择的,并且可以对应于根据情况低于或高于在没有故障的情况下正常观察到的读取电流的电流,例如基本上等于在本发明的某些示例中正常观察到的读取电流的强度的两倍。与之进行比较的电流可以流过与被选择用于读取的基本位线相同的基本位线上,或者流过至少一条其他线,特别是相邻线,如下所述。

25、执行检测的基本位线

26、在检测读取故障的情况下,执行故障检测的所述至少一条基本位线可以是与被读取的存储单元相关联的基本位线。

27、执行故障检测的所述至少一条基本位线可以与被读取或被编程的存储单元相关联的基本位线相邻。

28、故障检测可以通过与被读取或被编程的存储单元相关联的线相邻的单条线来执行。

29、故障检测可以通过与被读取或被编程的存储单元相关联的基本位线两侧的两条线来执行。

30、执行故障检测的所述至少一条基本位线可以属于与被读取或被编程的存储单元相同的块;块通常被定义为基本位线的集合,其中只有一条基本位线被选择以被读取或编程。

31、执行故障检测的所述至少一条基本位线可以属于在包括被读取或被编程的存储单元的块之后或之前的块;这些块通常位于存储器的邻近位置。

32、错误检测可以通过可能受到影响的一条或多条基本位线来执行,这些基本位线可以相对远离被读取或被编程的存储单元,并且不一定与被读取或被编程的存储单元相关联的线相邻。优选通过位于被读取或被编程的存储单元附近的一条或多条线、特别是相邻线进行错误检测。

33、可以在干扰机制的影响区域,即,感应的干扰电流高到足以产生故障的区域中执行检测。该区域可以在多条线上延伸和/或涉及影响区域中每条线的多个晶体管(或存储单元)。

34、通过分割字线进行错误检测

35、在一些实施示例中,存储器包括分割字线,每对(索引p)字线具有偶数索引2k的字线和奇数索引2k+1的字线,存储单元的晶体管的栅极交替地连接到偶数索引的字线以及奇数索引的相应字线,至少一对字线中的一条线升高到读取电位或写入电位以激活与其连接的存储单元,其另一条线升高到去激活与其连接的存储单元的电位,以便激活每隔一条基本位线的被读取的存储单元或对每隔一条基本位线编程,并且在与被读取或被编程的存储单元相关联的基本位线相邻的所述至少一条基本位线中执行故障检测。因此,与被读取或被编程的存储单元相关联的基本位线相邻的所述至少一条基本位线是电隔离的,并且因此仅在激光攻击或辐射事件的情况下通过电流。因此,可以将警报电流的阈值设置为低于相邻的基本位线也通过读取电流的情况。特别地,在这种情况下,预定阈值可以被设置为低于正常观察到的读取电流的大小的两倍。

36、通过修改晶体管源极的连接进行错误检测

37、在一些实施示例中,至少在相应存储单元的读取或编程期间,与每条基本位线相关联的晶体管的源极连接到升高到给定电位、特别是地的相应公共线,并且至少在故障检测期间,与所述至少一条相邻的基本位线相关联的晶体管的源极与所述给定电位、特别是与地电隔离。因此,所述至少一个相邻的基本位线不具有到所述给定电位的电连接路径,因此其仅在激光攻击或辐射事件的情况下通过电流。因此,可以将警报电流的阈值设置为低于相邻的基本位线也通过读取电流的情况。同样在这种情况下,预定义阈值可以设置为低于正常观察到的读取电流的大小的两倍。

38、术语“电隔离”当被应用于基本位线时,必须理解为指源极所连接的公共线不再允许在读取期间正常观察到的电流流动,因此,如果在受扰动影响的一个或多个晶体管的漏极和衬底之间观察到除了光电或辐射电流之外的任何电流的话,该电流将不会流过该基本位线。使晶体管的源极偏置的所述给定电位可以根据存储器的类型来选择,其等于给定电压v,通常为0v(电接地)。

39、重复读取字或写入字

40、在检测到基本位线上的读取故障的情况下,只要在该线上仍然检测到故障,则优选地将该线的读取重复预定次数。

41、当在存储器中对字进行编程时检测到故障的情况下,只要仍然检测到故障,就重复该字的编程预定次数。

42、如果在检测循环结束之前停止检测到故障,则可以恢复存储单元的读取或编程,该故障暂时影响存储器的读取或编程。如果在检测循环结束时仍检测到故障,则可以执行预定动作——例如,可以使使用存储器的程序变得安全,或者可以使用冗余安全电路。

43、在故障检测的情况下,可以生成信号以警告用户,例如警告用户试图破坏存储器或存在干扰。

44、故障检测方法可以借助于存储器芯片内存在的一个或多个专用电路来自主地实施;作为变型,该方法借助于存储器芯片外部的一个或多个电路来实施。

45、其上执行检测的存储器可以具有任何容量,例如大于或等于512mb的容量。

46、存储器电路

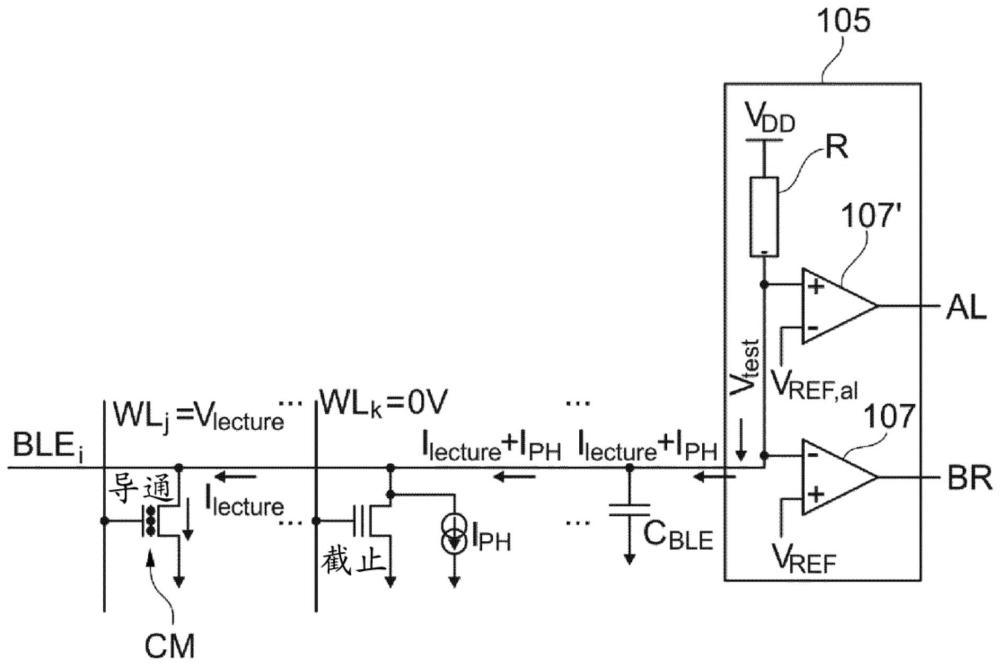

47、根据其另一个方面,本发明还涉及一种允许实施上面所述的检测方法的非易失性半导体存储器电路,特别是nor闪存电路、eeprom存储器电路或rom存储器电路;因此,该存储器电路可以被配置为检测由光电或辐射效应引起的至少一个故障的可能存在,并且包括多个存储单元,多个存储单元包含mos晶体管、可能地包含浮动栅极mos晶体管,每个存储单元位于基本位线和相关联字线的交叉点处,在通过相关联的基本位线和字线选择了存储单元之后,通过检测在读取期间流过该存储单元的读取电流来读取该存储单元的二进制内容,该存储器电路包括至少一个警报电路,该警报电路的输入端连接到执行故障检测的至少一条基本位线,该警报电路具有输出端并且被配置为在检测期间在流过所述一条或多条相关联的基本位线的总电流与表示在这一个或多个存储单元中存在至少一个故障的预定阈值之间进行比较;警报电路的输出端的状态指示所述至少一个故障是否存在。

48、特别地,根据其另一个方面,本发明的又一主题是一种允许实现上面所述的检测方法的非易失性半导体存储器电路,特别是nor闪存电路、eeprom存储器电路或rom存储器电路;因此,该存储器电路可以被配置为检测由光电或辐射效应引起的至少一个故障的可能存在,并且包括多个存储单元,多个存储单元包含mos晶体管、可能地包含浮动栅极mos晶体管,每个存储单元位于基本位线和字线的交叉点处,该存储器电路包括至少一个警报电路,该警报电路的输入端连接到执行故障检测的至少一条基本位线,该警报电路具有输出端,该输出端的状态指示所述至少一个故障是否存在,该警报电路被配置为:

49、-通过在流过执行故障检测的所述至少一条基本位线的总电流与表示在除了被读取的存储单元之外的一个或多个存储单元中存在至少一个故障的预定阈值之间进行比较,在存储单元的读取期间检测至少一个故障的可能存在,在通过基本位线和字线选择了存储单元之后,通过检测在读取期间流过该存储单元的读取电流来读取该存储单元的二进制内容,和/或

50、-在对至少一个存储单元进行编程期间,特别是当至少一个存储单元是nor闪存或eeprom时,通过在流过除了被编程的存储单元所属的基本位线之外的至少一条基本位线的电流与表示该线中存在至少一个故障的预定阈值之间进行比较,检测至少一个故障的可能存在。

51、这样的存储器电路可以封装在存储器芯片或微控制器芯片或任何其他微处理器电路内。

52、本发明可应用于许多类型的存储器。

53、nor闪存

54、在nor闪存的情况下,每个存储单元可以包括浮动栅极mos晶体管,其控制栅极连接到相应的字线,并且其漏极连接到相应的基本位线。

55、eeprom

56、在eeprom的情况下,每个存储单元可以包括串联的两个晶体管:mos选择晶体管和浮动栅极状态晶体管,选择晶体管的栅极连接到与所述单元相关联的字线,选择晶体管的漏极连接到与所述单元相关联的基元位线,所述状态晶体管的控制栅极连接到偏置电压,所述偏置电压特别是读取模式下的电源电压或是接地。

57、eeprom可以包括地址解码器,该地址解码器针对每条基本位线将偏置电压传输到状态晶体管的控制栅极。这允许与包含被读取的存储单元的线相邻的基本位线的晶体管的源极与地电隔离。因此,与包含被读取的单元的基本位线相邻的基本位线没有到地的电连接路径,因此它们仅在激光攻击或辐射事件的情况下通过电流。因此,可以将警报电流的阈值设置为低于相邻的基本位线也通过读取电流的情况。

58、rom

59、在rom的情况下,每个存储单元可以包括mos晶体管,其栅极连接到相关联的字线,其漏极连接到相关联的基本位线,存储器电路包括连接到每条基本位线的读取器件,读取器件包括mos上拉晶体管。

60、作为变型,至少在相应存储单元的读取期间,与每条基本位线相关联的mos晶体管的源极连接到升高到给定电位、特别是接地的相应的公共线,并且至少在故障检测期间,与至少一条相邻的基本位线相关联的晶体管的源极与所述给定电位、特别是与地电隔离。

61、列解码器

62、存储器电路优选地包括列解码器,该列解码器包括连接到每条基本位线的选择晶体管以对基本位线进行选择,并且对于执行故障检测的每条基本位线,包括与选择晶体管并联连接的警报晶体管,该警报晶体管连接到所述至少一个警报电路。

63、警报电路

64、优选地,警报电路包括至少一个检测电路,该检测电路包括电压比较器,该电压比较器具有连接到基准电压的第一输入端和连接到执行故障检测的基本位线的警报晶体管的第二输入端,当第二输入端上的电压低于基准电压时检测到故障,所述警报晶体管在故障检测期间导通。

65、在rom的情况下,所述至少一个检测电路可以与读取器件分离。

66、在rom的情况下,并且对于与每条基本位线相关联的mos晶体管的源极连接到升高到给定电位的相应公共线的变型,警报电路优选地包括读取器件,特别是没有任何单独的附加检测电路。具体地,rom中晶体管的源极的这种配置使得能够不必添加任何单独的检测电路,因为通过使用相邻基本位线的读取器件检测相邻基本位线上的电流来触发警报,该器件的输出能够生成警报位。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184647.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表