输入权重比特位可配置的存内计算电路及其芯片

- 国知局

- 2024-07-31 20:11:57

本发明属于集成电路,具体涉及一种输入权重比特位可配置的存内计算电路,以及对应的cim芯片。

背景技术:

1、随着人工智能的快速发展和普及,卷积神经网络(cnn)和深度神经网络(dnn)已经成为计算机视觉领域最具影响力的创新之一。cnn和dnn等神经网络进行数据处理上需要进行大量的乘法和乘累加(mac)运算,这种运算在基于冯诺依曼架构的计算机中进行处理时。由于需要在处理器和存储器间频率搬运数据,因而造成了较高的能量消耗和延迟,这个问题被称为冯诺依曼瓶颈或内存墙。基于冯诺依曼架构的dnn处理器和加速器的演示表明,能量消耗和延迟主要取决于处理器和存储器之间输入数据。因此,传统的冯诺依曼计算机并不适合处理神经网络等人工智能相关的计算任务。

2、为了克服冯诺依曼瓶颈,技术人员提出一种基于存储器的存内运算(cim)架构,这种计算机架构直接利用存储器来实现逻辑运算,无需在存储器和处理器进行数据搬运,因而可以大幅提高数据处理效率降低设备功耗。

3、卷积神经网络中包含大量带符号的乘法与乘累加操作。既有的多位权重cim电路实现该类正权重和负权重的运算任务时主要有两个特点:一是分离的正负权重放置。在分离的正负权重放置中,正负权重放在单独的列中,因而需要2k个sram单元来存储有符号的k位权重,这增加了面积开销并降低了推理速度。二是具有近存储器mac操作的存储器内权重处理。在具有近存储器mac操作的存储器内权重处理中,则需要将多个脉宽调制wl应用于k个sram单元,进而将带符号的k位数字权重转换为用于在近存储器电路中计算的mac操作的模拟值;这种对运算数据进行特殊编码和模数转换的过程会显著增加电路运算过程的延迟、面积开销和整体功耗。

技术实现思路

1、为了解决现有各类具有带符号乘法与乘累加运算功能的cim电路普遍存在的面积开销大,运算效率低、延迟和功耗较高的问题,本发明提供一种输入权重比特位可配置的存内计算电路及其芯片。

2、本发明提供的技术方案为:

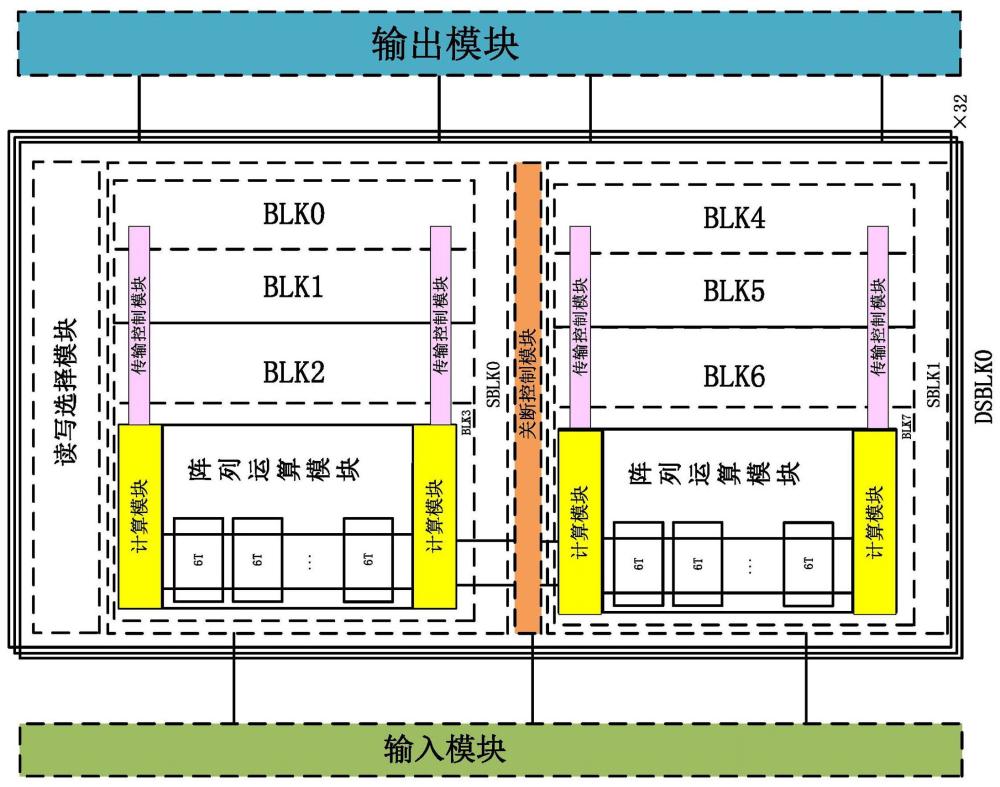

3、一种输入权重比特位可配置的存内计算电路,按照功能划分,该存内计算电路中包括:sram阵列、外围电路、关断控制模块、多个计算模块、传输控制模块、输入模块,以及输出模块。其中,sram阵列与外围电路配合能够实现sram电路的数据存储功能,而sram阵列配合其余各部分则可以实现多比特的带符号数和无符号数间的乘法运算。

4、在本发明的存内计算电路中,sram阵列中位于同一行的各个sram单元两侧的传输管连接在同一组字线wll和wlr上。sram阵列一方面配合外围电路实现对数据的读、写、保持操作;另一方面则将自身包含的各个sram单元用于存储乘法运算中无符号数的其中一个bit位。

5、关断控制模块包括多个传输门,各个传输门用于打断sram阵列的位线bl和blb;进而将sram阵列划分成以n行单列的sram单元为一个基本单元的多个部分。sram阵列中每个基本单元与至少一个计算模块连接,进而构成一个blk。

6、blk中的每个计算模块包括两个nmos管n3、n4,两个pmos管p1、p2,以及一个电容c。电路连接关系为:p1和n3的漏极连接在计算位线cbl上;n3的栅极接位线bl,p1的栅极接位线blb; n3的源极与n4的漏极相连;p1的源极与p2的漏极相连;n4的栅极接输入字线inn;p2的栅极接输入字线inp;n4的源极接vss;p2的源极接vdd;电容c的一端连接在计算位线cbl上,另一端接vss;位于同一行的各个计算模块共享同一条计算位线cbl以及输入字线inn和inp;

7、传输控制模块由多个传输门构成;每个传输门用于管理相邻两个计算模块间的计算位线cbl的连通状态,进而在不同列上通过电荷共享的方式实现对乘法运算中无符号数的各位进行权重配置;

8、输入模块包括输入编码单元、关断管理单元、传输管理单元和预充电单元。其中,输入编码单元与每一行的各个计算模块相连;输入编码单元用于管理字线wll、wlr以及输入字线inn和inp的电平状态,进而输入由wll、wlr、inn和inp的电平状态表征的乘法运算的带符号数。关断管理单元用于产生输入到关断控制模块中的各个传输门的使能信号。传输管理单元则用于产生输入到传输控制模块中的各个传输门的使能信号。预充电单元用于在执行逻辑运算任务时将计算位线cbl预充到指定电位。

9、输出模块包括adc单元、移位器和加法器。adc单元的输入端连接各行的计算位线cbl和参考电平,并用于输出根据cbl的电平状态量化出的乘法运算结果。加法器和移位器共同实现对乘法运算中带符号数的各位进行权重配置。

10、作为本发明进一步的改进,sram单元采用6t-sram单元或其它具有双字线的sram单元;

11、6t-sram单元包括两个nmos管n1、n2,以及两个反相器inv0、inv1。电路连接关系如下:inv0的输入端、inv1的输出端与n1的源极相连,并作为存储节点q。inv0的输出端、inv1的输入端与n2的源极相连,并作为存储节点qb。n1、n2的漏极分别连接在位线bl和blb上,n1、n2的栅极分别连接字线wll、wlr。

12、作为本发明进一步的改进,每个blk中包含两个计算模块,其中一个计算模块连接在当前列中的位线bl和blb的上方,另一个计算模块连接在当前列中的位线bl和blb的下方。

13、作为本发明进一步的改进,位于相邻列的m个blk构成了一个sblk。在同一个sblk中,各个blk的计算模块上挂载的电容c的电容值按照1、2、4、8、…、2m-1的倍率进行配置;各个blk挂载的电容的电容值倍率即为sblk中各个blk执行乘法运算时的位权重。

14、作为本发明进一步的改进,每个blk作为执行2bit带符号数与1bit无符号数间乘法运算的操作对象,操作逻辑如下:

15、(1)将1bit无符号数预先存储blk中指定的sram单元中,并将计算位线cbl预充到vss与vdd的中间电位。

16、(2)将wll、wlr、inn和inp置为指定的电平状态,进而实现向blk中输入对应的2bit带符号数。

17、(3)对计算结束后的计算位线cbl的电平状态进行量化,得到乘法运算的结果:

18、其中,当计算位线cbl的位线电压上升,则表示乘积为“+1”;当计算位线cbl的位线电压下降,则表示乘积为“-1”;当计算位线cbl的位线电压保持不变,则表示乘积为“0”。

19、在本发明中,将wll、inn和inp置低电平,wlr置高电平时,表征输入的乘法运算中的带符号数为“+1”。将wll、inn和inp置高电平,wlr置低电平,表征输入的乘法运算中的带符号数为“-1”。将wll和inn置低电平,wlr和inp置高电平,表征输入的乘法运算中的带符号数为“0”。

20、作为本发明进一步的改进,每个sblk配合传输控制模块共同构成执行2bit带符号数与mbit无符号数间乘法运算的操作对象,操作逻辑如下:

21、(1)将各列的计算位线cbl预充到vdd和vss的中间电位,然后断开传输控制模块中位于各blk间的传输门。

22、(2)将mbit的无符号数按位分解为n个单比特数,并将各个单比特数按对应位权重预存到各个blk中指定的sram单元中。

23、(3)将wll、wlr、inn和inp置为指定的电平状态,进而实现向blk中输入对应的2bit带符号数;2bit带符号数与mbit无符号数各位上的乘积体现在每个blk中cbl的位线电压上。

24、(4)将传输控制模块中位于各blk间的传输门闭合,不同blk的cbl相互连通并实现电荷共享,此时,2bit带符号数与mbit无符号数的乘积体现在计算位线cbl的位线电压的变化上。具体的,cbl的位线电压的变化方向反映乘积的符号,cbl的变化幅度则反映乘积的数值大小。

25、作为本发明进一步的改进,多个sblk配合关断控制模块、传输控制模块、移位器和全加器共同构成4bit以上带符号数与mbit无符号数乘法运算的操作对象,操作逻辑为:

26、(1)将带符号数中的数值部分逐位分解为多个单比特数,并将单比特数与原符号位组合,构成多个2bit带符号数。

27、(2)利用关断控制模块将同列中各个sblk隔离开;并由隔离后的每个sblk配合传输控制模块完成各个2bit带符号数与mbit无符号数间的乘法运算,得到对应的多个乘积结果。

28、(3)采用移位器根据2bit带符号数的数值部分在原多比特带符号数中的位权重,对各个乘积结果进行移位,然后在将移位后的乘积结果通过加法器进行加和,最终得到4bit以上带符号数与mbit无符号数的乘积。

29、作为本发明进一步的改进,每个sblk配合传输控制模块至多能够完成两个2bit带符号数与mbit无符号数乘法的运算任务,其中,每个blk中的其中一行sram单元配合上方的计算模块完成其中一个运算任务;另外一行sram单元配合下方的计算模块完成另一个运算任务。

30、本发明还包括一种cim芯片,其由如前述的输入权重比特位可配置的存内计算电路封装而成。

31、本发明提供的技术方案,具有如下有益效果:

32、本发明基于双字线的sram单元设计了一种带符号乘法的存内计算电路,该电路将1bit权重存储在sram单元内, 2bit带符号数分为1bit符号位和1bit无符号数两部分、1bit符号位通过控制双字线wll和wlr的高低电平表示,1bit无符号数结合新增的计算部分的输入字线inn和inp进行控制。在电路中,根据表征权重和带符号数中各个信号的不同取值,可以控制计算字线cbl相对电源和地的充放电路径的导通,进而通过cbl的位点电压变化表征最终的乘积结果。

33、本发明通过同一个sblk上的不同blk的计算位线cbl上配置不同大小的电容,并对各个blk上的计算位线cbl通过传输控制模块进行打断控制。利用这种特殊的电路设计,可以通过电荷共享的方式在不同blk上实现不同的位权重,无需借助其他外围电路就可以实现2bit带符号数与多bit无符号数的乘法运算,整个计算的宏电路设计精巧,运算时间短、运算效率高。

34、在2bit带符号数与多bit无符号数乘法基础上,本发明的电路还借助移位器和加法器实现了多bit待符号数与多bit无符号数乘法,以及上述各种乘法对应的mac运算,该存内计算电路的性能强大,面积开销较小,集成度高。另外,由于本发明电路在各类运算中无需借助外围电路进行无符号数的位权重处理,因此运算效率更高,也可以改善电路运算过程的延迟和功耗。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185400.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表