数字存内计算宏的测试方法、装置和芯片与流程

- 国知局

- 2024-07-31 20:13:03

本公开涉及测试,尤其是一种数字存内计算宏的测试方法、装置和芯片。

背景技术:

1、内存内计算(cim,computing in memory)是一种可以打破冯诺依曼架构存储墙瓶颈的有效方法。内存内计算的架构是通过在存储器中嵌入计算逻辑来减少cpu和存储器之间的数据搬移。

2、目前存内计算宏(cim macro)的实现方式可以分为基于静态随机存取存储器(static random-access memory,sram)的数字方式、基于sram的模拟方式、基于新型存储器件(例如非易失性的磁性随机存储器或阻变式存储器)的方式等。其中基于sram的数字存内计算宏(cimd macro)具有访问速度快、计算精度高、能效比高、稳定性好、易于设计和生产制造的优点,比较适合应用在大算力、低功耗的大型ai芯片设计中。

3、如何对cimd macro进行有效的测试,是一个亟待解决的问题。

技术实现思路

1、本公开实施例提供一种数字存内计算宏的测试方法、装置和芯片,可以对cimdmacro进行有效的测试。

2、本公开实施例的第一方面,提供一种数字存内计算宏的测试方法,包括:

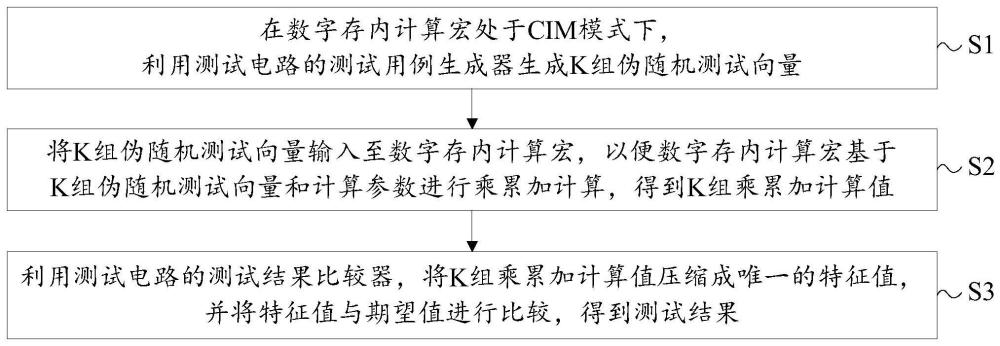

3、在数字存内计算宏处于内存内计算cim模式下,利用测试电路的测试向量生成器生成k组伪随机测试向量,其中,k为大于1的整数;

4、将所述k组伪随机测试向量输入至所述数字存内计算宏,以便所述数字存内计算宏基于所述k组伪随机测试向量和计算参数进行乘累加计算,得到k组乘累加计算值;

5、利用所述测试电路的测试结果比较器,将所述k组乘累加计算值压缩成唯一的特征值,并将所述特征值与期望值进行比较,得到测试结果。

6、在本公开的一个实施例中,在所述在数字存内计算宏处于内存内计算模式下,利用测试电路的测试向量生成器生成k组伪随机测试向量之前,还包括:

7、响应于所述测试电路接收到内建自测试指令,控制所述数字存内计算宏进入静态随机存取存储器sram模式,对所述数字存内计算宏进行全地址写遍历,在全地址内写入所述计算参数;

8、利用所述测试电路对所述数字存内计算宏进行全地址读遍历,得到读取值;

9、基于所述计算参数和所述读取值,确定所述计算参数的写入是否正确。

10、在本公开的一个实施例中,所述利用测试电路的测试向量生成器生成k组伪随机测试向量,包括:

11、响应于所述测试向量生成器接收到测试向量启动指令,所述测试向量生成器使用默认种子作为初始值生成k组伪随机测试向量,并将所述k组伪随机测试向量发送给线性移相器。

12、在本公开的一个实施例中,所述利用测试电路的测试向量生成器生成k组伪随机测试向量,包括:

13、利用所述测试访问端口控制器向测试数据寄存器发送种子数据,并将所述种子数据发送给新种子寄存器;

14、响应于所述测试向量生成器接收到测试向量启动指令,所述测试向量生成器利用所述默认种子或者所述新种子数据作为初始值生成k组伪随机测试向量。

15、在本公开的一个实施例中,所述测试向量生成器使用13阶外接型的最长线性移位寄存器m序列生成所述k组伪随机测试向量;所述m序列的特征多项式为x13+x4+x3+x+1;所述线性移相器设置在所述m序列的输出端和数据总线之间。

16、在本公开的一个实施例中,所述利用所述测试电路的测试结果比较器,将所述k组乘累加计算值压缩成唯一的特征值,并将所述特征值与期望值进行比较,得到测试结果,包括:

17、响应于接收到压缩启动信号,利用所述测试结果比较器的多输入特征寄存器将所述k组乘累加计算值压缩成所述特征值;

18、利用所述测试结果比较器的期望结果比较器对所述特征值和所述期望值进行比较,得到测试结果。

19、在本公开的一个实施例中,所述利用所述测试结果比较器的多输入特征寄存器将所述k组乘累加计算值压缩成所述特征值,包括:

20、将所述k组乘累加计算值并行输入给所述多输入特征寄存器的每一级寄存器单元,得到所述特征值。

21、本公开实施例的第二方面,提供一种数字存内计算宏的测试装置,包括:

22、测试向量生成模块,用于在数字存内计算宏处于内存内计算cim模式下,利用测试电路的测试向量生成器生成k组伪随机测试向量,其中,k为大于1的整数;

23、测试向量输入模块,用于将所述k组伪随机测试向量输入至所述数字存内计算宏,以便所述数字存内计算宏基于所述k组伪随机测试向量和计算参数进行乘累加计算,得到k组乘累加计算值;

24、测试比较模块,用于利用所述测试电路的测试结果比较器,将所述k组乘累加计算值压缩成唯一的特征值,并将所述特征值与期望值进行比较,得到测试结果。

25、在本公开的一个实施例中,所述数字存内计算宏的测试装置还包括权值验证模块,所述权值验证模块用于响应于所述测试电路接收到内建自测试指令,控制所述数字存内计算宏进入静态随机存取存储器sram模式,对所述数字存内计算宏进行全地址写遍历,在全地址内写入所述计算参数;所述权值验证模块还用于利用所述测试电路对所述数字存内计算宏进行全地址读遍历,得到读取值;所述权值验证模块还用于基于所述计算参数和所述读取值,确定所述计算参数的写入是否正确。

26、在本公开的一个实施例中,所述测试向量生成模块用于响应于所述测试向量生成器接收到测试向量启动指令,所述测试向量生成器使用默认种子作为初始值生成k组伪随机测试向量,并将所述k组伪随机测试向量发送给线性移相器。

27、在本公开的一个实施例中,所述测试向量生成模块用于利用所述测试访问端口控制器向测试数据寄存器发送种子数据,并将所述种子数据发送给新种子寄存器;所述测试向量生成模块还用于响应于所述测试向量生成器接收到测试向量启动指令,所述测试向量生成器利用所述默认种子或者所述新种子数据作为初始值生成k组伪随机测试向量。

28、在本公开的一个实施例中,所述测试向量生成器使用13阶外接型的最长线性移位寄存器m序列生成所述k组伪随机测试向量;所述m序列的特征多项式为x13+x4+x3+x+1;所述线性移相器设置在所述m序列的输出端和数据总线之间。

29、在本公开的一个实施例中,所述测试比较模块用于响应于接收到压缩启动信号,利用所述测试结果比较器的多输入特征寄存器将所述k组乘累加计算值压缩成所述特征值;所述测试比较模块还用于利用所述测试结果比较器的期望结果比较器对所述特征值和所述期望值进行比较,将所述测试结果存入所述第一测试数据寄存器中。

30、在本公开的一个实施例中,所述测试比较模块用于将所述k组乘累加计算值并行输入给所述多输入特征寄存器的每一级寄存器单元,得到所述特征值。

31、本公开实施例的第三方面,提供一种芯片,包括上述第二方面所述的数字存内计算宏的测试装置。

32、本公开实施例的第四方面,提供一种电子设备,包括:

33、存储器,用于存储计算机程序;

34、处理器,用于执行所述存储器中存储的计算机程序,且所述计算机程序被执行时,实现上述第一方面所述的数字存内计算宏的测试方法。

35、本公开实施例的第五方面,提供一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时,实现上述第一方面所述的数字存内计算宏的测试方法。

36、本公开实施例的数字存内计算宏的测试方法、装置和芯片,在数字存内计算宏处于内存内计算cim模式下,利用测试电路的测试向量生成器生成k组伪随机测试向量;将所述k组伪随机测试向量输入至所述数字存内计算宏,以便所述数字存内计算宏基于所述k组伪随机测试向量和计算参数进行乘累加计算,得到k组乘累加计算值;利用所述测试电路的测试结果比较器,将所述k组乘累加计算值压缩成唯一的特征值,并将特征值与期望值进行比较,得到测试结果。本公开可以应用于人工智能的系统级芯片的可测性设计中,可以快速准确地确定数字存内计算宏是否进行了有效且准确的工作,具有成本低、测试速度快、测试覆盖率高和产品制造良率高的优点。

37、下面通过附图和实施例,对本公开的技术方案做进一步的详细描述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185467.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表