一种基于FPGA和TDC的高精度频率检测系统及方法

- 国知局

- 2024-09-05 14:22:10

本发明属于频率测试计数领域,涉及一种基于fpga和tdc的高精度频率测量系统及方法。

背景技术:

1、硅微谐振式加速度计是一种高精度的加速度传感器,在航空航天,导航与制导,消费电子,汽车电子领域起着重要作用。与其余类型的加速度计相比,谐振式加速度计具有更高精度潜力,因而在军事和民用领域具有重要应用价值。硅微谐振加速度计输出为两路频率信号,以频率信号表征加速度大小,通过测量谐振频率的变化可以得到加速度信息,所以对测频方法的精度有很高的要求。

2、在目前的频率采集方法中,常见的测频方法有模拟测频法和数字测频法,模拟测频法是通过将频率转化为电流或者电压信号来间接测量频率,由于其精度低,分辨率低,检测结构复杂,存在耦合的问题所以逐渐被淘汰。数字测频法是现在主要的研究方向。数字测频法可以利用数字芯片对多组数据同步进行测量,不需要额外的电路结构,易于调整,检测结果易于传输。在数字测频法中,应用最为广泛的是等精度测频法和多路移相时钟测频法。等精度测频法的优势在于方法简单,易于实现,且等精度测频法的测频误差与被测信号无关,仅仅与标准信号的频率和实际闸门的持续时间相关,因此广泛应用于低频测量和高频测量的领域中。但其缺陷在于被测信号与标准信号的频率不是同源信号,无法确定其相位关系,在开启和关闭实际闸门时,标准信号的上升沿无法与实际闸门的上升沿对齐,所以对标准信号的计数值会有±1的误差。多路移相时钟测频法其基本原理和等精度测频法类似,区别在于标准信号通过移相获得多组同源不同相的时钟。以一路标准信号为基准参考信号,对其进行0°、90°、180°、270°的移相得到四路标准信号,其上升沿依次相差了1/4个时钟周期,本质原理是将标准信号进行倍频操作以减小±1计数误差带来的影响,依旧无法消除误差影响。

技术实现思路

1、发明目的:为克服现有技术不足,提供一种基于fpga和tdc的高精度频率检测系统及方法,以实现消除等精度测频法中基准信号的±1误差,提高频率测量的精度。

2、技术方案:为解决上述技术问题,本发明采用如下技术方案:

3、一种基于fpga和tdc的高精度频率检测系统,包括fpga芯片和tdc芯片,所述fpga芯片产生预设闸门,通过预设闸门和被测信号控制实际闸门,在实际闸门时间内,对被测信号与标准信号进行计数,并与tdc芯片进行通信,在实际闸门关闭后,继续对标准信号进行计数并再次与tdc芯片通信。通过tdc芯片产生的输出信号与被测信号与基准信号的计数器值进行计算得到被测信号频率值。

4、所述检测方法步骤如下:

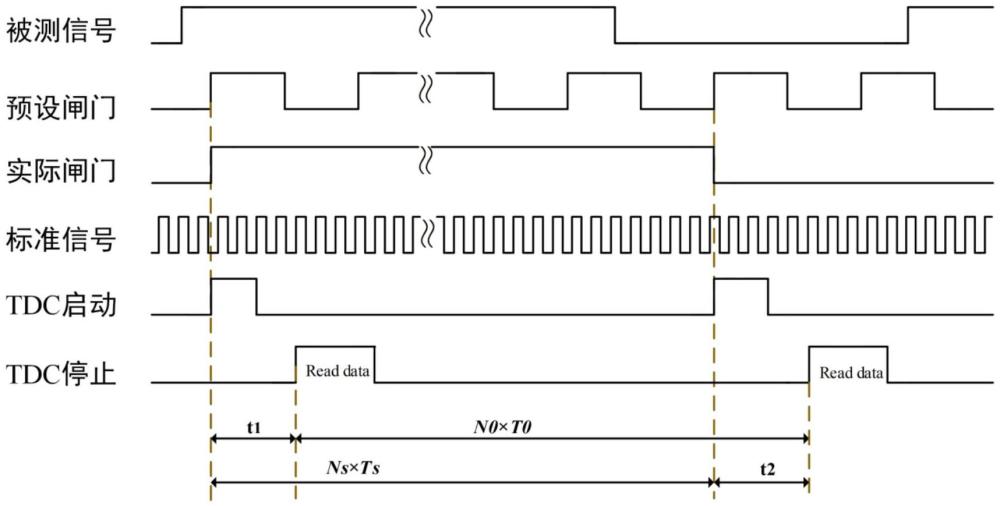

5、令基准信号周期为t0,被测信号周期为ts。当预设闸门打开后,被测信号的上升沿到达时,实际闸门打开,此时向tdc芯片发送启动脉冲,并对被测信号的上升沿开始计数,在经过n个标准信号上升沿后,对tdc芯片发出停止脉冲,获得测量结果t1,此时对标准时钟开始计数,当预设闸门关闭后,在被测信号的上升沿到达时,关闭实际闸门,再次开启tdc芯片,并对被测信号的计数停止,获得被测信号个数ns,经过n个标准信号上升沿后,关闭tdc芯片,获得测量结果t2,停止对标准信号计数,获得标准信号个数n0。n的选取和标准信号频率有关,在50mhz标准时钟下,设置为3。经过计算,被测信号频率可以表示为:

6、ns×ts=n0×t0+t1-t2。

7、与现有技术相比,本发明的有益效果在于:此发明保留了等精度测量法的优势,可以应用于低频测量于高频测量之中,同时可以消除等精度测频法中基准信号的±1计数误差,在理论推导上无测量误差,在实际应用中测量误差仅来自于tdc芯片的测量精度与fpga中定点数的运算误差,此方法极大提高了测频精度。

技术特征:1.一种基于fpga和tdc的高精度频率检测系统,其特征在于,包括fpga芯片和tdc芯片;所述fpga芯片用于产生预设闸门,并通过预设闸门和被测信号控制实际闸门,在实际闸门时间内,对被测信号与标准信号进行计数,并与tdc芯片进行通信,在实际闸门关闭后,继续对标准信号进行计数并再次与tdc芯片通信;通过tdc芯片产生的输出信号与被测信号与基准信号的计数器值进行计算得到被测信号频率值。

2.一种基于fpga和tdc的高精度频率检测方法,其特征在于,采用如权利要求1所述的系统,包括如下步骤:令基准信号周期为t0,被测信号周期为ts;当预设闸门打开后,被测信号的上升沿到达时,实际闸门打开,此时向tdc芯片发送启动脉冲,并对被测信号的上升沿开始计数,在经过n个标准信号上升沿后,对tdc芯片发出停止脉冲,获得测量结果t1,此时对标准时钟开始计数,当预设闸门关闭后,在被测信号的上升沿到达时,关闭实际闸门,再次开启tdc芯片,并对被测信号的计数停止,获得被测信号个数ns,经过n个标准信号上升沿后,关闭tdc芯片,获得测量结果t2,停止对标准信号计数,获得标准信号个数n0;n的选取和标准信号频率有关,在50mhz标准时钟下,设置为3;经过计算,被测信号频率表示为:

3.根据权利要求2所述的一种基于fpga和tdc的高精度频率检测方法,其特征在于,所述fpga芯片为5csxfc6c6u23i7n,tdc芯片为tdc-gp22,外接晶振、eeprom、电源、复位芯片,完成fpga最小系统设计,使fpga芯片能正常工作。

4.根据权利要求3所述的一种基于fpga和tdc的高精度频率检测方法,其特征在于,晶振电路产生50mhz的标准时钟信号,通过fpga芯片的i/o口输入至fpga芯片中作为一个基准信号,被测信号从fpga芯片的i/o口输入至fpga芯片中;在频率测量开始前,fpga芯片对tdc芯片进行初始化操作,利用spi通信协议,进行tdc芯片的寄存器配置,初始化完成后可以开始频率测量工作。

5.根据权利要求4所述的一种基于fpga和tdc的高精度频率检测方法,其特征在于,所述检测方法的具体步骤为:

技术总结本发明公开了一种基于FPGA和TDC的高精度频率检测方法,采用FPGA和TDC;其中,FPGA产生预设闸门信号,通过预设闸门和被测信号控制实际闸门,在实际闸门时间内,对被测信号与标准信号进行计数,并与TDC芯片进行通信,在实际闸门关闭后,继续对标准信号进行计数并再次与TDC芯片通信。通过TDC芯片产生的输出信号与标准信号与被测信号的计数器值进行计算,从而得到被测信号频率值。本发明的有益效果在于,此方法的测频误差远小于现有技术的测频误差。技术研发人员:夏敦柱,赵纪飞受保护的技术使用者:东南大学技术研发日:技术公布日:2024/9/2本文地址:https://www.jishuxx.com/zhuanli/20240905/286058.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表