一种沟槽隔离结构及其制备方法与流程

- 国知局

- 2024-09-11 14:23:33

本发明涉及半导体,特别是涉及一种沟槽隔离结构及其制备方法。

背景技术:

1、目前bcd(在同一芯片上制作双极管bipolar、cmos和dmos器件)浅沟槽工艺中,通过测试模式的fa(失效分析)发现在硅衬底的顶部角出现肩膀塌陷问题,并且在沟槽的填充层预清洗后容易形成divot(凹陷区),如图1-图2所示,分别为沟槽隔离结构的一种tem图、沟槽隔离结构的另一种tem图,其中图2的虚线部分为凹陷区,且aa corner(有源区与沟槽搭界处的沟槽侧壁顶角)处的填充层厚度偏薄导致容易引起击穿,引起nmos(n型金属氧化物半导体)的tddb(time-dependent dielectric breakdown,时序相关介电击穿)失效。时序相关介电击穿失效是指在一定的电压和温度条件下,器件的介电层(通常是栅氧化物)随时间逐渐退化,最终导致击穿的现象,可采用时序相关介电击穿寿命对其进行测试分析。

2、鉴于此,急需一种能够提升有源区与沟槽搭界处的沟槽侧壁顶角处的栅氧层的最小厚度,进而提升器件耐压性及时序相关介电击穿寿命的沟槽隔离结构的制备方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种沟槽隔离结构及其制备方法,用于解决现有技术中有源区与沟槽搭界处的沟槽侧壁顶角处的栅氧层厚度偏薄导致容易引起击穿,引起半导体器件的时序相关介电击穿失效的问题。

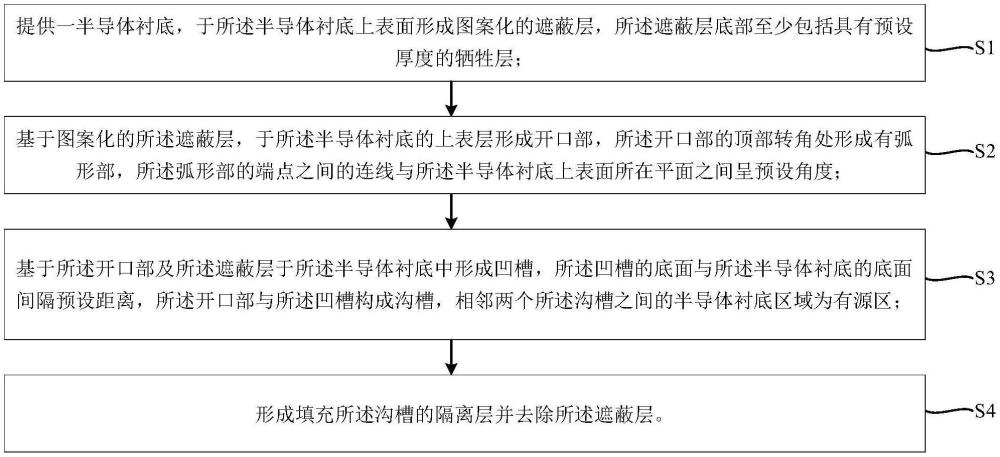

2、为实现上述目的及其他相关目的,本发明提供一种沟槽隔离结构的制备方法,包括以下步骤:

3、提供一半导体衬底,于所述半导体衬底上表面形成图案化的遮蔽层,所述遮蔽层底部至少包括具有预设厚度的牺牲层;

4、基于图案化的所述遮蔽层,于所述半导体衬底的上表层形成开口部,所述开口部的顶部转角处形成有弧形部,所述弧形部的端点之间的连线与所述半导体衬底上表面所在平面之间呈预设角度;

5、基于所述开口部及所述遮蔽层于所述半导体衬底中形成凹槽,所述凹槽的底面与所述半导体衬底的底面间隔预设距离,所述开口部与所述凹槽构成沟槽,相邻两个所述沟槽之间的半导体衬底区域为有源区;

6、形成填充所述沟槽的隔离层并去除所述遮蔽层。

7、可选地,所述遮蔽层包括第一膜层以及第二膜层,所述第一膜层及所述第二膜层依次层叠设置于所述牺牲层上方。

8、可选地,所述第一膜层的材质包括氮化硅;所述第二膜层的材质包括氮氧化硅。

9、可选地,去除所述第一膜层的方法包括化学机械研磨;去除所述第二膜层的方法包括化学机械研磨;去除所述牺牲层的方法包括湿法刻蚀。

10、可选地,所述预设角度的范围为29°~36°。

11、可选地,所述牺牲层的厚度与所述弧形部的端点之间的水平距离的比值处于预设比值范围内,所述预设比值的范围为2.304~2.816。

12、可选地,形成所述开口部的方法包括等离子体刻蚀;形成所述凹槽的方法包括等离子体刻蚀。

13、可选地,所述隔离层包括覆盖所述沟槽内壁及底面的缓冲层以及填充所述沟槽的剩余间隙的填充层,所述缓冲层包裹所述填充层的侧壁和底部,所述填充层与所述缓冲层构成隔离层。

14、本发明还提供一种沟槽隔离结构,包括:

15、半导体衬底;

16、沟槽,包括开口部及凹槽,所述开口部位于所述半导体衬底的上表层且所述开口部的顶部转角处形成有弧形部,所述弧形部的端点之间的连线与所述半导体衬底上表面所在平面之间呈预设角度,所述凹槽的底面与所述半导体衬底的底面具有预设间隔距离;

17、有源区,设置于相邻两个所述沟槽之间的半导体衬底区域;

18、填充层,填充所述沟槽。

19、可选地,所述预设角度的范围为29°~36°。

20、如上所述,本发明的沟槽隔离结构及其制备方法,具有以下有益效果:在形成所述沟槽隔离结构的过程中,通过设置所述遮蔽层底部为具有所述预设厚度的所述牺牲层,并通过调控所述牺牲层的厚度与所述弧形部的端点之间的水平距离的比值处于预设比值范围内,调控所述弧形部的端点之间的连接直线与所述半导体衬底上表面所在平面之间的夹角呈所述预设角度,提升了所述弧形部附近的所述沟槽内的所述填充层的厚度,提升了所述沟槽隔离结构的填充良率,继而提升了半导体器件耐压性,避免了半导体器件的时序相关介电击穿失效。

技术特征:1.一种沟槽隔离结构的制备方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的沟槽隔离结构的制备方法,其特征在于:所述遮蔽层包括第一膜层以及第二膜层,所述第一膜层及所述第二膜层依次层叠设置于所述牺牲层上方。

3.根据权利要求2所述的沟槽隔离结构的制备方法,其特征在于:所述第一膜层的材质包括氮化硅;所述第二膜层的材质包括氮氧化硅。

4.根据权利要求2所述的沟槽隔离结构的制备方法,其特征在于:去除所述第一膜层的方法包括化学机械研磨;去除所述第二膜层的方法包括化学机械研磨;去除所述牺牲层的方法包括湿法刻蚀。

5.根据权利要求1所述的沟槽隔离结构的制备方法,其特征在于:所述预设角度的范围为29°~36°。

6.根据权利要求1所述的沟槽隔离结构的制备方法,其特征在于:所述牺牲层的厚度与所述弧形部的端点之间的水平距离的比值处于预设比值范围内所述预设比值的范围为2.304~2.816。

7.根据权利要求1所述的沟槽隔离结构的制备方法,其特征在于:形成所述开口部的方法包括等离子体刻蚀;形成所述凹槽的方法包括等离子体刻蚀。

8.根据权利要求1所述的沟槽隔离结构的制备方法,其特征在于:所述隔离层包括覆盖所述沟槽内壁及底面的缓冲层以及填充所述沟槽的剩余间隙的填充层,所述缓冲层包裹所述填充层的侧壁和底部,所述填充层与所述缓冲层构成隔离层。

9.一种沟槽隔离结构,其特征在于,包括:

10.根据权利要求9所述的沟槽隔离结构,其特征在于:所述预设角度的范围为29°~36°。

技术总结本发明提供一种沟槽隔离结构及其制备方法,包括以下步骤:提供一半导体衬底,于半导体衬底上表面形成图案化的遮蔽层,遮蔽层底部至少包括具有预设厚度的牺牲层;基于图案化的遮蔽层,于半导体衬底的上表层形成开口部,开口部的顶部转角处形成有弧形部,弧形部的端点之间的连线与半导体衬底上表面所在平面之间呈预设角度;基于开口部及遮蔽层于半导体衬底中形成凹槽,凹槽的底面与半导体衬底的底面间隔预设距离,开口部与凹槽构成沟槽,相邻两个沟槽之间的半导体衬底区域为有源区;形成填充沟槽的隔离层并去除遮蔽层。本发明的沟槽隔离结构及其制备方法有效提升了器件耐压性,避免了器件的时序相关介电击穿失效。技术研发人员:张琼文,沈显青,刘峰松,袁慎顽受保护的技术使用者:上海积塔半导体有限公司技术研发日:技术公布日:2024/9/9本文地址:https://www.jishuxx.com/zhuanli/20240911/290545.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表