一种基于合金层的提高种子层附着力的方法与流程

- 国知局

- 2024-10-09 14:42:46

本发明涉及集成电路,更具体地,涉及一种基于合金层的提高种子层附着力的方法。

背景技术:

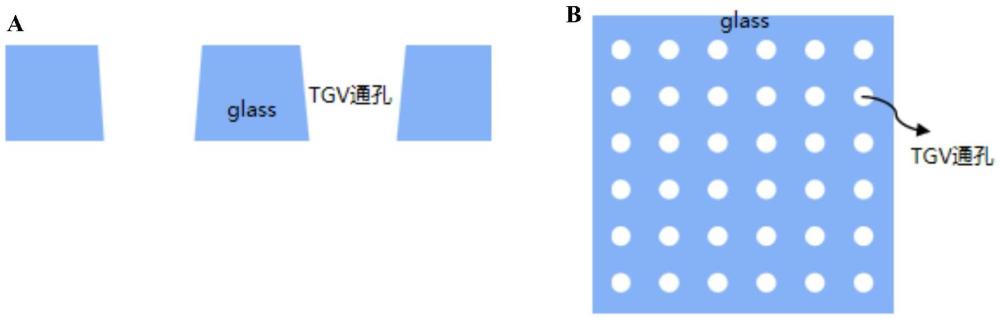

1、chiplet异质集成技术开发与整合的关键在于融合实现多尺度、多维度的芯片互连,从而提高电源效率并减小延迟,为高性能计算、人工智能和智慧终端等提供更小尺寸和更高性能的芯片。芯片的垂直方向互连主要依赖硅通孔(tsv)或玻璃通孔(tgv)等技术,水平方向上则主要通过重布线系统(rdl)技术进行互连。

2、tgv通孔和tsv通孔的金属填充,一般是先采用磁控溅射方式,在基板表面及通孔侧壁沉积cu种子层,然后再电镀cu,将通孔填充满cu。但是在沉积高深宽比(深宽比一般为3:1-20:1)的tgv基板时,溅射金属粒子到达侧壁的能量减弱,导致种子层和深孔侧壁之间的附着力低,存在剥离风险。

3、因此,亟需开发一种能够提高种子层附着力的方法,尤其适用于沉积高深宽比的tgv基板,避免种子层和深孔侧壁之间发生剥离风险。

技术实现思路

1、本发明旨在至少解决上述现有技术中存在的技术问题之一。为此,本发明提出一种基于合金层的提高种子层附着力的方法。本发明通过离子注入的方式,在基板和通孔侧壁形成一层合金层,再沉积后续的屏障层、种子层,合金层大大增加了基板表面和种子层之间、通孔侧壁和种子层之间的附着力,降低了剥离风险。

2、本发明的第一方面提供一种基于合金层的提高种子层附着力的方法。

3、具体地,一种基于合金层的提高种子层附着力的方法,包括如下步骤:

4、(1)基板开通孔;

5、(2)采用离子注入的方式,将金属离子注入至所述基板的表面和所述通孔的侧壁,形成合金层;

6、(3)在所述合金层表面沉积屏障层;

7、(4)在所述屏障层表面沉积种子层;

8、(5)在所述基板上制作电镀光阻层(pr pattern);

9、(6)在所述电镀光阻层表面沉积电镀cu,形成cu柱;

10、(7)剥离所述电镀光阻层(pr pattern),得到含种子层的基板;

11、(8)将所述含种子层的基板进行刻蚀,至所述电镀光阻层原本所在位置的种子层被刻蚀完全,即结束刻蚀。

12、本发明在完成开通孔的基板表面,进行离子注入,使得金属离子被注入到基板表面和通孔侧壁,如此便在基板表面和通孔侧壁形成合金层(alloy层),然后再依次沉积屏障层(barrier层)和种子层,由于基板和屏障层之间存在合金层,起到缓冲作用,合金层可以大幅地提升种子层和基板之间、种子层和通孔侧壁之间的附着力,且具有一定的导电性。然后再依次制作电镀光阻层、沉积电镀cu、剥离电镀光阻,最后刻蚀去除电镀光阻层原本所在位置的种子层,此时仍然保留了部分未被刻蚀完全的cu柱。

13、优选地,步骤(1)中,所述基板为tgv基板或tsv基板。

14、优选地,步骤(1)中,所述基板的厚度为0.1-1mm。

15、进一步优选地,步骤(1)中,所述基板的厚度为0.4-0.5mm。

16、优选地,步骤(1)中,开通孔后的基板中包括基板表面区和通孔侧壁,所述基板表面区为无通孔的平坦部分。

17、优选地,步骤(1)中,所述通孔的孔径为10-200μm,和/或所述通孔的深宽比为3:1-20:1。

18、进一步优选地,步骤(1)中,所述通孔的孔径为80-100μm,和/或所述通孔的深宽比为5:1-10:1。

19、优选地,步骤(2)中,所述离子注入为采用ti离子、mo离子、ni离子、ta离子中的一种注入。

20、进一步优选地,步骤(2)中,所述离子注入为ti离子注入,所述合金层为tisi合金层(tisi alloy层)。

21、优选地,步骤(2)中,所述离子注入的能量为1-3000kev。

22、进一步优选地,步骤(2)中,所述离子注入的能量为600-3000kev。

23、优选地,步骤(2)中,所述合金层的厚度为1-10nm。

24、进一步优选地,步骤(2)中,所述合金层的厚度为5-10nm。

25、优选地,步骤(3)、(4)和(6)中,通过磁控溅射进行沉积,所述磁控溅射的能量为200-700ev。

26、进一步优选地,步骤(3)、(4)和(6)中,通过磁控溅射进行沉积,所述磁控溅射的能量为300-600ev。

27、优选地,步骤(3)中,所述屏障层为ti层。作为cu种子层的barrier层。

28、优选地,步骤(3)中,所述屏障层沉积在基板表面和通孔侧壁。

29、优选地,步骤(3)中,所述基板表面的屏障层的厚度为30-200nm。

30、优选地,步骤(4)中,所述种子层为cu种子层。

31、优选地,所述ti层和所述cu种子层合并称为ticu种子层。

32、优选地,步骤(3)中,所述种子层覆盖基板表面和通孔侧壁。

33、优选地,步骤(4)中,所述基板表面的种子层的厚度为100-600nm。

34、优选地,步骤(5)中,通过涂布、曝光、显影方式在基板上制作电镀光阻图案。

35、优选地,步骤(6)中,通过电镀方式沉积电镀cu。

36、优选地,步骤(6)中,沉积电镀cu至通孔被完全覆盖,形成cu柱。

37、优选地,步骤(6)中,所述基板表面的电镀cu的厚度3-30μm。

38、优选地,步骤(7)中,采用剥离液,在35-45℃下,剥离所述电镀光阻层。

39、优选地,步骤(7)中,所述剥离液为乙二醇。

40、优选地,步骤(8)中,将含种子层的基板置于刻蚀液中进行刻蚀。

41、优选地,步骤(8)中,所述刻蚀液为含氟的h2o2刻蚀液。

42、优选地,步骤(8)中,结束刻蚀后,继续通过湿制程刻蚀方法进行过刻蚀,至所述电镀光阻层原本所在位置的合金层被刻蚀完全。如此可以避免tgv通孔cu柱间的信号干扰(如果不将电镀光阻层原本所在位置的合金层刻蚀掉,那么两个cu柱间的阻抗可能<1mω,造成电信号干扰)。

43、相对于现有技术,本发明的有益效果如下:

44、本发明先将基板开通孔,然后进行离子注入,使金属离子被注入到基板表面和通孔侧壁,形成合金层,然后依次沉积屏障层、种子层、制作电镀光阻层、沉积电镀cu、剥离电镀光阻,最后刻蚀去除合金层,避免tgv通孔cu柱间的信号干扰(如果不将合金层刻蚀掉,那么两个cu柱间的阻抗可能<1mω,造成电信号干扰),由于本发明在基板和屏障层之间增加了合金层,起到缓冲作用,具有一定的导电性,可以提高屏障层和基板之间以及屏障层和通孔侧壁之间的附着力,避免种子层和深孔侧壁的附着力存在剥离风险。

技术特征:1.一种提高种子层附着力的方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的方法,其特征在于,步骤(1)中,所述基板为tgv基板或tsv基板。

3.根据权利要求1所述的方法,其特征在于,步骤(1)中,所述通孔的孔径为10-200μm,和/或所述通孔的深宽比为3:1-20:1。

4.根据权利要求1所述的方法,其特征在于,步骤(2)中,所述离子注入为采用ti离子、mo离子、ni离子、ta离子中的一种注入。

5.根据权利要求4所述的方法,其特征在于,步骤(2)中,所述离子注入为ti离子注入,所述合金层为tisi合金层。

6.根据权利要求5所述的方法,其特征在于,步骤(2)中,所述离子注入的能量为1-3000kev。

7.根据权利要求1所述的方法,其特征在于,步骤(3)中,所述基板表面的屏障层的厚度30-200nm。

8.根据权利要求1所述的方法,其特征在于,步骤(4)中,所述基板表面的种子层的厚度为100-600nm。

9.根据权利要求1所述的方法,其特征在于,步骤(6)中,沉积电镀cu至通孔被完全覆盖,形成cu柱。

10.根据权利要求9所述的方法,其特征在于,步骤(6)中,所述基板表面的电镀cu的厚度3-30μm。

技术总结本发明属于集成电路技术领域,提供了一种基于合金层的提高种子层附着力的方法。本发明先将的基板完成开通孔,然后进行离子注入,使金属离子被注入到基板表面和通孔侧壁,形成合金层,然后依次沉积屏障层、沉积种子层、制作电镀光阻层、沉积电镀Cu、剥离电镀光阻,最后刻蚀去除合金层,避免TGV通孔Cu柱间的信号干扰,由于本发明在基板和屏障层之间增加了合金层,起到缓冲作用,具有一定的导电性,还可以提高屏障层和基板之间以及屏障层和通孔侧壁之间的附着力,避免种子层和深孔侧壁的剥离风险。技术研发人员:胡小波,张晓军,李佳小龙,夏慧,谢明辉,冯俊杰受保护的技术使用者:深圳市矩阵多元科技有限公司技术研发日:技术公布日:2024/9/29本文地址:https://www.jishuxx.com/zhuanli/20241009/306211.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表