碳化硅半导体装置及其制造方法与流程

- 国知局

- 2024-10-15 09:57:46

本公开涉及一种碳化硅半导体装置及其制造方法。

背景技术:

1、在专利文献1中公开有以下的半导体装置:通过对六方晶单晶体的碳化硅基板进行磷的离子注入来形成非晶层,并通过进行热处理来将非晶层重结晶为立方晶单晶体的n型碳化硅,并通过在n型碳化硅的上表面蒸镀镍来形成电极。

2、在专利文献2中公开有以下的半导体装置:在形成于由4h-sic构成的n+型sic的第一主面上的n-型外延生长层内,具有n+型源极区和形成于n+型源极区内的n+型3c-sic区及p+型电位固定区,与n+型3c-sic区及p+型电位固定区相接地形成阻挡金属膜,在阻挡金属膜上形成源极布线用电极。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开2009-49198号公报

6、专利文献2:国际公开第2017/042963号

技术实现思路

1、发明要解决的问题

2、在沟槽栅型的碳化硅半导体装置中,研究了将源极区(主区)用3c-sic构成以与源极电极(主电极)进行欧姆接触。在该情况下,在制造上合理的过程是,在通过n型杂质的离子注入在整个面形成了n+型的源极区之后,通过使用了掩模进行的p型杂质的离子注入来使源极区的一部分的导电型反转(击回(日文:打ち返す))从而形成p+型的基极接触区。然而,在源极区进行了击回的部分产生很多损伤,有时产生泄漏不良。

3、本公开鉴于上述问题,目的在于提供在沟槽栅型的碳化硅半导体装置中主区不借助硅化物层就能够与主电极进行欧姆接触、并且能够抑制泄漏不良的碳化硅半导体装置及其制造方法。

4、用于解决问题的方案

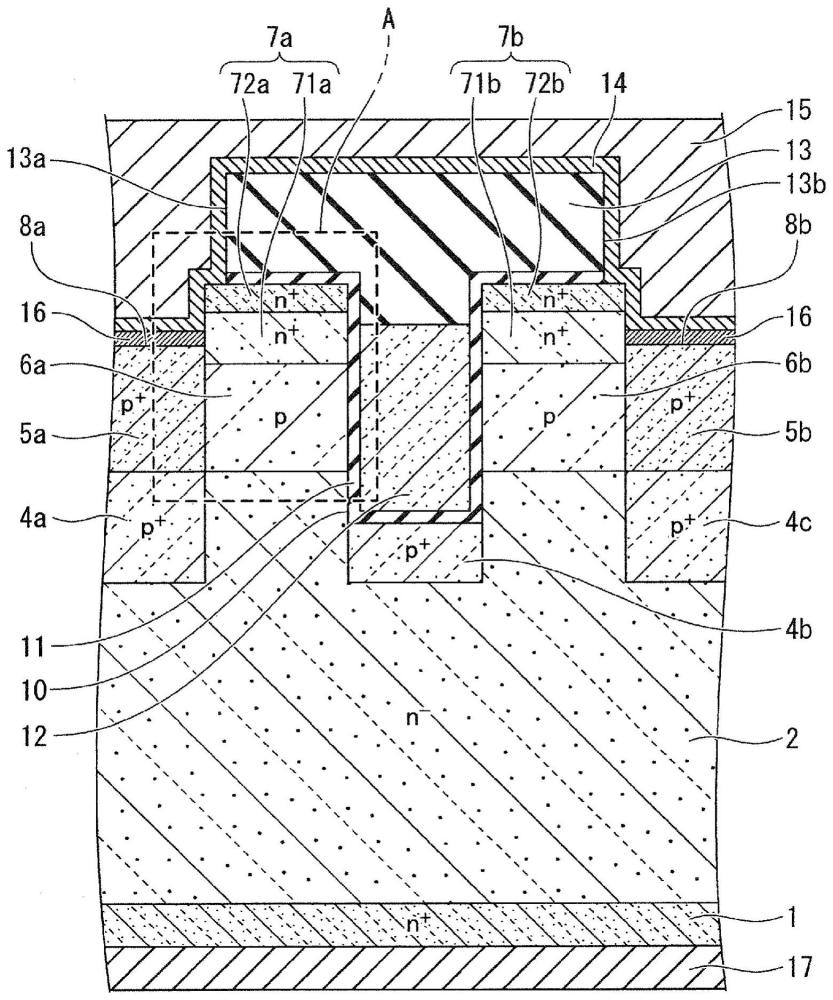

5、为了实现上述目的,本公开的一个方式的主旨在于提供一种以下的碳化硅半导体装置,具备:由碳化硅构成的第一导电型的漂移层;由碳化硅构成的第二导电型的基区,其设置于漂移层的上表面侧;包含3c结构的碳化硅的第一导电型的源极接触区,其设置于基区的上表面侧;栅极绝缘膜,其设置于贯通源极接触区和基区的栅极沟槽的内侧;栅极电极,其隔着栅极绝缘膜设置于栅极沟槽的内侧;主电极,其设置于与栅极沟槽分离地设置的接触沟槽的内侧,与源极接触区的至少侧面相接;以及第二导电型的基极接触区,其与接触沟槽的下表面相接,由4h结构的碳化硅构成,杂质浓度比基区的杂质浓度高,其中,接触沟槽的下表面比源极接触区的下表面深。

6、本公开的其它方式的主旨在于提供一种以下的碳化硅半导体装置的制造方法,包括以下工序:在由碳化硅构成的第一导电型的漂移层的上表面侧形成由碳化硅构成的第二导电型的基区;在基区的上表面侧形成包含3c结构的碳化硅的第一导电型的源极接触区;形成贯通源极接触区和基区的栅极沟槽;在栅极沟槽的内侧隔着栅极绝缘膜形成栅极电极;与栅极沟槽分离地形成贯通源极接触区的接触沟槽;在接触沟槽的内侧形成与源极接触区的至少侧面相接的主电极;以及以与接触沟槽的下表面相接的方式形成杂质浓度比基区的杂质浓度高的第二导电型的基极接触区,该基极接触区由4h结构的碳化硅构成,其中,将接触沟槽的下表面形成得比源极接触区的下表面深。

7、发明的效果

8、根据本公开,能够提供在沟槽栅型的碳化硅半导体装置中主区不借助硅化物层就能够与主电极进行欧姆接触、并且能够抑制泄漏不良的碳化硅半导体装置及其制造方法。

技术特征:1.一种碳化硅半导体装置,具备;

2.根据权利要求1所述的碳化硅半导体装置,其中,

3.根据权利要求1所述的碳化硅半导体装置,其中,

4.根据权利要求1或2所述的碳化硅半导体装置,其中,

5.根据权利要求4所述的碳化硅半导体装置,其中,

6.根据权利要求4所述的碳化硅半导体装置,其中,

7.根据权利要求4所述的碳化硅半导体装置,其中,

8.根据权利要求1或2所述的碳化硅半导体装置,其中,

9.根据权利要求1或2所述的碳化硅半导体装置,其中,

10.根据权利要求1或2所述的碳化硅半导体装置,其中,

11.根据权利要求1或2所述的碳化硅半导体装置,其中,

12.根据权利要求1或2所述的碳化硅半导体装置,其中,

13.根据权利要求1或2所述的碳化硅半导体装置,其中,

14.根据权利要求4所述的碳化硅半导体装置,其中,

15.根据权利要求4所述的碳化硅半导体装置,其中,

16.根据权利要求1或2所述的碳化硅半导体装置,其中,

17.根据权利要求1或2所述的碳化硅半导体装置,其中,

18.一种碳化硅半导体装置的制造方法,包括以下工序:

19.根据权利要求18所述的碳化硅半导体装置的制造方法,其中,

20.根据权利要求18所述的碳化硅半导体装置的制造方法,其中,还包括以下工序:

技术总结本公开提供一种碳化硅半导体装置及其制造方法,主区不借助硅化物层就能够与主电极进行欧姆接触,并且能够抑制泄漏不良。具备:第一导电型的漂移层;第二导电型的基区,其设置于漂移层的上表面侧;包含3C结构的碳化硅的第一导电型的源极接触区,其设置于基区的上表面侧;栅极电极,其隔着栅极绝缘膜设置于栅极沟槽的内侧;主电极,其设置于接触沟槽的内侧,与源极接触区的侧面相接;以及第二导电型的基极接触区,其与接触沟槽的下表面相接,由4H结构的碳化硅构成,其中,接触沟槽的下表面比源极接触区的下表面深。技术研发人员:大瀬直之受保护的技术使用者:富士电机株式会社技术研发日:技术公布日:2024/10/10本文地址:https://www.jishuxx.com/zhuanli/20241015/315920.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。