双面刻蚀双面填充沟槽电极硅探测器

- 国知局

- 2024-11-06 14:35:20

本发明属于硅探测器,涉及一种双面刻蚀双面填充沟槽电极探测器。

背景技术:

1、目前,国内外对硅基半导体探测材料的研究多集中于高纯硅基材料。高纯硅层作为硅基光探测器的基本材料,直接关系到器件的性能,硅材料广泛应用在硅半导体探测器和微电子集成电路中。近十年来,人们对高纯硅制作技术有了很大的改善,使其性能有了很大的提升。目前我国对硅基半导体探测器的研究重点是如何提高单晶硅的纯度,以及如何有效地调控其杂质与缺陷。

2、在单晶制备方面,我国主要是利用化学气相沉积法、熔合区等工艺,但在品质方面仍存在较大差距。在器件制备技术方面,目前国内外已有较为成熟的制作工艺,如离子注入法、气相沉积法、磁控溅射法、电子束蒸镀法、光刻法等,并已经有较为成熟的工艺路线。然而,目前我国在这一领域的研究还处于起步阶段,对离子注入的剂量及深度的掌握还不够精准,在cvd、pvd等领域仍然面临着很大的技术瓶颈,有待于进一步改进。

3、对于传统的三维沟槽电极硅探测器,需要保证在刻蚀过程中,探测器主体不从衬底上脱落。在刻蚀完成后,由于硅衬底的厚度较薄,沟槽电极不能完全穿透整个硅衬底,只能刻蚀到硅衬底深度的90%左右。因此,为了确保探测器结构单元或阵列具有良好的机械稳定性,硅片上就需要保留一定厚度的基底。因此,传统的三维沟槽电极硅探测器的第一个缺点是在未刻蚀区域存在死区。死区是指探测器未刻蚀部分中的弱电场或零电场区域。如果死区占据了探测器体积的很大一部分,那么探测器的电学特性将受到严重影响,从而降低电荷收集效率。其次,传统三维沟槽电极探测器的电极间距不同,这也是导致电荷收集率降低的一个关键因素。在电极间距最大处,电场强度最低,电子-空穴的漂移动力不足,被俘获的概率增加,这就导致探测器的电荷收集率降低,电极间距的不同对探测器性能的稳定造成了很大影响。

4、因此,亟需一种简单有效的三维沟槽电极硅探测器,以消除传统探测器存在的死区的问题,且性能优异。

技术实现思路

1、为了达到上述目的,本发明提供一种双面刻蚀双面填充沟槽电极探测器,解决了传统硅探测器无法消除死区、稳定性差的问题,同时实现电极的贯穿性,且性能优异。

2、本发明所采用的技术方案是,

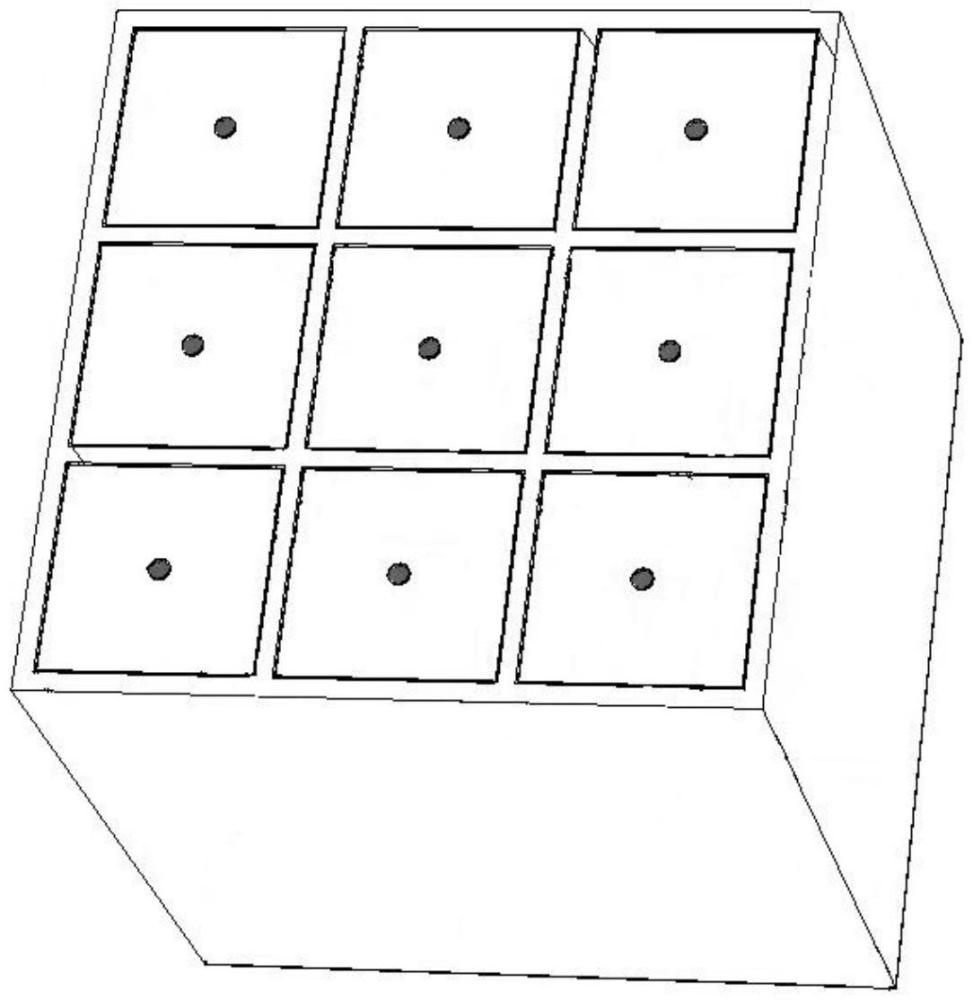

3、双面刻蚀双面填充沟槽电极探测器,包括:硅基体,硅基体形状为立方体;硅基体中心沿着竖直方向两侧设置中央阳极;硅基体两侧设有沟槽阴极;相邻的硅基体共享相同的沟槽阴极;中央阳极下部覆盖阳极铝电极接触层;沟槽阴极上部外侧覆盖阴极铝电极接触层;硅基体下表面除过沟槽阴极两侧未覆盖阳极铝电极接触层处覆盖下表面sio2层;硅基体上表面除过中央阳极上部未覆盖阴极铝电极接触层处覆盖上表面sio2层。

4、进一步的,中央阳极的直径为:5-20μm;相邻硅基体的沟槽阴极之间的距离为:5-20μm。

5、进一步的,所述硅基体为n型轻掺杂,掺杂浓度为4×1011/cm3-2×1012/cm3。

6、进一步的,所述中央阳极为n型重掺杂,掺杂浓度为1×1018/cm3-2×1020/cm3。

7、进一步的,所述沟槽阴极为p型重掺杂,掺杂浓度1×1018/cm3~2×1020/cm3。

8、进一步的,所述上表面sio2层与下表面sio2层厚度都为1μm。

9、进一步的,所述阳极铝电极接触层与阴极铝电极接触层的厚度均为1μm。

10、进一步的,所述硅基体的数量为n2,构成n×n阵列。

11、进一步的,所述每个硅基体中,沟槽阴极与中央阳极之间的间距均相等。

12、本发明的有益效果是:

13、1,现有的贯穿沟槽电极探测器较多,由于工艺技术的限制,电极刻蚀无法完全贯穿整个硅体,均保留了一定厚度作为衬底防止硅体脱落,导致探测器中存在一部分无法刻蚀的区域,即所谓的“死区”,因此传统三维沟槽探测器的底部永远存在死区部分,这部分死区的电场较弱,电荷分布不均匀,严重影响了探测器的性能。本发明探测器通过优化刻蚀工艺,在硅探测器的两面都进行刻蚀和填充,可以先进行硅体上半部分的沟槽的刻蚀和填充,再进行硅体剩余部分的沟槽的刻蚀和填充,这就保证了在刻蚀的过程中硅体不脱落,从而不需要衬底作为支撑。因此,本发明中央阳极和沟槽阴极都贯穿整个硅基体,确保电极能够深入到基体的每一个角落,完全穿过硅基体。这种设计使得电场能够均匀分布在整个探测器中,消除了死区的存在,从而实现硅体的全面利用。

14、2,本发明探测器的全耗尽电压更低,在无辐照情况下探测器单元的耗尽电压仅为1.8v,能耗低,电荷收集速率更快。

15、3,由于本发明探测器中,电场能够无阻碍地贯穿整个硅体,不再受到死区的限制。因此,本发明探测器提供了最大的体积用于电荷收集,能够更加均匀地分布电荷,更快速地收集和传输电荷;相比于传统柱状电极硅探测器、传统三维沟槽探测器,本发明提高了探测器对粒子或光子的探测效率,提高探测器的响应速度,从而提高探测器的性能。

16、4,由于本发明探测器使用双面刻蚀双面填充的技术以及贯穿电极的存在,其电场和电势分布更加均匀,因此可以设计任意不同电极间距的探测器,它们的全耗尽电压会随电极间距的增大而增大,但电场与电势分布都比较均匀。同时,可以提高探测器对粒子或光子的灵敏度,有助于进一步精确定位入射粒子或光子的位置,提高探测器的位置分辨率。

17、5,传统的三维沟槽电极探测器阴极铝电极接触层和阳极铝电极接触层在同一个平面,而本发明的阴极铝电极接触层和阳极铝电极接触层是分隔开的,在阴极铝电极接触层一面加偏置电压,在阳极铝电极接触层一面读出,可以避免电极被击穿的危险。

技术特征:1.双面刻蚀双面填充沟槽电极探测器,包括:硅基体(5),其特征在于,硅基体(5)形状为立方体;硅基体(5)中心沿着竖直方向两侧设置中央阳极(2);硅基体(5)两侧设有沟槽阴极(4);相邻的硅基体(5)共享相同的沟槽阴极(4);中央阳极(2)下部覆盖阳极铝电极接触层(7);沟槽阴极(4)上部外侧覆盖阴极铝电极接触层(3);硅基体(5)下表面除过沟槽阴极(4)两侧未覆盖阳极铝电极接触层(7)处覆盖下表面sio2层(6);硅基体(5)上表面除过中央阳极(2)上部未覆盖阴极铝电极接触层(3)处覆盖上表面sio2层(1)。

2.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,中央阳极(2)的直径为:5-20μm;相邻硅基体(5)的沟槽阴极(4)之间的距离为:5-20μm。

3.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述硅基体(5)为n型轻掺杂,掺杂浓度为4×1011/cm3-2×1012/cm3。

4.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述中央阳极(2)为n型重掺杂,掺杂浓度为1×1018/cm3-2×1020/cm3。

5.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述沟槽阴极(4)为p型重掺杂,掺杂浓度1×1018/cm3~2×1020/cm3。

6.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述上表面sio2层(1)与下表面sio2层(6)厚度都为1μm。

7.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述阳极铝电极接触层(7)与阴极铝电极接触层(3)的厚度均为1μm。

8.根据权利要求1所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述硅基体(5)的数量为n2,构成n×n阵列。

9.根据权利要求8所述的双面刻蚀双面填充沟槽电极探测器,其特征在于,所述每个硅基体(5)中,沟槽阴极(4)与中央阳极(2)之间的间距均相等。

技术总结本发明提供了一种双面刻蚀双面填充沟槽电极探测器,包括:硅基体,硅基体形状为立方体;硅基体中心沿着竖直方向两侧设置中央阳极;硅基体两侧设有沟槽阴极;相邻的硅基体共享相同的沟槽阴极;中央阳极下部覆盖阳极铝电极接触层;沟槽阴极上部外侧覆盖阴极铝电极接触层;硅基体下表面除过沟槽阴极两侧未覆盖阳极铝电极接触层处覆盖下表面SiO<subgt;2</subgt;层;硅基体上表面除过中央阳极上部未覆盖阴极铝电极接触层处覆盖上表面SiO<subgt;2</subgt;层。以解决传统硅探测器无法消除死区、稳定性差的问题,同时实现电极的贯穿性,且性能优异。技术研发人员:朱旭然,李正,刘志宇,谭泽文,孙佳雄,李晓丹受保护的技术使用者:鲁东大学技术研发日:技术公布日:2024/11/4本文地址:https://www.jishuxx.com/zhuanli/20241106/323009.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表