半导体结构及其形成方法与流程

- 国知局

- 2024-11-19 09:37:38

本发明涉及半导体制造,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、集成电路一般由一层半导体器件和多层互连线组成。早期集成电路性能提高和功能扩展的重点都集中在晶体管层面,即通过减小特征尺寸(critical dimension)实现更高的速度、更低的功耗,以及更高的集成度。且传统的集成电路封装是在一个封装内放置一个晶片(裸芯片)或平面放置多个晶片(mcm),这种封装形式称为2d。

2、随着半导体工艺特征尺寸的不断缩小,特别是进入纳米尺寸范围后,半导体制造技术难度越来越大,传统的技术越来越接近物理尺寸极限。由此,三维集成电路随之应用而生。

3、三维集成电路(three-dimensional integrated circuit,3d ic)在垂直方向堆叠多个同构或异构的晶片或电路模块,利用硅通孔(through silicon via,tsv)实现垂直方向电气连接,具有互连密度高、外形尺寸小、低功耗和大带宽等众多优势。

4、然而,现有三维集成电路的电学性能仍有待提升。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构及其形成方法,能够有效提升最终形成的半导体结构的性能。

2、为解决上述问题,本发明提供一种半导体结构,包括相对第一面和第二面的第一晶圆;位于第二面表面的器件层;位于器件层内的互连层,互连层包括连接区和围绕连接区的开口区,开口区内具有若干相互分立且沿第一晶圆的表面法线方向贯穿互连层的开口;沿第一晶圆的表面法线方向贯穿第一晶圆的导电插塞,导电插塞一端伸入器件层内且与连接区相接触。

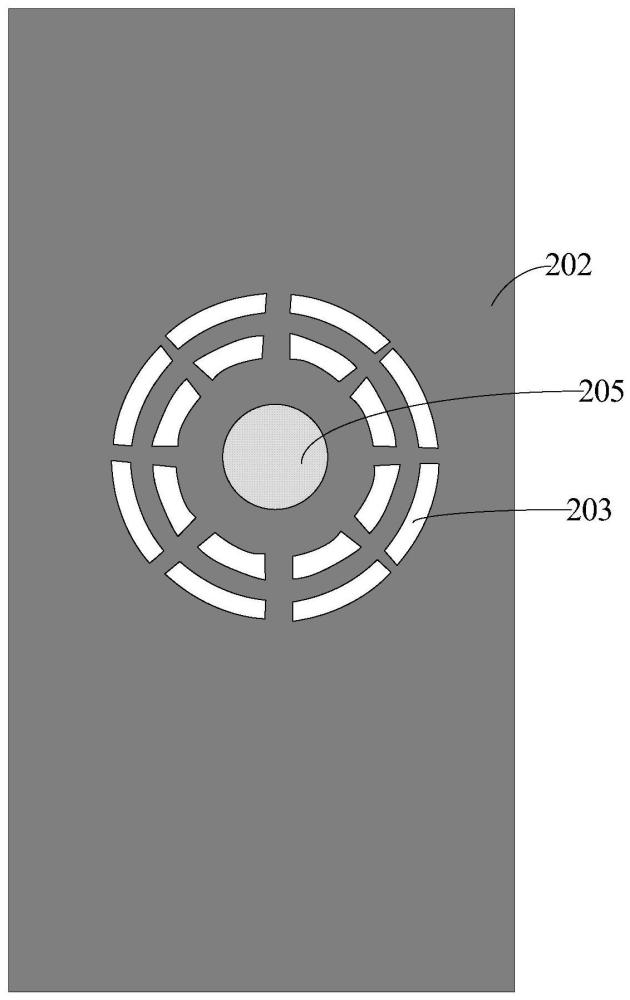

3、可选的,若干开口投影至互连层的图形以连接区的中心点呈中心对称分布。

4、可选的,开口投影至互连层表面的图形为扇形、圆形或者矩形。

5、可选的,若干开口以连接区的中心点呈圆环分布。

6、可选的,圆环的圈数大于等于1。

7、可选的,每圈圆环之间的间距范围为0.001um-100um,每圈圆环内的开口的数量大于1,开口在沿着圆环的径向上的尺寸范围为0.001um-100um,开口在沿着圆环的周向上的尺寸范围为0.001um-100um。

8、可选的,还包括:位于互连层上的辅助互连层,辅助互连层与互连层之间通过辅助插塞连接。

9、可选的,互连层在垂直于自第一面至第二面的长度大于辅助互连层在垂直于自第一面至第二面的长度,互连层与器件层内的功能电路连接。

10、可选的,辅助互连层的层数大于等于1。

11、可选的,互连层在垂直于自第一面至第二面的长度小于辅助互连层在垂直于自第一面至第二面的长度,辅助互连层与器件层内的功能电路连接。

12、可选的,辅助互连层包括辅助连接区和围绕辅助连接区的辅助开口区,辅助开口区内形成有若干辅助开口,辅助连接区与连接区对应,辅助开口区与开口区对应。

13、可选的,还包括:位于第一面的表面的第一钝化层,第一钝化层内具有暴露出导电插塞表面的开口;位于导电插塞的表面以及部分第一钝化层的表面形成连接层。

14、可选的,还包括:位于部分第一钝化层的表面和连接层的侧壁表面的第二钝化层。

15、可选的,还包括:与第一晶圆键合的第二晶圆,第二晶圆的器件层与第一晶圆的器件层键合。

16、相应的,本发明还提供一种半导体结构的形成方法,包括:提供第一晶圆,第一晶圆包括相对的第一面和第二面;在第二面表面形成器件层,器件层内具有互连层,互连层包括连接区和围绕连接区的开口区,在开口区内形成若干相互分立且沿着第一晶圆的表面法线方向贯穿互连层的开口;沿第一晶圆的表面法线方向自第一面至第二面刻蚀第一晶圆,在第一晶圆内形成的插塞孔,插塞孔的底部延伸入器件层内且暴露出部分连接区的表面;在插塞孔内形成导电插塞,导电插塞与连接区相接触。

17、可选的,在第二面的表面形成器件层的步骤包括:在第二面的表面形成第一介质层,在第一介质层内形成功能电路;在第一介质层的表面形成第二介质层;在第二介质层内形成互连层;在互连层的表面形成第三介质层。

18、可选的,互连层的形成步骤包括:在第二介质层内形成初始互连层,初始互连层包括连接区和开口区;在初始互连层的表面形成图形层,图形层内具有若干图形层开口,若干图形层开口的底部暴露出开口区的初始互连层的表面;以图形层为掩膜刻蚀初始互连层,在开口区内形成暴露出第一介质层表面的若干开口,相邻开口之间具有间隙。

19、可选的,还包括:在互连层上形成辅助互连层,辅助互连层与互连层之间通过辅助插塞连接。

20、可选的,形成辅助互连层的步骤包括:刻蚀第三介质层,在第三介质层内形成若干辅助插塞孔,若干辅助插塞孔的底部暴露出连接区的互连层的表面和相邻开口之间的互连层的表面;在辅助插塞孔内形成辅助插塞;在第三介质层的表面以及辅助插塞的表面形成第四介质层;刻蚀第四介质层,在第四介质层内形成暴露出辅助插塞的介质层开口;在介质层开口内形成辅助互连层;在第四介质层的表面和辅助互连层的表面形成第五介质层。

21、与现有技术相比,本发明的技术方案具有以下优点:

22、本发明的形成方法的方案中,器件层内具有互连层,互连层包括连接区和围绕连接区的开口区,开口区内形成有若干开口;导电插塞贯穿第一晶圆且延伸到器件层内且与连接区的互连层连接;一方面利用互连层内的开口使得互连层内部具有缝隙,能够在发生形变时产生一定的伸缩量,当插塞孔暴露出的互连层由于释放应力向导电插塞方向发生翘曲时,周围互连层就会产生阻止互连层反正翘曲的反作用力,从而大大降低了互连层发生翘曲的概率,降低半导体结构内孔洞出现的概率;另一方面导电插塞与连接区的互连层连接,保证导电插塞与互连层之间的接触面积,从而保证半导体结构的耐流能力,从而提升最终形成的半导体结构的质量和有效率,具有较广泛的适用范围。

技术特征:1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述半导体结构,其特征在于,若干所述开口投影至所述互连层的图形以所述连接区的中心点呈中心对称分布。

3.如权利要求1所述半导体结构,其特征在于,所述开口投影至所述互连层表面的图形为扇形、圆形或者矩形。

4.如权利要求1所述半导体结构,其特征在于,若干所述开口以所述连接区的中心点呈圆环分布。

5.如权利要求4所述半导体结构,其特征在于,所述圆环的圈数大于等于1。

6.如权利要求5所述半导体结构,其特征在于,每圈圆环之间的间距范围为0.001um-100um,每圈圆环内的开口的数量大于1,开口在沿着圆环的径向上的尺寸范围为0.001um-100um,开口在沿着圆环的周向上的尺寸范围为0.001um-100um。

7.如权利要求1所述半导体结构,其特征在于,还包括:位于所述互连层上的辅助互连层,所述辅助互连层与所述互连层之间通过辅助插塞连接。

8.如权利要求7所述半导体结构,其特征在于,所述互连层在垂直于自所述第一面至所述第二面的长度大于所述辅助互连层在垂直于自所述第一面至所述第二面的长度,所述互连层与所述器件层内的功能电路连接。

9.如权利要求8所述半导体结构,其特征在于,所述辅助互连层的层数大于等于1。

10.如权利要求7所述半导体结构,其特征在于,所述互连层在垂直于自所述第一面至所述第二面的长度小于所述辅助互连层在垂直于自所述第一面至所述第二面的长度,所述辅助互连层与所述器件层内的功能电路连接。

11.如权利要求7所述半导体结构,其特征在于,所述辅助互连层包括辅助连接区和围绕所述辅助连接区的辅助开口区,所述辅助开口区内形成有若干辅助开口,所述辅助连接区与所述连接区对应,所述辅助开口区与所述开口区对应。

12.如权利要求1所述半导体结构,其特征在于,还包括:位于所述第一面的表面的第一钝化层,所述第一钝化层内具有暴露出所述导电插塞表面的开口;位于所述导电插塞的表面以及部分所述第一钝化层的表面形成连接层。

13.如权利要求12所述半导体结构,其特征在于,还包括:位于部分所述第一钝化层的表面和所述连接层的侧壁表面的第二钝化层。

14.如权利要求1所述半导体结构,其特征在于,还包括:与所述第一晶圆键合的第二晶圆,所述第二晶圆的器件层与所述第一晶圆的器件层键合。

15.一种半导体结构的形成方法,其特征在于,包括:

16.如权利要求15所述半导体结构的形成方法,其特征在于,在所述第二面的表面形成所述器件层的步骤包括:

17.如权利要求16所述半导体结构的形成方法,其特征在于,所述互连层的形成步骤包括:

18.如权利要求16所述半导体结构的形成方法,其特征在于,还包括:在所述互连层上形成辅助互连层,所述辅助互连层与所述互连层之间通过辅助插塞连接。

19.如权利要求18所述半导体结构的形成方法,其特征在于,形成所述辅助互连层的步骤包括:

技术总结一种半导体结构及其形成方法,其中半导体结构包括相对第一面和第二面的第一晶圆;位于第二面表面的器件层;位于器件层内的互连层,互连层包括连接区和围绕连接区的开口区,开口区内具有若干相互分立且沿第一晶圆的表面法线方向贯穿互连层的开口;沿第一晶圆的表面法线方向贯穿第一晶圆的导电插塞,导电插塞一端伸入器件层内且与连接区相接触;能够有效提升最终形成的半导体结构的性能。技术研发人员:史鲁斌受保护的技术使用者:中芯国际集成电路制造(北京)有限公司技术研发日:技术公布日:2024/11/14本文地址:https://www.jishuxx.com/zhuanli/20241118/329554.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表