芯片封装结构及其制作方法与流程

- 国知局

- 2024-11-19 09:39:46

本发明涉及一种封装结构及其制作方法,尤其涉及一种芯片封装结构及其制作方法。

背景技术:

1、近年来,随着电子技术的日新月异,高科技电子产业的相继问世,使得更人性化、功能更佳的电子产品不断地推陈出新,并朝向轻、薄、短、小的趋势设计。就半导体封装技术而言,四方扁平无引脚封装结构(quad flat non-leaded package,qfn)或是晶圆级芯片尺寸封装(wafer level chip size package,wlcsp),因可减少元件体积而成为封装型态的主流之一。

2、一般而言,四方扁平无引脚封装结构所采用的导线架,是将金属薄板以蚀刻的方式来形成芯片承载座与多个引脚接垫。然而,因蚀刻金属板的关系,导致导线架的扇出线路宽度较大(大于80微米),以致不适合芯片上有高密度接垫的应用。为了解决上述的问题,目前业界是将晶圆上的芯片切开,在基板上重构(reconfiguration)以略微增加芯片和芯片之间的间距,然后直接制作芯片的上重布线路层(redistribution layer,rdl),并运用rdl技术进行重新布线。接着,在rdl线路上做绝缘层穿孔并上锡球。因此制作方式涉及晶圆级封装,因此制程的材料设备厂房昂贵,进而也影响生产成本。

技术实现思路

1、本发明是针对一种芯片封装结构及其制作方法,其利用低成本的大型基板及其基础设施的制程,避免晶圆级封装昂贵的厂房材料设备因而能降低生产成本。

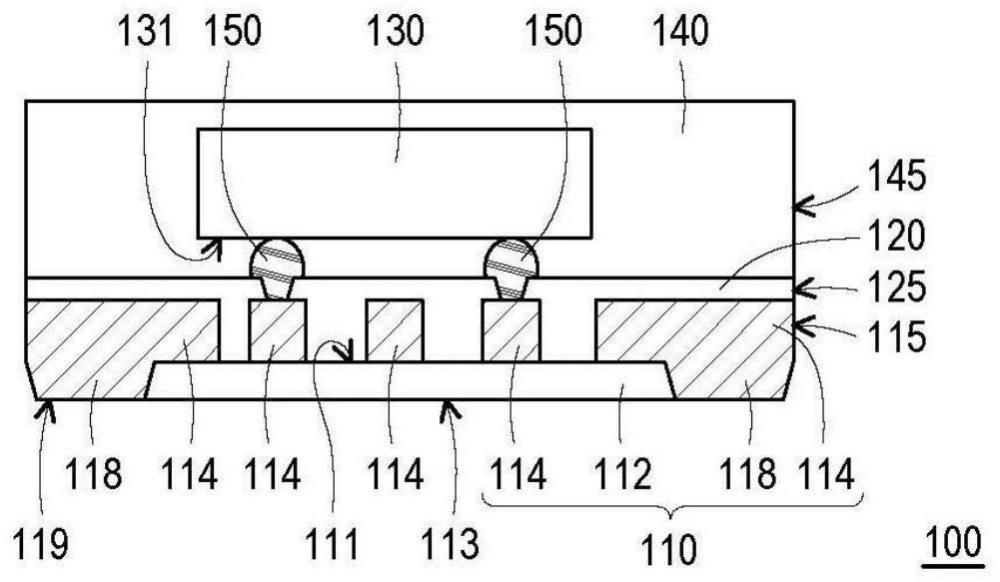

2、根据本发明的实施例,芯片封装结构包括重布线路层、芯片以及封装胶体。重布线路层包括介电层、多个重布线路以及多个导电孔。重布线路分别配置于介电层的上表面上。重布线路位于导电孔上方。导电孔贯穿介电层使引脚接垫为重布线路的一部分而组成一体成形的结构。每一导电孔内的引脚接垫的底表面微凹于介电层的下表面,其微凹度介于1.0微米至20微米之间。芯片配置于重布线路层上,且与重布线路电性连接。封装胶体配置于重布线路层上且包覆芯片。

3、在根据本发明的实施例的芯片封装结构中,上述的芯片封装结构还包括多个焊球,位于芯片的主动表面与重布线路之间。芯片通过焊球与重布线路层电性连接。

4、在根据本发明的实施例的芯片封装结构中,上述的芯片封装结构还包括保护层,配置于重布线路层以及封装胶体之间。保护层覆盖介电层与重布线路,且暴露出部分重布线路。

5、在根据本发明的实施例的芯片封装结构中,上述的封装胶体的周围表面切齐于每一重布线路的侧表面。

6、在根据本发明的实施例的芯片封装结构中,上述的第二重布线路的线宽与线距分别大于7微米且小于等于20微米。

7、根据本发明的实施例,芯片封装结构的制作方法其包括以下步骤。形成重布线路层。重布线路层包括介电层、多个重布线路以及多个导电孔。重布线路分别配置于介电层的上表面上。导电孔贯穿介电层使引脚接垫为重布线路的一部分而组成一体成形的结构。形成至少一芯片于重布线路层上。芯片与重布线路电性连接。形成封装胶体于重布线路层上。封装胶体包覆芯片。进行单体化程序,以切割封装胶体以及重布线路层,而形成至少一芯片封装结构。于芯片封装结构中,在每一导电孔的底表面微凹于介电层的下表面,其微凹度介于1.0微米至20微米之间。

8、在根据本发明的实施例的芯片封装结构的制作方法中,上述形成重布线路层的步骤,包括:提供载板。载板包括基材、不锈钢层以及金属层。不锈钢层形成于基材上且共形地覆盖基材。金属层形成于不锈钢层上且共形地覆盖不锈钢层。形成介电层于金属层上。形成多个贯穿孔以贯穿介电层。以电镀的方式形成导电孔于贯穿孔内以及形成重布线路于介电层的上表面上。

9、在根据本发明的实施例的芯片封装结构的制作方法中,上述于移除载板之前,形成保护层于重布线路层上。保护层覆盖介电层与重布线路,且暴露出部分重布线路。

10、在根据本发明的实施例的芯片封装结构的制作方法中,上述的芯片封装结构的制作方法还包括形成芯片于重布线路层上之前,配置转接板于保护层上并移除基材以及不锈钢层,而暴露出金属层。移除金属层,而暴露出每一导电孔的底表面以及介电层的下表面。将重布线路层及其上的保护层贴附于台面上。

11、在根据本发明的实施例的芯片封装结构的制作方法中,上述的芯片通过多个焊球与重布线路层电性连接。

12、基于上述,在本发明的芯片封装结构及其制作方法中,因芯片是配置于重布线路层上,其中重布线路层的在每一导电孔的底表面微凹于介电层的下表面,其微凹度介于1.0微米至20微米之间。也就是说,本发明以重布线路层来取代现有技术中的导线架,且无采用晶圆级封装程序,因此不需要昂贵的材料设备及厂房,且能降低生产成本。

技术特征:1.一种芯片封装结构,其特征在于,包括:

2.根据权利要求1所述的芯片封装结构,其特征在于,还包括:

3.根据权利要求1所述的芯片封装结构,其特征在于,还包括:

4.根据权利要求1所述的芯片封装结构,其特征在于,所述封装胶体的周围表面切齐于所述多个重布线路中的每一个的侧表面。

5.根据权利要求1所述的芯片封装结构,其特征在于,所述多个重布线路中的每一个的线宽与线距分别大于7微米且小于等于20微米。

6.一种芯片封装结构的制作方法,其特征在于,包括:

7.根据权利要求6所述的芯片封装结构的制作方法,其特征在于,形成所述重布线路层的步骤,包括:

8.根据权利要求7所述的芯片封装结构的制作方法,其特征在于,还包括:

9.根据权利要求8所述的芯片封装结构的制作方法,其特征在于,还包括:

10.根据权利要求6所述的芯片封装结构的制作方法,其特征在于,所述至少一芯片通过多个焊球与所述重布线路层的所述多个重布线路电性连接。

技术总结本发明提供一种芯片封装结构及其制作方法。芯片封装结构包括重布线路层、芯片以及封装胶体。重布线路层包括介电层、多个重布线路以及多个导电孔。重布线路分别配置于介电层的上表面上。导电孔贯穿介电层且电性连接重布线路。每一导电孔的底表面微凹于介电层的下表面,其微凹度介于1.0微米至20微米之间。芯片配置于重布线路层上,且与重布线路电性连接。封装胶体配置于重布线路层上且包覆芯片。本发明的芯片封装结构及其制作方法,其利用低成本的大型基板及其基础设施的制程,避免晶圆级封装昂贵的厂房材料设备因而能降低生产成本。技术研发人员:何崇文受保护的技术使用者:何崇文技术研发日:技术公布日:2024/11/14本文地址:https://www.jishuxx.com/zhuanli/20241118/329701.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表