半导体器件和电子器件的制作方法

- 国知局

- 2024-12-06 12:12:12

本申请涉及显示,尤其是涉及一种半导体器件和电子器件。

背景技术:

1、随着显示器件的发展,现有显示器件对薄膜晶体管的要求越来越高。低温多晶硅薄膜晶体管由于具有开关速度快、功耗低的优点被广泛应用。但在低温多晶硅薄膜晶体管的使用过程中,发现低温多晶硅薄膜晶体管会存在“驼峰”特性,导致显示器件在低灰度下出现亮度不均匀的问题。其原因在于:沿沟道宽度边缘,在栅偏置下,由于几何效应,导致沟道边缘的电场较高,更多的载流子被困在宽度边缘形成寄生晶体管,从而在边缘处出现驼峰电流,导致低温多晶硅薄膜晶体管的边缘区域相较于中间区域提前开启,造成低温多晶硅薄膜晶体管的亚阈值摆幅增加,导致像素充电不均,进而导致显示不均。

2、所以,现有显示器件存在薄膜晶体管的边缘区域相较于中间区域提前开启导致的显示不均的技术问题。

技术实现思路

1、本申请实施例提供一种半导体器件和电子器件,用以解决现有显示器件存在薄膜晶体管的边缘区域相较于中间区域提前开启导致的显示不均的技术问题。

2、本申请实施例提供一种半导体器件,该半导体器件包括:

3、衬底;

4、有源层,设置于所述衬底一侧,所述有源层包括沟道部和位于所述沟道部两侧的掺杂部;

5、栅极层,设置于所述衬底一侧;

6、栅极绝缘层,设置于所述有源层和所述栅极层之间;

7、其中,在所述有源层所在平面上具有相互垂直的第一方向和第二方向,所述沟道部指向所述掺杂部的方向为第一方向,在第二方向上,所述栅极绝缘层中位于所述沟道部的中间区域的部分的介电常数与厚度的比值,大于所述栅极绝缘层中位于所述沟道部的边缘区域的介电常数与厚度的比值。

8、在一些实施例中,在第二方向上,所述栅极绝缘层中位于所述沟道部的中间区域的部分的厚度,小于或者等于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的厚度,且所述栅极绝缘层中位于所述沟道部的中间区域的部分的介电常数,大于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的介电常数。

9、在一些实施例中,在所述第二方向上,所述栅极绝缘层中位于所述沟道部的中间区域的部分的厚度,大于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的厚度,且所述栅极绝缘层中位于所述沟道部的中间区域的部分的介电常数,大于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的介电常数。

10、在一些实施例中,所述栅极绝缘层中位于所述沟道部的中间区域的部分的材料,与所述栅极绝缘层中位于所述沟道部的边缘区域的部分的材料不同。

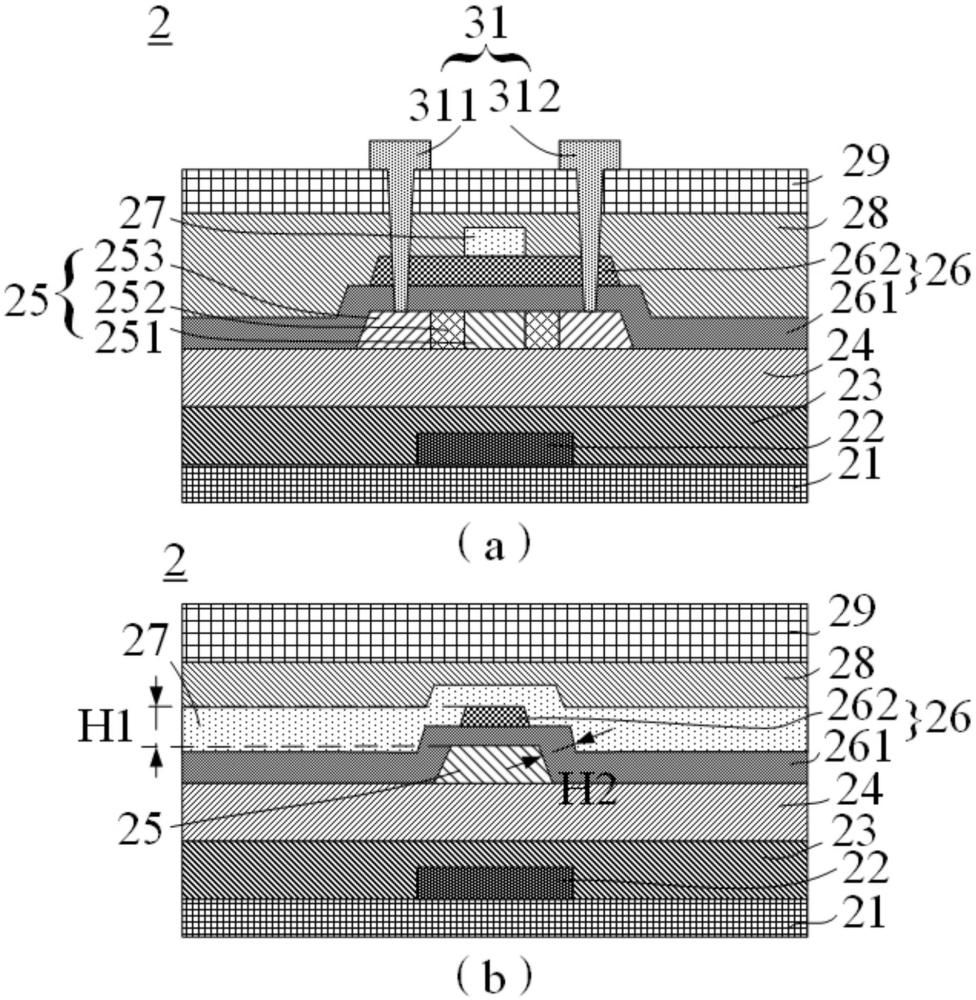

11、在一些实施例中,所述栅极层设置于所述有源层远离所述衬底的一侧,所述栅极绝缘层至少包括第一栅极绝缘层和第二栅极绝缘层,所述第二栅极绝缘层的介电常数大于所述第一栅极绝缘层的介电常数,在第二方向上,所述第二栅极绝缘层在所述衬底上的投影与所述边缘区域内的所述沟道部在所述衬底上的投影无重叠,且所述第一栅极绝缘层位于所述中间区域的部分的厚度小于所述第一栅极绝缘层位于所述边缘区域的部分的厚度。

12、在一些实施例中,所述第一栅极绝缘层设置于所述第二栅极绝缘层与所述有源层之间;或者所述第二栅极绝缘层设置于所述第一栅极绝缘层与所述有源层之间。

13、在一些实施例中,所述半导体器件还包括源漏极层,所述源漏极层包括源极和漏极,所述源极和所述漏极分别与位于所述沟道部两侧的所述掺杂部连接;其中,所述第二栅极绝缘层设置于所述源极与所述漏极的设置区域,所述源极和所述漏极分别穿过所述第二栅极绝缘层的过孔与所述掺杂部连接。

14、在一些实施例中,所述第二栅极绝缘层的图案与所述有源层的图案相同。

15、在一些实施例中,所述栅极层设置于所述有源层与所述衬底之间;或者所述栅极层设置于所述有源层远离所述衬底的一侧。

16、同时,本申请实施例提供一种电子器件,该电子器件包括如上述实施例任一所述的半导体器件。

17、有益效果:本申请提供一种半导体器件和电子器件;该半导体器件通过在第二方向上,使栅极绝缘层中位于沟道部的中间区域的部分的介电常数与厚度的比值,大于栅极绝缘层中位于所述沟道部的边缘区域的介电常数与厚度的比值,使得半导体器件中位于中间区域的栅极与沟道部的电容大于位于边缘区域的栅极与沟道部的电容,使得沟道部的中间区域可以先于沟道部的边缘区域开启,消除驼峰电流,减小半导体器件的亚阈值摆幅,提高半导体器件的性能,从而提高显示均一性。

技术特征:1.一种半导体器件,其特征在于,包括:

2.如权利要求1所述的半导体器件,其特征在于,在所述第二方向上,所述栅极绝缘层中位于所述沟道部的中间区域的部分的厚度,小于或者等于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的厚度,且所述栅极绝缘层中位于所述沟道部的中间区域的部分的介电常数,大于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的介电常数。

3.如权利要求1所述的半导体器件,其特征在于,在所述第二方向上,所述栅极绝缘层中位于所述沟道部的中间区域的部分的厚度,大于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的厚度,且所述栅极绝缘层中位于所述沟道部的中间区域的部分的介电常数,大于所述栅极绝缘层中位于所述沟道部的边缘区域的部分的介电常数。

4.如权利要求2或3所述的半导体器件,其特征在于,所述栅极绝缘层中位于所述沟道部的中间区域的部分的材料,与所述栅极绝缘层中位于所述沟道部的边缘区域的部分的材料不同。

5.如权利要求2或3所述的半导体器件,其特征在于,所述栅极绝缘层至少包括第一栅极绝缘层和第二栅极绝缘层,所述第二栅极绝缘层的介电常数大于所述第一栅极绝缘层的介电常数,在第二方向上,所述第二栅极绝缘层在所述衬底上的投影与所述边缘区域内的所述沟道部在所述衬底上的投影无重叠,且所述第一栅极绝缘层位于所述中间区域的部分的厚度小于所述第一栅极绝缘层位于所述边缘区域的部分的厚度。

6.如权利要求5所述的半导体器件,其特征在于,所述第一栅极绝缘层设置于所述第二栅极绝缘层与所述有源层之间;或者所述第二栅极绝缘层设置于所述第一栅极绝缘层与所述有源层之间。

7.如权利要求5所述的半导体器件,其特征在于,所述半导体器件还包括源漏极层,所述源漏极层包括源极和漏极,所述源极和所述漏极分别与位于所述沟道部两侧的所述掺杂部连接;其中,所述第二栅极绝缘层设置于所述源极与所述漏极的设置区域,所述源极和所述漏极分别穿过所述第二栅极绝缘层的过孔与所述掺杂部连接。

8.如权利要求5所述的半导体器件,其特征在于,所述第二栅极绝缘层的图案与所述有源层的图案相同。

9.如权利要求1所述的半导体器件,其特征在于,所述栅极层设置于所述有源层与所述衬底之间;或者所述栅极层设置于所述有源层远离所述衬底的一侧。

10.一种电子器件,其特征在于,包括如权利要求1至9任一所述的半导体器件。

技术总结本申请提供一种半导体器件和电子器件;该半导体器件通过在第二方向上,使栅极绝缘层中位于沟道部的中间区域的部分的介电常数与厚度的比值,大于栅极绝缘层中位于所述沟道部的边缘区域的介电常数与厚度的比值,使得半导体器件中位于中间区域的栅极与沟道部的电容大于位于边缘区域的栅极与沟道部的电容,使得沟道部的中间区域可以先于沟道部的边缘区域开启,消除驼峰电流,减小半导体器件的亚阈值摆幅,提高半导体器件的性能,从而提高显示均一性。技术研发人员:熊文慧,李壮,宋德伟,艾飞受保护的技术使用者:武汉华星光电技术有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/339918.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表