利用埋置绝缘层作为栅极介电质的高压晶体管的制作方法

- 国知局

- 2024-12-06 12:32:36

本披露通常涉及半导体装置及制造技术,以提供基于半导体或绝缘体上硅(silicon-on-insulator;soi)架构形成的晶体管元件。

背景技术:

1、由于场效应晶体管的关键尺寸的持续缩小,在半导体装置的领域已取得显着进步。在最近的发展中,在复杂平面装置架构中,晶体管元件的关键尺寸已达到30纳米甚至更小,从而获得极高集成密度,并因此提供在单个集成电路中集成越来越多功能的可能性。复杂场效应晶体管的关键尺寸(例如栅极长度)的持续缩小通常涉及特定的挑战,必须解决这些特定挑战以实现尺寸缩小的场效应晶体管的合适功能。复杂场效应晶体管的栅极长度的持续缩小的这些负面影响的其中一些涉及形成于栅极电极结构下方的导电沟道之间的电容耦合,其余晶体管本体相对栅极电极结构的寄生电容,从而增加进入并穿过极薄栅极介电材料的静态及动态漏电流,等等。例如,栅极电极结构至沟道区的减小的电容耦合的问题已导致栅极介电材料的物理厚度持续缩小,以增加电容耦合,另一方面,这可能显着促进进入并穿过该薄栅极介电材料的漏电流增加。因此,已开发复杂材料系统及制造技术,以向栅极介电材料中引入高k介电材料,从而使物理厚度适于保持漏电流于可接受的水平,同时进一步减小由此形成的电性厚度或氧化物等同厚度。

2、为了进一步增强高度微缩场效应晶体管的沟道区的总体可控性,在最近的开发中,通过进一步降低沟道区中的掺杂物浓度可解决在具有约30纳米及显着更小的长度的沟道区中不可避免的掺杂物波动问题,从而也降低散射事件的概率,并因此增加沟道区中载流子的总体速度。在此背景下,已意识到,全耗尽晶体管本体区(也就是沟道区以及在其附近的任意区域在施加于栅极电极结构的0v下基本不包含迁移载流子)可提供优越的晶体管性能,尤其是在总体沟道可控性方面。通过使用极薄半导体材料以在其中实施沟道区(例如极薄硅材料、硅/锗材料等),可实现全耗尽晶体管配置,从而结合此极薄半导体材料中的无或极低掺杂物浓度获得所需的全耗尽状态。

3、而且,在至少一些态样中,通过使用soi架构(也就是,在相应主动半导体材料下方形成埋置绝缘材料的架构)也可增加晶体管性能。因此,已在基于soi架构所形成的全耗尽平面晶体管元件的基础上开发复杂电路设计,其中,即使对于具有30纳米及显着更小的关键尺寸的高度复杂晶体管元件,结合较低功耗也可实现晶体管的较高开关速度。因此,甚至高度复杂的控制电路可实施于相应电路设计中,其中,由于较低功耗,甚至复杂独立装置可具有任意此类复杂电路。

4、由于平面晶体管架构中的全耗尽晶体管配置基本上用以在单个半导体芯片中实施高度复杂电路,因此相较用于小信号应用的复杂全耗尽晶体管元件,也需要操作于较高电压的晶体管元件。也就是说,这些复杂小信号晶体管通常操作于约2v甚至更小的供应电压,以减少静态及动态漏电流并因此降低功耗,从而也提供减小相应栅极介电材料的物理厚度的可能性,如上所述,即使使用复杂高k介电材料,也可能需要减小相应栅极介电材料的物理厚度来保持所需程度的沟道可控性。因此,当实施额外功能于集成电路芯片中时,例如,具有相应输出级的射频(rf)组件、电荷泵或者可能必须操作于约5v以及显着更高的电压(例如10至50v及更高)的任意其它功率装置,相应的高压晶体管必须实施于相应集成电路芯片的特定装置区域。尽管相应高压晶体管可基本上依据独立的制造策略在独立的衬底上形成并可随后转移至另一个衬底(其上承载有复杂小信号晶体管元件),但结果表明,此类制程策略仍可能显着影响总体制造成本并因此可能使此类方法不太理想。

5、在其它方法中,相应高压晶体管元件可与复杂小信号晶体管一起形成,不过,因此需要较大修改,以符合形成可靠高压晶体管的要求。例如,相应栅极电极结构的图案化可能必须基于不同的策略执行,因为除了复杂小信号晶体管与高压晶体管的不同栅极长度以外,尤其,针对高压晶体管,要求栅极介电材料的物理厚度显着增加。因此,栅极介电材料的图案化可能必须执行于两个不同的序列中,以提供复杂小信号晶体管的常用高k介电材料堆叠以及具有足够物理厚度以符合高压晶体管的电压要求的相应高压栅极介电材料,例如二氧化硅材料。因此,已作了大量努力来实施高压晶体管的全耗尽晶体管架构或者试图使用soi装置的特定架构以例如通过使用埋置绝缘材料作为栅极介电层来实施相应的高压晶体管。

6、例如,美国专利号7,939,395说明一种半导体装置,其中,可将埋置绝缘层用作栅极介电材料,其中,栅极电极形成于埋置绝缘层上方的“主动”半导体层中,且漏区与源区形成于硅衬底材料中。为此,第一接触区经形成以延伸穿过埋置二氧化硅层并连接高掺杂漏区,同时第二接触区穿过埋置绝缘层形成并连接高掺杂源区。

7、美国专利号7,745,879涉及基于soi架构的全耗尽绝缘体上硅场效应晶体管以及相应制造技术,其中,可使用薄硅层来设置包括轻掺杂区的漏区,可将该区视为漂移区,提供较大长度以允许相应电压降。而且,沟道区位于该漂移区与源区之间,且具有合适配置(也就是,具有适当尺寸设计的栅极介电材料)的栅极电极结构位于该沟道区上方并且还连接载流子复合元件。

8、美国专利号7,151,303涉及用于存储器(memory)装置的访问(access)晶体管,其在辐射或粒子诱发载流子生成方面具有优越的鲁棒性,其中,通过设置专门掺杂的栅极电极可获得全耗尽状态。也就是说,在此概念中,可使用与漏源掺杂相比具有反型掺杂的栅极电极材料,以在沟道区中获得全耗尽状态。

9、由于在soi配置中设置高压晶体管方面所投入的大量努力,结果表面,相较用以形成复杂全耗尽小信号晶体管的成熟流程,仍然可能必须实施较大修改,从而为依据已知策略形成的此类装置增加大量额外成本。

10、鉴于上述情形,本披露涉及半导体装置及制造技术,其中,可能依据全耗尽晶体管配置提供基于soi架构的场效应晶体管,同时避免或至少减轻上述问题的影响。

技术实现思路

1、下面提供本披露的简要总结,以提供本发明的一些态样的基本理解。本技术实现要素:并非详尽概述本发明。其并非意图识别本发明的关键或重要元件或划定本发明的范围。其唯一目的在于提供一些简化形式的概念,作为后面所讨论的更详细说明的前序。

2、一般来说,本披露基于以下概念:可将半导体装置的埋置绝缘层有利地用作栅极介电材料,其中,可将形成于该埋置绝缘材料下方的任意衬底或块体材料有效用作栅极电极材料。因此,在此类装置配置中,可能不再需要形成于相应半导体材料上方的“标准”栅极电极结构。

3、在本文中所披露的一些态样中,可将形成于该埋置绝缘层(其可充当栅极介电材料)上方的半导体层设置为具有适于在沟道区中获得全耗尽状态的厚度,从而提供与全耗尽晶体管配置相关联的优点,例如寄生电容减小,沟道区的优越可控性,因散射中心的数目减少而导致高载流子迁移率,当考虑晶体管长度缩小时掺杂物波动总体减少,等等。而且,通过使用极薄的初始半导体层(例如,其也可用于复杂全耗尽小信号晶体管元件),可实现关于制程技术的高度兼容性,从而导致总体制造成本降低。

4、而且,当在单个半导体芯片内结合全耗尽小信号晶体管元件形成此类全耗尽晶体管元件时,可实现总体功能性的显着增加,尤其因为该较厚的埋置绝缘材料可使栅极介电材料的物理厚度增加,其因此可允许在升高的供应电压下的任意此类晶体管元件的操作。因此,以相对全耗尽小信号晶体管的配置及流程的高兼容性,基于全耗尽晶体管架构可形成需要具有高操作电压的晶体管的相应电路部分。因此,可实现在增加的集成密度下结合增强的功能性的优越设计灵活性,因为任意此类高压晶体管元件可实施于任意所需装置区域,从而可能实现在相邻装置区域中形成小信号晶体管与高压晶体管。

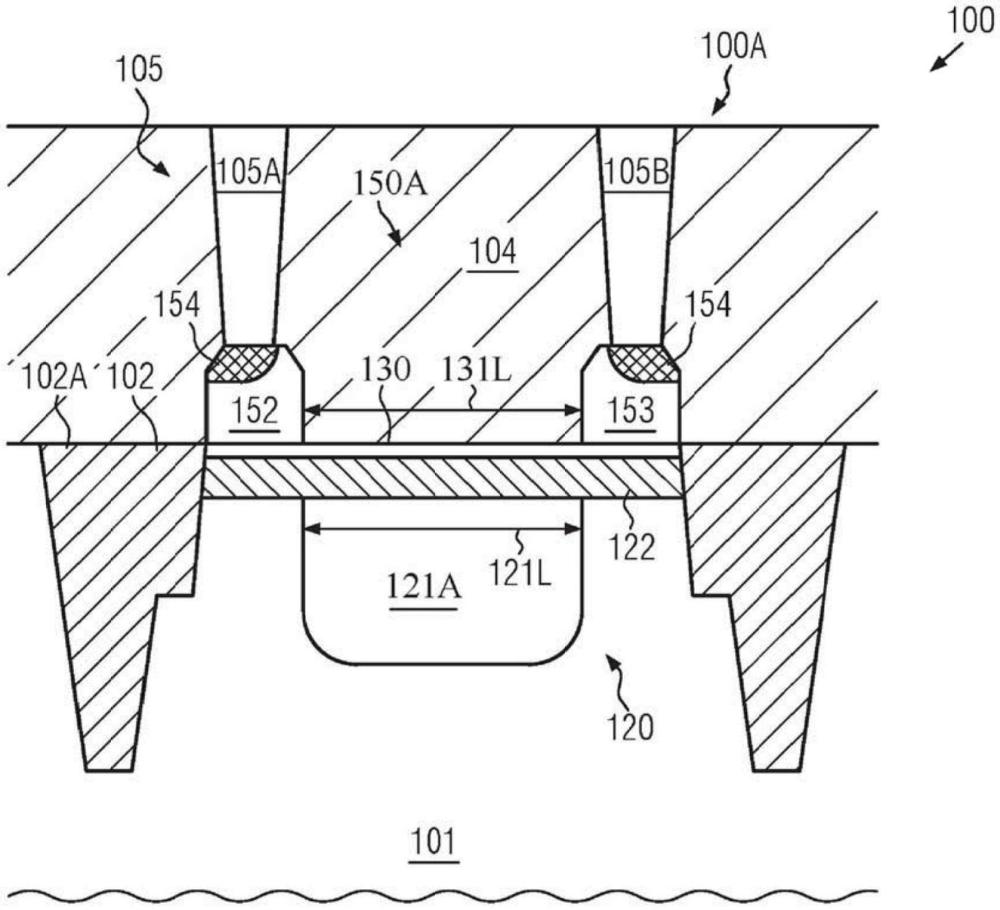

5、依据本文中所披露的一个示例实施例,一种半导体装置包括位于半导体层中的沟道区。而且,漏区与源区位于该半导体层上,以横向连接该沟道区。该半导体装置还包括埋置绝缘层,其包括位于该沟道区下方的一部分。此外,该半导体装置包括与栅极接触区连接的位于该埋置绝缘层下方的掺杂区,其中,该埋置绝缘层的该部分及该掺杂区形成晶体管元件的栅极电极结构。

6、依据本文中所披露的另一个示例实施例,一种晶体管元件包括位于漏区与源区之间的沟道区。而且,该晶体管元件包括位于至少该沟道区下方的埋置绝缘层的一部分。此外,该晶体管元件包括掺杂半导体区,其位于该埋置绝缘层的该部分下方并与控制端子连接,其中,该埋置绝缘层的该部分及该掺杂半导体区形成栅极电极结构。

7、依据本文中所披露的又一个示例实施例,提供一种方法。该方法包括通过在埋置绝缘层的一部分下方掺杂半导体衬底的衬底材料的一部分形成晶体管元件的栅极电极结构。该方法还包括在形成于该埋置绝缘层上的半导体层上形成漏区及源区。此外,该方法包括在该漏区与该源区之间形成层间介电材料。

本文地址:https://www.jishuxx.com/zhuanli/20241204/342004.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表