一种带温度补偿电路的带隙基准电压源电路

- 国知局

- 2024-07-31 23:44:40

本发明涉及模拟集成电路设计,特别是涉及一种带温度补偿电路的带隙基准电压源电路。

背景技术:

1、近年来,随着微电子技术及半导体行业的快速发展,带隙基准电压源(bandgapreference,bandgap)作为最基本的单元电路,在电源管理系统领域占据极其重要的地位。电源管理系统若要输出一个精准的电压,通常需要一个精确的参考电压。带隙基准电压源能够为低压差线性稳压器(low dropout regulator,ldo)、dc-dc开关电源等提供一个稳定的参考电压。而随着对电源管理系统更稳定、更高精度的追求,要求参考电压对工艺、温度和电源电压的依赖性越来越小,不随工艺、温度或电源电压的变化而变化,即希望带隙基准电压源能够降低温漂系数,提高电源抑制比psrr。但传统的带隙基准电路存在环路增益较低、温漂系数较高、psrr较低、输出参考电压固定为1.2v左右等劣势,不利于电源管理系统高稳定性、高精度地输出电压。

技术实现思路

1、本发明的目的是提供一种带温度补偿电路的带隙基准电压源电路,可有效提高带隙基准电压源电路的电源抑制比、降低温漂系数并且具有输出参考电压可调的特点。

2、为实现上述目的,本发明提供了如下方案:

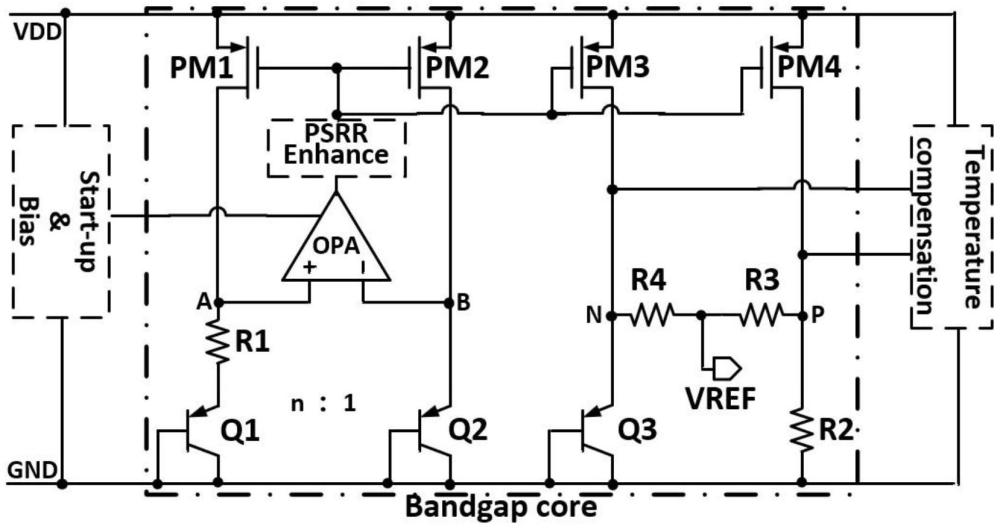

3、一种带温度补偿电路的带隙基准电压源电路,包括:启动和偏置电路、带隙基准核心电路以及温度补偿电路;

4、所述启动和偏置电路的输入端连接基准电压vref;所述启动和偏置电路的输出端输出偏置电压;所述启动和偏置电路的输出端与所述带隙基准核心电路的输入端连接;所述带隙基准核心电路的输出端用于产生ptat电压、ctat电压以及基准电压vref;所述带隙基准核心电路的输出端与所述温度补偿电路的输入端连接;所述温度补偿电路用于对带隙基准电压源电路进行温度补偿。

5、可选地,所述启动和偏置电路具体包括:pmos管pm5、pmos管pm6、nmos管nm1、nmos管nm2、pmos管pm7、pmos管pm8、nmos管nm3、nmos管nm4、nmos管nm5、nmos管nm6以及电阻r5;

6、所述pmos管pm5的源极、所述pmos管pm7的源极以及所述pmos管pm8的源极均连接电源电压vdd;所述pmos管pm5的栅极与漏极短接并连接所述pmos管pm6的源极;所述pmos管pm6的栅极和所述nmos管nm1的栅极作为所述启动和偏置电路的输入端连接基准电压vref;所述pmos管pm6的漏极以及所述nmos管nm1的漏极均与所述nmos管nm2的栅极连接;所述nmos管nm2的漏极分别与所述pmos管pm7的栅极以及所述pmos管pm8的栅极连接;所述nmos管nm2的漏极还与所述pmos管pm8的漏极连接,连接处作为所述启动和偏置电路的输出端,输出偏置电压vb1;所述nmos管nm3的栅极和漏极短接并与所述pmos管pm7的漏极连接;所述nmos管nm3的栅极还与所述nmos管nm4的栅极连接;所述nmos管nm5的栅极和漏极短接并与所述nmos管nm3的源极连接;所述nmos管nm5的栅极还与所述nmos管nm6的栅极连接;所述nmos管nm4的漏极与所述pmos管pm8的漏极连接;所述nmos管nm4的源极与所述nmos管nm6的漏极连接;所述nmos管nm6的源极与所述电阻r5的一端连接;所述nmos管nm1的源极、所述nmos管nm2的源极、所述nmos管nm5的源极以及所述电阻r5的另一端均接地。

7、可选地,所述带隙基准核心电路具体包括:运算放大器、psrr增强电路、bjt管q1、bjt管q2、pmos管pm1、pmos管pm2、电阻r1以及输出级电路;

8、所述pmos管pm1的源极以及所述pmos管pm2的源极均连接电源电压vdd;所述pmos管pm1的栅极以及所述pmos管pm2的栅极均与所述psrr增强电路的输出端out连接;所述psrr增强电路的输出端out还与所述输出级电路连接;所述输出级电路作为所述带隙基准核心电路的输出端,产生ptat电压、ctat电压以及基准电压vref;所述pmos管pm1的漏极分别与所述电阻r1的一端以及所述运算放大器的正相输入端连接;所述电阻r1的另一端与所述bjt管q1的发射极连接;所述pmos管pm2的漏极分别与所述bjt管q2的发射极以及所述运算放大器的反相输入端连接;所述运算放大器的输出端与所述psrr增强电路的输入端连接;所述运算放大器的电源端与所述偏置电路的输出端连接;所述bjt管q1的基极和集电极以及所述bjt管q2的基极和集电极均接地。

9、可选地,所述psrr增强电路具体包括:pmos管pm9以及nmos管nm7;

10、所述pmos管pm9的源极连接电源电压vdd;所述pmos管pm9的栅极和漏极短接并与所述nmos管nm7的漏极连接,连接点作为所述psrr增强电路的输出端out;所述nmos管nm7的栅极作为所述psrr增强电路的输入端与所述运算放大器的输出端连接。

11、可选地,所述输出级电路具体包括:pmos管pm3、pmos管pm4、bjt管q3、电阻r2、电阻r3以及电阻r4;

12、所述pmos管pm3的源极以及所述pmos管pm4的源极均连接电源电压vdd;所述pmos管pm3的栅极以及所述pmos管pm4的栅极作为所述输出级电路的输入端均与所述psrr增强电路的输出端out连接;所述pmos管pm3的漏极分别与所述电阻r4的一端以及所述bjt管q3的发射极连接,连接处生成ctat电压;所述电阻r4的另一端与所述电阻r3的一端连接,连接处生成基准电压vref;所述电阻r3的另一端分别与所述pmos管pm4的漏极以及所述电阻r2的一端连接,连接处生成ptat电压;所述bjt管q3的集电极和基极以及所述电阻r2的另一端均接地。

13、可选地,所述温度补偿电路具体包括:pmos管pm10、pmos管pm11、pmos管pm12、pmos管pm13、pmos管pm14、pmos管pm15、nmos管nm8、nmos管nm9、nmos管nm10以及电阻r6;

14、所述pmos管pm10的源极、所述pmos管pm11的源极、所述pmos管pm12的源极、所述pmos管pm13的源极、所述pmos管pm14的源极以及所述pmos管pm15的源极均连接电源电压vdd;所述pmos管pm10的栅极以及所述pmos管pm11的栅极作为所述温度补偿电路的输入端与所述psrr增强电路的输出端out连接;所述pmos管pm10的漏极分别与所述nmos管nm8的漏极以及所述nmos管nm10的栅极连接;所述nmos管nm8的栅极和漏极短接;所述pmos管pm11的漏极分别与所述nmos管nm9的栅极以及所述电阻r6的一端连接;所述pmos管pm12的栅极和漏极短接并与所述nmos管nm9的漏极连接;所述pmos管pm12的栅极与所述pmos管pm13的栅极连接;所述pmos管pm13的漏极作为ptat电压输入端连接所述ptat电压;所述pmos管pm14的栅极和漏极短接并与所述nmos管nm10的漏极连接;所述pmos管pm14的栅极与所述pmos管pm15的栅极连接;所述pmos管pm15的漏极作为ctat电压输入端连接所述ctat电压;所述nmos管nm8的源极、所述电阻r6的另一端、所述nmos管nm9的源极以及所述nmos管nm10的源极均接地。

15、根据本发明提供的具体实施例,本发明公开了以下技术效果:

16、本发明提供了一种带温度补偿电路的带隙基准电压源电路,是基于电压模架构进行电压调节设计的,相较于传统带隙基准电压源电路增加了温度补偿电路。该带隙基准电压源电路由启动和偏置(start-up&bias)电路、带隙基准核心(bandgap core)电路以及温度补偿(temperature compensation)电路构成,是一种可以简单有效地降低温漂系数的带隙基准电压源。因此,本发明提供的带温度补偿电路的带隙基准电压源电路可有效提高带隙基准电压源电路的电源抑制比、降低温漂系数并且具有输出参考电压可调的特点。

本文地址:https://www.jishuxx.com/zhuanli/20240730/198392.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表