半导体结构的制作方法及半导体结构与流程

- 国知局

- 2024-07-31 18:15:55

本公开涉及集成电路,特别是涉及一种半导体结构的制作方法及半导体结构。

背景技术:

1、随着半导体工艺制程的不断发展,半导体器件的关键尺寸减小,在14nm及以下制程的集成电路中,为了提升载流子迁移率,晶体管结构从平面结场效应晶体管转变为具有三维立体栅结构的鳍式场效应晶体管(fin field effective transistor,finfet)。

技术实现思路

1、基于此,本公开提供一种半导体结构的制作方法及半导体结构。

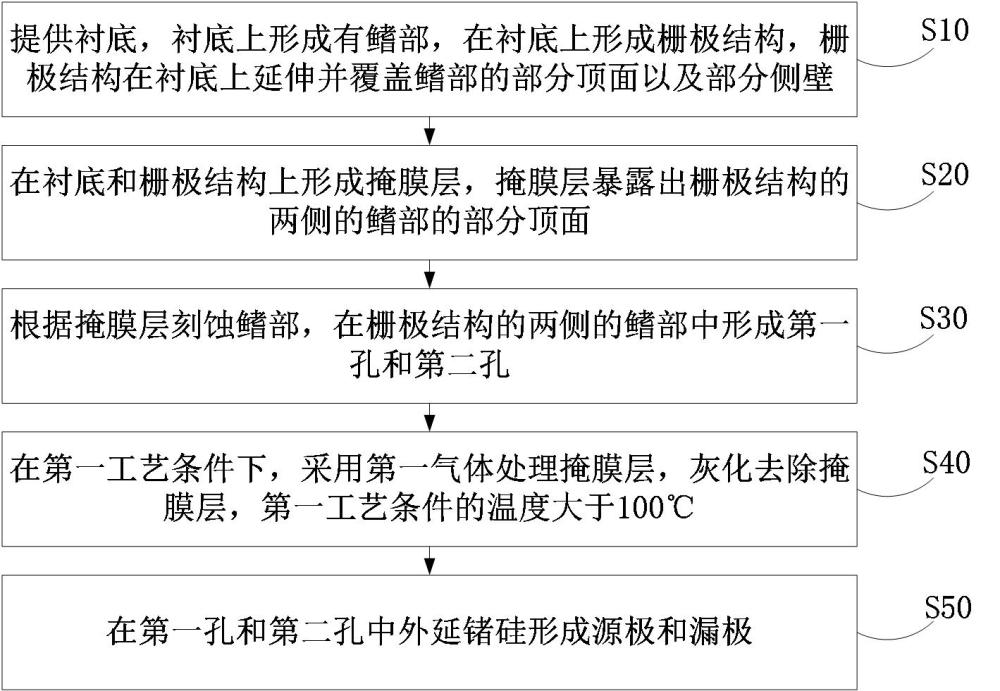

2、第一方面,本公开提供了一种半导体结构的制作方法,包括:

3、提供衬底,所述衬底上形成有鳍部,在所述衬底上形成栅极结构,所述栅极结构在所述衬底上延伸并覆盖所述鳍部的部分顶面以及部分侧壁;

4、在所述衬底和所述栅极结构上形成掩膜层,所述掩膜层暴露出所述栅极结构的两侧的所述鳍部的部分顶面;

5、根据所述掩膜层刻蚀所述鳍部,在所述栅极结构的两侧的所述鳍部中形成第一孔和第二孔;

6、在第一工艺条件下,采用第一气体处理所述掩膜层,灰化去除所述掩膜层,所述第一工艺条件的温度大于100℃;

7、在所述第一孔和所述第二孔中外延锗硅形成源极和漏极。

8、可选地,所述第一工艺条件为:

9、温度100℃-350℃;压力1mtorr-10torr;源功率10w-6000w;

10、所述第一气体包括氧气、氢气、氮气以及氨气中的至少一种。

11、可选地,灰化去除所述掩膜层之后,在所述第一孔和所述第二孔中外延形成源极和漏极之前,还包括:

12、在第二工艺条件下,采用第二气体处理所述结构,以使所述第一孔和所述第二孔暴露出的所述鳍部的表面的晶格重新排列成均匀的单晶结构;

13、湿法清洗所述第一孔和所述第二孔。

14、可选地,所述第二工艺条件为:

15、温度10℃-350℃;压力1mtorr-10torr;源功率10w-6000w;

16、所述第二气体包括氧气、氢气、氮气、氨气、溴气、四氟化碳或三氟化氮中的至少一种。

17、可选地,所述制作方法包括:

18、刻蚀所述第一孔和所述第二孔,去除所述第一孔暴露出的部分所述鳍部,增大所述第一孔的尺寸形成第三孔,去除所述第二孔暴露出的部分所述鳍部,增大所述第二孔的尺寸形成第四孔;

19、在所述第三孔和所述第四孔中外延锗硅形成源极和漏极。

20、可选地,采用各向同性刻蚀工艺刻蚀所述第一孔和所述第二孔。

21、可选地,形成所述第三孔和所述第四孔之后,在第二工艺条件下,采用第二气体处理所述结构,以使所述第三孔和所述第四孔暴露出的所述鳍部的表面的晶格重新排列成均匀的单晶结构;

22、湿法清洗所述第三孔和所述第四孔。

23、可选地,所述制作方法还包括:

24、在第三工艺条件下,采用第三气体处理所述结构,以还原所述鳍部暴露在制程空间中被氧化的部分。

25、可选地,所述第三工艺条件为:温度10℃-300℃;

26、所述第三气体包括氨气、四氟化碳或三氟化氮中的至少一种。

27、第二方面,本公开提供一种半导体结构,采用如第一方面所述的制作方法制作得到。

28、本公开的半导体结构的制作方法及半导体结构,在栅极结构的两侧鳍部中形成第一孔和第二孔之后,在大于100℃温度的第一工艺条件下灰化去除掩膜层,提高灰化去除掩膜层的效率将掩膜层全部去除,缩短灰化处理的时长,避免残留掩膜层影响后续制程,同时避免结构表面形成较厚的氧化层,能够提高半导体结构的关键尺寸的精度。

技术特征:1.一种半导体结构的制作方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制作方法,其特征在于,所述第一工艺条件为:

3.根据权利要求1所述的半导体结构的制作方法,其特征在于,灰化去除所述掩膜层之后,在所述第一孔和所述第二孔中外延形成源极和漏极之前,还包括:

4.根据权利要求3所述的半导体结构的制作方法,其特征在于,所述第二工艺条件为:

5.根据权利要求4所述的半导体结构的制作方法,其特征在于,采用各向同性刻蚀工艺刻蚀所述第一孔和所述第二孔。

6.根据权利要求1所述的半导体结构的制作方法,其特征在于,形成所述第三孔和所述第四孔之后,在第二工艺条件下,采用第二气体处理所述结构,以使所述第三孔和所述第四孔暴露出的所述鳍部的表面的晶格重新排列成均匀的单晶结构;

7.根据权利要求1所述的半导体结构的制作方法,其特征在于,所述制作方法还包括:

8.根据权利要求7所述的半导体结构的制作方法,其特征在于,所述第三工艺条件为:温度10℃-300℃;

9.一种半导体结构,其特征在于,采用如权利要求1-8中任一项所述的制作方法制作得到。

技术总结本公开涉及一种半导体结构的制作方法及半导体结构,涉及集成电路领域,方法包括:提供衬底,衬底上形成有鳍部,在衬底上形成栅极结构,栅极结构在衬底上延伸并覆盖鳍部的部分顶面以及部分侧壁;在衬底和栅极结构上形成掩膜层,掩膜层暴露出栅极结构的两侧的鳍部的部分顶面;根据掩膜层刻蚀鳍部,在栅极结构的两侧的鳍部中形成第一孔和第二孔;在第一工艺条件下,采用第一气体处理掩膜层,灰化去除掩膜层,第一工艺条件的温度大于100℃;在第一孔和第二孔中外延锗硅形成源极和漏极。通过提高灰化去除掩膜层的效率,缩短灰化处理的时长,避免残留掩膜层影响后续制程,同时避免结构表面形成较厚的氧化层,能够提高半导体结构的关键尺寸的精度。技术研发人员:王士京,王兆祥,刘伊伟,梁洁,涂乐义,王昕受保护的技术使用者:上海邦芯半导体科技有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178525.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表