半导体装置、匹配电路以及滤波器电路的制作方法

- 国知局

- 2024-07-31 18:16:36

本发明涉及半导体装置。并且,本发明涉及具备上述半导体装置的匹配电路以及滤波器电路。

背景技术:

1、作为用于半导体集成电路的代表性的电容器元件,例如已知有mim(metalinsulator metal:金属绝缘体金属)电容器。mim电容器是具有利用下部电极和上部电极夹持绝缘体的平行平板型的结构的电容器。

2、在专利文献1中公开了一种电子部件,具备:电路元件,形成于基板上;至少一对端子电极,与上述电路元件连接并且与至少一个面对置地配置;以及支承体,比上述至少一对端子电极突出地形成,并且设置于在上述至少一个面的俯视时不与上述电路元件重叠的区域。

3、在专利文献1的图1~图4中,作为电子部件的一个例子,示出了如下的电容器1:在呈平面矩形形状的基板2上依次层叠有下部电极3(电路元件)、电介质层4(电路元件)、第一电极5a(电路元件)、第一电极5b(电路元件)、第一保护层6(保护层)、第二电极7(电路元件)、第二保护层8(保护层)、端子电极9a、9b以及支承体10a、10b。

4、专利文献1:日本特开2012-15333号公报(日本专利第5445357号公报)

5、在专利文献1中记载了:作为电介质层4的膜的材料,例如使用pbtio3、pb(zr,ti)o3(pzt)、pbnb2o3、pb(mg,nb)o3(pmn)、batio3、(ba,sr)tio3(bst)、catio3、zro2、hfo2、tio2、ta2o6、bi4ti4o12、srbi2ta2o9、al2o3、si3n4、sio2等高介电陶瓷材料。

6、在将专利文献1所记载的电容器1那样的半导体装置用于匹配电路等的电容器的情况下,要求作为介电损耗的倒数的q值高。然而,对于适合于提高半导体装置的q值的电介质膜,至今还没有充分研究。

技术实现思路

1、本发明是为了解决上述的问题而完成的,其目的在于提供一种具有高的q特性的半导体装置。并且,本发明的目的在于提供具备上述半导体装置的匹配电路以及滤波器电路。

2、本发明的半导体装置具备:基板;第一电极层,设置于上述基板上;电介质膜,设置于上述第一电极层上;第二电极层,设置于上述电介质膜上;保护层,覆盖上述第一电极层及上述第二电极层;以及外部电极,贯通上述保护层,上述电介质膜由硅氧化物构成,上述电介质膜所含有的上述硅氧化物的三元环结构与四元环结构的比率为0.46以下。

3、本发明的匹配电路具备本发明的半导体装置。

4、本发明的滤波器电路具备本发明的半导体装置。

5、根据本发明,能够提供具有高的q特性的半导体装置。并且,根据本发明,能够提供具备上述半导体装置的匹配电路以及滤波器电路。

技术特征:1.一种半导体装置,其中,具备:

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1所述的半导体装置,其中,

4.根据权利要求1~3中的任意一项所述的半导体装置,其中,

5.根据权利要求4所述的半导体装置,其中,

6.根据权利要求5所述的半导体装置,其中,

7.根据权利要求5所述的半导体装置,其中,

8.根据权利要求1~7中的任意一项所述的半导体装置,其中,

9.根据权利要求1~7中的任意一项所述的半导体装置,其中,

10.一种匹配电路,其中,具备权利要求1~9中的任意一项所记载的半导体装置。

11.一种滤波器电路,其中,具备权利要求1~9中的任意一项所记载的半导体装置。

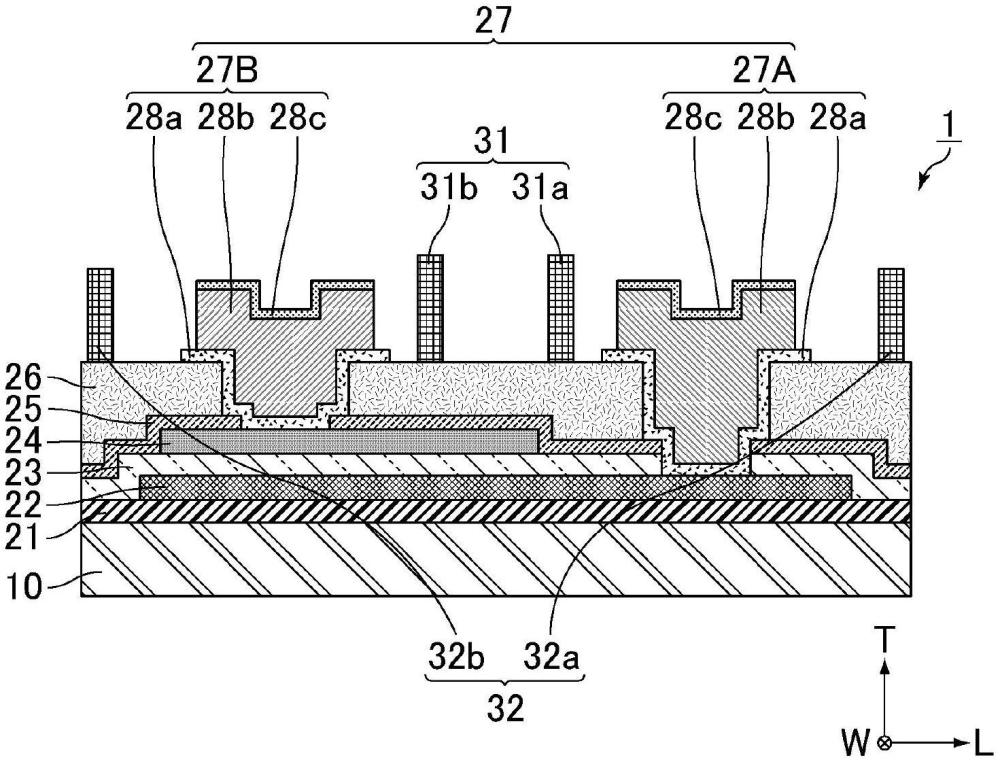

技术总结作为半导体装置的一个实施方式的电容器(1)具备:基板(10)、设置于基板(10)上的第一电极层(22)、设置于第一电极层(22)上的电介质膜(23)、设置于电介质膜(23)上的第二电极层(24)、覆盖第一电极层(22)以及第二电极层(24)的保护层(26)以及贯通保护层(26)的外部电极(27),电介质膜(23)由硅氧化物构成,电介质膜(23)所含有的硅氧化物的三元环结构与四元环结构的比率为0.46以下。技术研发人员:伊藤是清受保护的技术使用者:株式会社村田制作所技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178564.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表