半导体结构的制作方法、半导体结构以及半导体器件与流程

- 国知局

- 2024-07-31 19:02:56

本技术实施例涉及半导体领域,具体而言,涉及一种半导体结构的制作方法、半导体结构以及半导体器件。

背景技术:

1、通过向gan材料中增加in组分形成ingan材料,在室温条件下,带隙调节范围可以从3.4到0.7ev。较低带隙的半导体可以吸收更宽的光谱,有利于提高gan材料在光解水应用中的光电流密度。然而,在gan生长过程中,ingan由于熔点低,容易导致in的析出问题,导致in浓度降低,影响氮化铟材料的光吸收率。

技术实现思路

1、本技术实施例提供了一种半导体结构的制作方法、半导体结构以及半导体器件,以至少解决相关技术中氮化铟材料的光吸收率较低的问题。

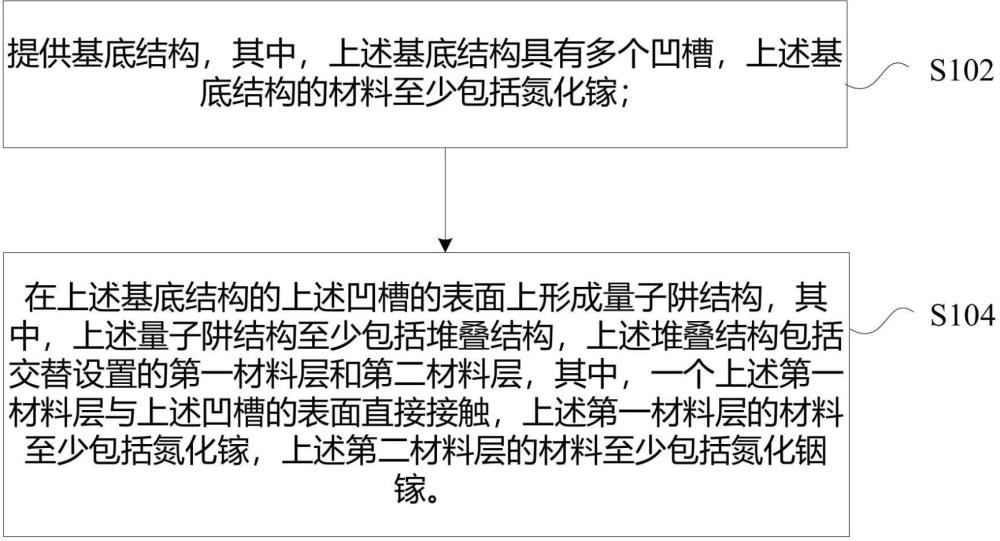

2、根据本技术的一个实施例,提供了一种半导体结构的制作方法,包括:提供基底结构,其中,所述基底结构具有多个凹槽,所述基底结构的材料至少包括氮化镓;在所述基底结构的所述凹槽的表面上形成量子阱结构,其中,所述量子阱结构至少包括堆叠结构,所述堆叠结构包括交替设置的第一材料层和第二材料层,其中,一个所述第一材料层与所述凹槽的表面直接接触,所述第一材料层的材料至少包括氮化镓,所述第二材料层的材料至少包括氮化铟镓。

3、在一个示例性实施例中,提供基底结构,包括:提供衬底,其中,所述衬底的材料至少包括氮化镓;在所述衬底的表面上形成氧化层;在所述氧化层远离所述衬底的表面上形成掩膜层;去除部分所述掩膜层、部分所述氧化层以及部分所述衬底,以使所述衬底的部分表面裸露,形成所述基底结构。

4、再一个示例性实施例中,提供衬底,包括:提供基底层,其中,所述基底层的材料至少包括蓝宝石;在所述基底层的表面上形成形核层,其中,所述形核层的材料至少包括氮化镓;在所述形核层远离所述基底层的表面上形成第一外延层,其中,所述第一外延层的材料至少包括氮化镓。

5、又一个示例性实施例中,在所述提供基底层之后,在所述基底层的表面上形成形核层之前,所述方法还包括:在第一预定温度条件下,采用第一预定气体对所述基底层进行清洗,并持续预定时间段。

6、另一个示例性实施例中,所述第一预定温度的范围为1000℃~1200℃,所述第一预定气体至少包括氢气,所述预定时间段为8~15min。

7、再一个示例性实施例中,所述在所述基底层的表面上形成形核层,包括:在第二预定温度条件下向所述基底层所在的腔室通入第二预定气体,得到所述形核层。

8、另一个示例性实施例中,所述第二预定温度的范围为500℃~550℃,所述第二预定气体至少包括三甲基镓和氨气,所述形核层的厚度范围为25~35nm。

9、又一个示例性实施例中,在所述形核层远离所述基底层的表面上形成第一外延层,包括:在第三预定温度条件下,在所述形核层远离所述基底层的表面上形成第一子外延层,其中,所述第一子外延层的材料至少包括氮化镓且所述第一子外延层为非掺杂材料层;在第四预定温度条件下,在所述第一子外延层远离所述形核层的表面上形成第二子外延层,其中,所述第四预定温度小于所述第三预定温度,所述第二子外延层的材料至少包括氮化镓和掺杂材料,所述第二子外延层的厚度大于所述第一子外延层的厚度,所述第一子外延层和所述第二子外延层形成所述第一外延层。

10、再一个示例性实施例中,所述第三预定温度的范围为1000~1100℃,所述第一子外延层的厚度范围为0.5~1.5μm,所述第四预定温度的范围为1000~1100℃,所述第二子外延层的厚度范围为1.5~2.5μm,所述第二子外延层的掺杂浓度范围为2.5~3.5×1018cm−3。

11、另一个示例性实施例中,所述在所述衬底的表面上形成氧化层,包括:在第五预定温度和预定压力条件下,向所述衬底所在的腔室通入第三预定气体,形成所述氧化层,其中,所述氧化层的材料至少包括二氧化硅。

12、又一个示例性实施例中,所述第五预定温度的范围为150~250℃,所述预定压力的范围为900~1100pa,所述第三预定气体至少包括硅源气体和氧化气体,所述氧化层的厚度的范围为150~250nm。

13、再一个示例性实施例中,所述去除部分所述掩膜层、部分所述氧化层以及部分所述衬底,包括:去除部分所述掩膜层以使所述氧化层的部分表面裸露,形成预备基底,其中,剩余的所述掩膜层形成掩膜部,所述掩膜层的材料至少包括阳极氧化铝;向所述预备基底所在的腔室通入第四预定气体,并以所述掩膜部作为掩膜刻蚀所述氧化层和所述衬底,以去除部分所述氧化层和部分所述衬底并使得部分所述衬底裸露。

14、又一个示例性实施例中,所述第四预定气体至少包括氯气和三氯化硼。

15、另一个示例性实施例中,在所述基底结构的所述凹槽的表面上形成量子阱结构,包括:在所述基底结构的所述凹槽的表面上形成第二外延层,其中,所述第二外延层的材料至少包括氮化镓;在所述第二外延层远离所述基底结构的表面上形成所述堆叠结构;在所述堆叠结构远离所述第二外延层的表面上形成第三外延层,所述第三外延层的材料至少包括氮化镓,所述第二外延层、所述堆叠结构以及所述第三外延层形成所述量子阱结构。

16、再一个示例性实施例中,所述在所述基底结构的所述凹槽的表面上形成第二外延层,包括:在第六预定温度条件下,向所述基底结构所在的腔室通入第五预定气体,形成所述第二外延层。

17、另一个示例性实施例中,所述第六预定温度的范围为1000~1100℃,所述第五预定气体至少包括三甲基镓、氨气以及氮气,所述第二外延层的厚度范围为1.5~2.5μm。

18、又一个示例性实施例中,所述在所述第二外延层远离所述基底结构的表面上形成所述堆叠结构,包括:第一形成步骤,向所述第二外延层所在的腔室通入第六预定气体,形成所述第一材料层;第二形成步骤,向所述第一材料层所在的腔室通入所述第六预定气体,形成所述第二材料层,其中,所述第二形成步骤中的所述第六预定气体的气体流量与所述第一形成步骤中的所述第六预定气体的气体流量不同,所述第二材料层的厚度大于所述第一材料层的厚度;依次重复所述第一形成步骤和所述第二形成步骤至少一次,直到达到预定次数,形成所述堆叠结构。

19、再一个示例性实施例中,所述第六预定气体至少包括三甲基铟,所述第一材料层的厚度范围为4~6nm,所述第二材料层的厚度范围为6~8nm。

20、又一个示例性实施例中,在所述堆叠结构远离所述第二外延层的表面上形成第三外延层,包括:向所述堆叠结构所在的腔室通入第七预定气体,形成所述第三外延层。

21、另一个示例性实施例中,所述第七预定气体至少包括二茂镁、三甲基镓、氨气以及氮气,所述第三外延层的厚度范围为30~60nm。

22、根据本技术的另一个实施例,提供了一种半导体结构,包括:基底结构,其中,所述基底结构具有多个凹槽;量子阱结构,位于所述凹槽内,所述量子阱结构至少包括堆叠结构,所述堆叠结构包括交替设置的第一材料层和第二材料层,其中,一个所述第一材料层与所述凹槽的表面直接接触,所述第一材料层的材料至少包括氮化镓,所述第二材料层的材料至少包括氮化铟镓。

23、又一个示例性实施例中,所述基底结构包括:衬底,其中,所述衬底的材料至少包括氮化镓;氧化层,位于所述衬底一侧的表面上;掩膜部,位于所述氧化层远离所述衬底的表面上,相邻的两个所述掩膜部形成所述凹槽。

24、再一个示例性实施例中,所述衬底包括:基底层,其中,所述基底层的材料至少包括蓝宝石;形核层,位于所述基底层一侧的表面上,所述形核层的材料至少包括氮化镓;第一外延层,位于所述形核层远离所述基底层的表面上,其中,所述第一外延层的材料至少包括氮化镓。

25、另一个示例性实施例中,所述量子阱结构包括:第二外延层,位于所述基底结构的所述凹槽的表面上,其中,所述第二外延层的材料至少包括氮化镓;堆叠结构,位于所述第二外延层远离所述基底结构的表面上;第三外延层,位于所述堆叠结构远离所述第二外延层的表面上,所述第三外延层的材料至少包括氮化镓。

26、根据本技术的又一个实施例,还提供了一种半导体器件,包括:任意一种所述的半导体结构的制作方法制作得到的半导体结构或者任意一种所述的半导体结构。

27、通过本技术,由于非极性面或者半极性面可以有效地缓解在氮化镓薄膜上外延氮化铟镓的压电极化应力,而相比于非凹槽结构,在凹槽结构内氮化镓更容易优先生长非极性面或者半极性面,所以在凹槽内生长出的氮化铟镓材料的应力小,氮化铟镓中的铟不容易析出,进而提高氮化铟镓中铟的浓度,实现提高氮化镓材料的光吸收率。因此,可以解决现有技术中氮化镓材料的光吸收率较低的问题。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181480.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。